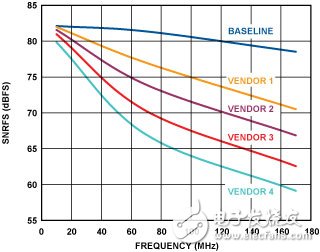

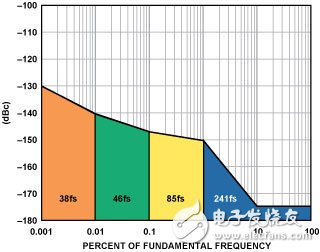

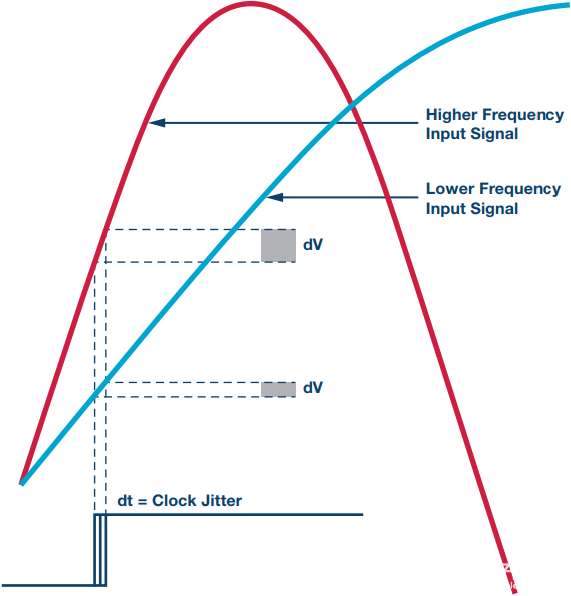

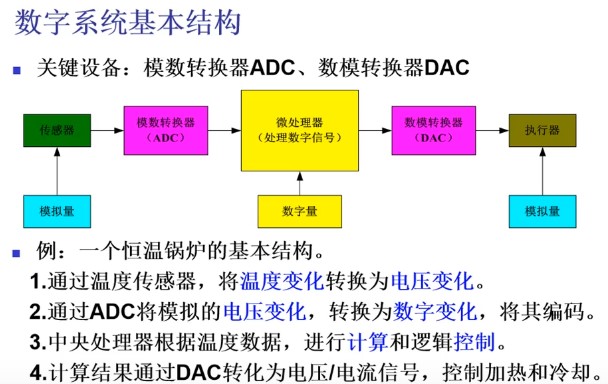

因此,使抖动最小意味着提高时钟边沿的摆率。一种实现方法是改进时钟源。图8在模拟输入频率范围上比较了用作ADI最高性能ADC(16 bit 80 MSPS AD9446)时钟源的多个不同的商用振荡器。

图8. 振荡器的选择影响AD9446-80的性能。

典型地,通用高性能时钟振荡器用于评估Analog Devices ADC实现的基线性能(蓝色线)。并非所有该高速转换器的用户均能够承受高性能温控低抖动振荡器所需的成本和空间,但是有些低成本振荡器即使在较高的模拟输入频率下也能够获得可接受的性能。图8示出了一些成本可接受的器件的性能。

重要的是,由于振荡器的销售商不会使用相同的方法描述或测量抖动,因此在选择商用振荡器时应格外注意。确定哪种振荡器最适用于具体应用的实用方法是,直接在系统中使用数种振荡器并对其进行测试。这可以对性能进行预测(假设振荡器销售商保持合理的质量控制标准)。更好的方法是联系振荡器的制造商以获得抖动或相位噪声数据,并且获得有关如何最佳地连接该器件的建议。不正确地连接振荡器可能会使转换器的无杂散动态范围(SFDR)恶化。

进一步的改进

如果价格和性能双优的振荡器仍不足以满足要求,可以考虑使用分频和/或滤波。式4描述了正弦波振荡器的输出:

两个参数将影响摆率,即信号频率(f)和幅度(A)。任一参数的增加都将使摆率增加并且将系统时钟抖动减少到更加理想的数值。通常增加时钟频率更加容易,我们可以使用时钟分配电路产生所需的转换器时钟速率,并且将其馈送到系统时钟树的其他部分。

分频器在电路元件和电源需求方面将增加成本,并且还将增加抖动。添加到时钟信号链路的每个有源元件都将增加总抖动。

在使用分频器时,必须考虑所有相关的参数。ADI的典型分频器产品是AD951x系列,仅使抖动增加约250 fs。除了内建的分频功能以外,AD951x还拥有诸如时钟分配和占空比控制的功能。

值得注意的是,尽管时钟分频器增加了总的抖动,但是由于其使频率降低,因此它们的输出抖动在输出周期中仅占很少的部分,并且引入更小的误差。例如,如果链路中100 MHz的时钟源和其他部件贡献了800 fs的抖动(约为10 ns周期的12.5%),如果时钟分频器将频率降低到10 MHz,此时分频器引入250 fs的抖动,所得到的总抖动为840 fs,小于100 ns输出周期的1%。

由式5可看出,最大的抖动贡献者确定总抖动,因此时钟源的最大抖动不应超过最大抖动贡献者的三分之一,但是没有必要比其少很多。实际的选择取决于应用的性能要求,诸如给定频率范围上的SNR、所使用的系统元件的特性以及尺寸和成本的限制。

减少相位噪声

如式5指出的,总抖动是来自时钟电路的抖动以及时钟源和其他插入元件抖动的平方和的平方根(RSS)。因此,如果分频器电路由噪声特别大的时钟源驱动,由于式5主要由最大的抖动项确定,因此分频器电路的作用不会体现出来。在该情况下,可以考虑在时钟源和分频电路之间使用无源窄带滤波器。

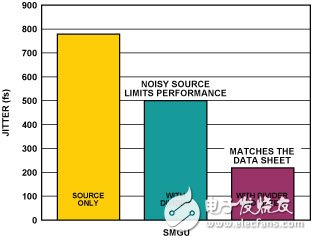

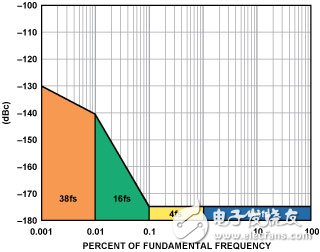

为了说明滤波的优点,考虑具有800 fs抖动的时钟源。如果时钟分频电路放置在时钟源和转换器之间,即使分频电路性能很好,抖动也仅能减少到约500 fs。但如果在时钟源和分频电路之间放置5% LC带通滤波器,就可以将抖动减少到250 fs(参看图9)。

图9. 利用时钟分频和滤波减少抖动

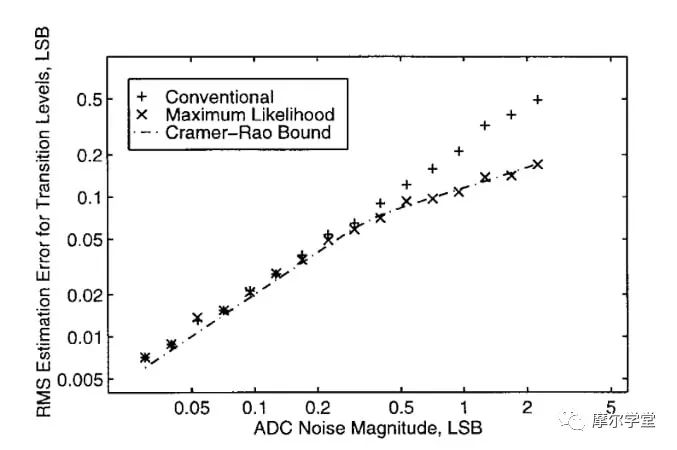

为了理解滤波器如何改善正弦时钟源的抖动,可以在频域中来探讨抖动并利用相位噪声图估计抖动值。尽管计算过程是简单的,并且提供了很好的比较方法,但是其并未考虑诸如摆率的非线性因素。因此,该模型所预测的抖动常常比实际抖动大。

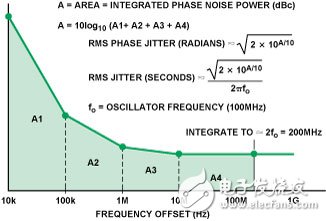

如图10所示,将相位噪声图划分为数个频率区域,并且对每个区域的噪声功率进行积分。这可以确定每个区域贡献的抖动以及时钟源的总抖动(通过RSS求和)。这些公式中,f0是载波频率。由于图10中的相噪图为两个边带之一,因此总体相位噪声应乘以2的平方根 。

图10. 利用相位噪声计算抖动

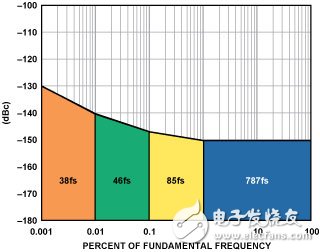

考虑具有800 fs抖动的时钟源。绘制该时钟源的相位噪声图(图11),这样可以容易地确定大的抖动来自频域中哪个位置。在800 fs抖动的时钟源的情况中,可以看到频谱中抖动的主要部分位于宽带。因此,采样系统中减少宽带噪声是极为重要的。

图11a. 800 fs时钟源的相位噪声图线

图11b. 使用具有5%通带的带通LC多极点滤波器的800 fs时钟源的相位噪声

在时钟源的输出端处使用简单的具有5%通带(5% LCBP)的带通LC多极点滤波器,可以极大地改善性能,如图11b中所示。应当注意,抖动性能从800 fs改善为小于300 fs。这对应于超过12 dB SNR的改善。

5% LCBP滤波器是易于实现的,但是体积较大并且比较昂贵。替代方案是使用晶体型滤波器。图12示出了相位噪声从800 fs改善为小于100 fs。与5% LCBP滤波器12dB SNR的改善相比,又增加了3dB,达到了15dB。

图12. 使用晶体滤波器的800 fs时钟源的相位噪声

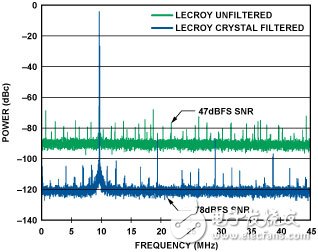

为了证实将晶体滤波器与噪声源级联的效果,进行一个实验,使用benchtop脉冲发生器为16 bit 100 MHz ADC AD9446-100提供时钟。在未进行滤波的情况下,发生器呈现出大于4 ps的抖动,导致SNR下降超过30 dB。在使用晶体滤波器的情况下,得到的抖动接近50 fs,改善后的 SNR接近于威廉希尔官方网站 资料中的SNR典型值。

图13. 晶体滤波器是有帮助的-即使存在噪声源

晶体滤波器利用其非常窄的通带区域(通常小于1%)可以将来自许多源的抖动减少到小于100 fs,但是它们也增加了成本,而其体积也大于有源滤波器。还应当注意,晶体滤波器具有5 dBm~10dBm的有限的输入/输出范围。超过该范围将导致失真,可能使ADC的SFDR下降。最后,某些晶体滤波器可能需要外部元件用于阻抗匹配。滤波器确实可以发挥作用,但是它们需要额外的元件、严格的匹配和额外的成本。

电子发烧友App

电子发烧友App

评论