系统时钟优化可以提升系统的性能,但也颇具挑战性。为模数转换器设计抖动为350飞秒(fs)的编码电路是相对容易的,但这是否能够满足当今的高速需求?例如,测试AD9446-100(16 bit 100 MHz ADC)时,在Nyquist区使用100 MHz的采样时钟频率,350 fs的抖动将使信噪比(SNR)下降约3 dB。如果在第三Nyquist域中使用105 MHz的interwetten与威廉的赔率体系 输入信号测试相同的设备,SNR下降可达10 dB。为了将时钟抖动减少到100 fs或更少,设计者需要理解时钟抖动来自哪里,以及ADC能够允许多大的抖动。如果在电路设计完成后才发现时钟电路性能受抖动的限制,并且在设计阶段中本可以很容易地避免该问题发生,这时已经太晚了。

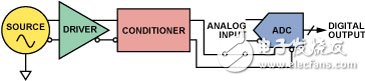

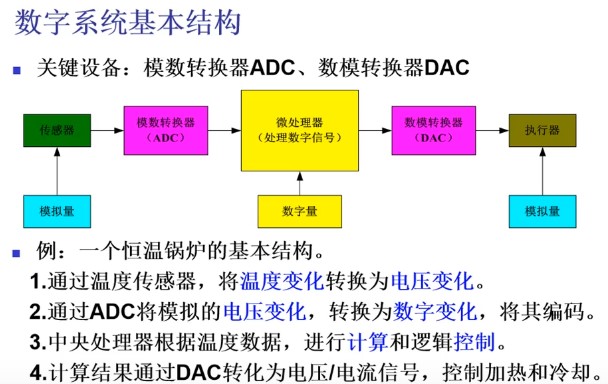

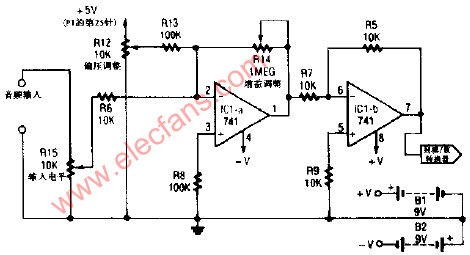

在这里我们将讨论相关的时钟参数和方法以实现高速转换器预期的性能,为此要用到一些威廉希尔官方网站 诀窍和经验。首先从典型的ADC时钟方案开始,如图1中所示,我们将焦点放在信号链路中每一级的可用于优化时钟的威廉希尔官方网站 ,并且指明一些应避免使用的常用威廉希尔官方网站 。

图1. 典型的时钟信号链路

什么是抖动?

抖动是系统时钟电路设计中最重要的参数,因此了解某些基础知识并且理解术语的含义是十分重要的。许多威廉希尔官方网站

文献描述了关于抖动的十分精确的数学模型,但是设计性能优良的转换器并非全部取决于精确的抖动描述。设计人员必须理解抖动如何进入系统以及如何使抖动的影响最小。

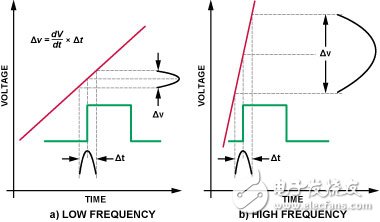

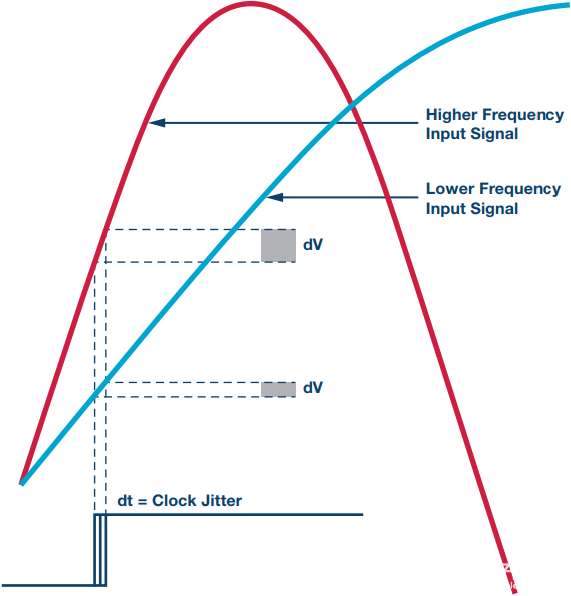

抖动是时钟边沿的位置变化,这将产生定时误差,直接导致转换幅度精度的误差(图2a)。模拟输入频率的增加导致输入信号的斜率增加,这将使转换误差放大(图2b)。应当注意,转换误差的度量是相对的,10 bit器件0.5 LSB(最低有效位)的转换误差等效于16 bit器件32 LSB的误差。这意味着随着ADC分辨率和模拟输入频率的增加,抖动变得更加引人注意。

图2. 转换误差是时钟抖动和模拟输入频率的函数

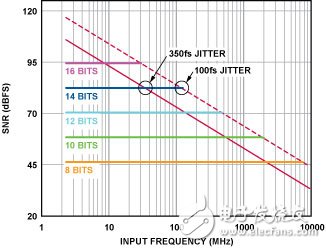

直观上看,它们之间的关系是非常明显的,因此工程师可以通过分析ADC性能和编码时钟抖动之间的关系,最终确定可接受的抖动量。式1定义了理想ADC(具有无穷大分辨率)SNR(dB)与频率的关系,而式2定义了N(10、12、14或16)bit理想ADC的SNR(dB)。

参看图3的斜线

参看图3的水平线

图3是由这两个公式画出的曲线图。用户可以在曲线交点处确定给定模拟输入信号频率时可容忍的总时钟抖动量。在低频下,精度受到转换器分辨率的限制。然而,随着输入信号频率的增加,在大于某个频点之后,ADC的性能将受控于系统的总时钟抖动。位于该频点左侧的输入信号频率,无须考虑小抖动的问题。

图3. 理想ADC的SNR vs. 模拟输入信号频率和抖动

然而,如果信号频率在该频点附近或者在其右侧,则必须降低频率或分辨率,或者必须提高抖动指标。因此,抖动越大,SNR性能受控于时钟系统抖动的频点就越低。

例如,如果使用具有350 fs抖动的时钟测试14 bit ADC,为了避免性能下降,输入信号频率必须低于35 MHz(14 bit水平线与350 fs斜线的交点)。如果抖动为100 fs,则输入信号频率可以达到125 MHz。

实际上,当模拟测试频率接近交点时,使用该一阶近似的简化模型便丧失了有效性。为了全面地理解时钟抖动对ADC性能的影响,除了分辨率以外,还要考虑量化噪声和模拟输入幅度(式3,基于参考文献9)。

其中

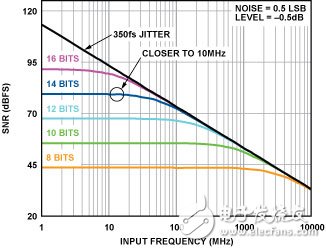

例如,假设ADC具有0.5 LSB的量化噪声,并且在测试时模拟输入幅度比满刻度低0.5 dB。图4结合了式2和式3,相比于简化模型,编码时钟抖动将在更低的频率处影响SNR性能。

图4. SNR是模拟输入频率、时钟抖动和量化噪声的函数

前面的示例中,模拟输入信号频率接近35 MHz时,具有350 fs抖动的时钟不会影响14 bit ADC的SNR。但是在考虑量化噪声、输入信号频率和输入幅度的影响后,10 MHz的信号频率就应被注意。同样地,抖动为100 fs的时钟会在低于100 MHz的频率下引起SNR的下降。

消除抖动

在回顾有关抖动的基础知识之后,我们将考虑抖动的源。能够使得ADC时钟沿变换的任何因素都将引入或影响抖动。这些因素包括串扰、EMI(电磁干扰)、地效应和电源噪声。

串扰引起的抖动可以出现在任意两条相邻的走线上。如果一条走线承载信号,而附近的平行走线承载变化的电流,则信号走线中会感生电压。如果该信号是时钟信号,则时钟边沿发生点的时刻将发生变化。

EMI辐射引发敏感信号走线上的抖动。EMI由开关电源、高压输电线、RF信号和其他类似的源产生。与串扰类似,EMI通过电磁耦合调整了信号或时钟的时序。

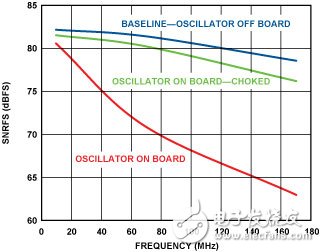

图5说明了电磁干扰对SNR的影响。蓝色曲线表示AD9446基线SNR vs. 频率的关系,其中AD9446使用外部时钟和线性电源。时钟未以任何方式连接到评估板。红色曲线给出了将相同的时钟电路固定或焊接到评估板后出现的性能下降,其中时钟电路由开关电源供电。绿色曲线给出了,如果对电源噪声进行滤波,则可以显著改善转换器的性能。

图5. 转换器性能 vs. 振荡器电源配置和频率

由开关电流或者不适当的接地引起的地弹也可能带来抖动。当许多门电路同时切换时,开关电流会变大。这可能在电源平面和地平面上产生电流尖峰,使时钟电路的阈值电压或模拟输入信号的电平移位。例如:

考虑PCB走线和接收门电路的输入端,门电路输出会具有10 pF的负载。当门电路切换时,10 mA的动态电流流入或流出每个输出端。[10 mA得自10 pF×1 V/ns,即CMOS门电路的典型摆率(I=C dV/dt)。] 因此,如果12个门电路同时切换,则动态电流可能累积达到120 mA。这将需要电源引脚提供很大的电流尖峰,而其中一个引脚是接地的。由引线电阻引起的瞬时压降(跳动)将影响所有以该引线作为参考地的电路。

为了减少这些源引起的抖动,应使用良好的布线和适当的电路布局。重要的一点是将模拟电路和数字电路限制在其各自的区域中。为确保良好的隔离,每个电路层都应遵循该原则。理解回流如何相对于源来流动以及如何避免模拟和数字电路之间的越界或交叉是十分重要的。总而言之,必须使敏感的模拟输入和时钟走线远离其他电路和走线,以免受到这些电路和走线的影响。

改善抖动意味着改善摆率

前面已讨论了抖动的基础知识及其可能带来的影响,现在的问题是:如何改进系统时钟或时钟电路以减少抖动?

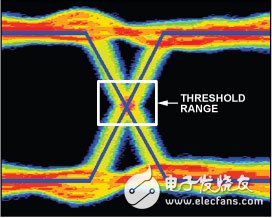

回顾之前的讨论,当抖动出现在转换过程或者时钟的阈值周期中时,抖动或噪声仅能破坏ADC的时序,如图6中所示。通过增加摆率使该边沿(并且因此使阈值周期)更快,将会使阈值周期中可能出现噪声的时间量变小,并使引入系统中的rms(均方根)抖动量变小。

图6. 差分时钟的阈值/转换区域的放大示图

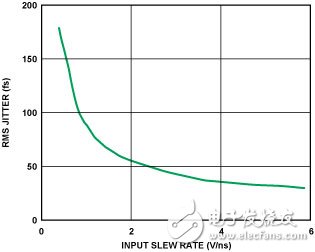

应当注意,摆率的增加不会影响原始信号质量,仅会影响通过阈值区域的转换时间。为了证实这一点,参考图2b。应当注意,信号摆动越快,在转换区域中花费的时间就越少。图7说明了抖动和摆率之间成反比。与前面的示例结合考虑,对于12 bit ADC,输入信号为70 MHz时抖动最少为100 fs rms,对应摆率为1V/ns。

图7. RMS抖动 vs. 摆率

电子发烧友App

电子发烧友App

评论