寄生电容,什么是寄生电容

电容,我们在日常生活、工作中都经常用到,但不知道大家对“寄生电容”是否知道呢?本文收集整理了一些资料,希望本文能对各位读者有比较大的参考价值。

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。在计算中我们要考虑进去。ESL就是等效电感,ESR就是等效电阻。不管是电阻,电容,电感,还是二极管,三极管,MOS管,还有IC,在高频的情况下我们都要考虑到它们的等效电容值,电感值。

寄生的含义就是本来没有在那个地方设计电容,但由于布线构之间总是有互容,互感就好像是寄生在布线之间的一样,所以叫寄生电容。

电容器与电感器都不是理想器件。一个电容器会有一定量的串联电感(称为寄生电感)。寄生电感由电容器中的导体(特别是引线)产生。老式电容器,如20世纪60年代以前就开始使用的蜡纸介质电容器件中,串联电感很大。由于电感是与电容串联的,所以构成了一个串联谐振电路。

在单片机电路设计中,晶振电路中的电容C1和C2典型值通常为30PF左右。对外接电容的值虽然没有严格的要求,但电容的大小会影响振荡频率的高低,振荡器的稳定性和起振的快速性。晶振的振荡频率的范围通常在1.2MHZ到12MHZ之间。但反过来运行速度快对存储器的速度要求就搞,对印制电路板的工艺高球也搞,即要求线间的寄生电容也要小,晶振和电容应尽可能安装得与单片机芯片靠近,,以减少寄生电容。

如何消除寄生电容的影响

消除寄生电容的方法有:

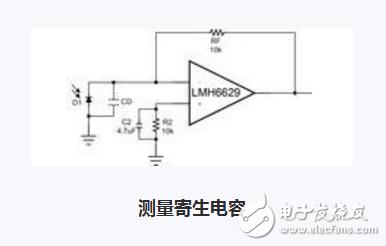

1、增加初始电容值法。采用增加初始电容值的方法可以使寄生电容相对电容传感器的电容量减小。由公式C0 = ![]()

可知,采用减小极片或极筒间的间距d0 ,如平板式间距可减小为0.2 毫米,圆筒式间距可减小为0.15毫米;或在两电极之间覆盖一层玻璃介质,用以提高相对介电常数,通过实验发现传感器的初始电容量C0不仅显著提高了,同时也防止了过载时两电极之间的短路; 另外,增加工作面积A或工作长度也可增加初始电容值C0。不过,这种方法要受到加工工艺和装配工艺、精度、示值范围、击穿电压等的限制, 一般电容的变化值在10-3~103pF之间。

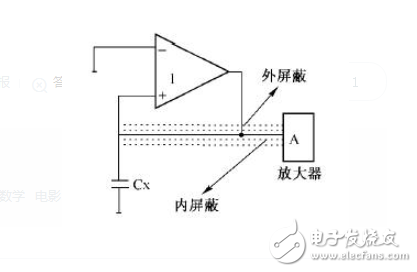

2、采用“驱动电缆”威廉希尔官方网站 ,减小寄生电容。如图1所示:在压电传感器和放大器A 之间采用双层屏蔽电缆,并接入增益为1 的驱动放大器,这种接法可使得内屏蔽与芯线等电位,进而消除了芯线对内屏蔽的容性漏电,克服了寄生电容的影响,而内外层之间的电容Cx 变成了驱动放大器的负载,电容传感器由于受几何尺寸的限制,其容量都是很小的,一般仅几个pF到几十pF。因C太小,故容抗XC=1/ωc很大,为高阻抗元件;所以,驱动放大器可以看成是一个输入阻抗很高,且具有容性负载,放大倍数为1 的同相放大器。

在线路中所有的引线间都是有电容。和线路中有电感。所以要尽量的减少引线距离。和集中接地。可以减少很多寄生电容;电感!