电子发烧友网站提供《完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表.pdf》资料免费下载

2024-03-13 13:58:12 0

0 电子发烧友网站提供《适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表.pdf》资料免费下载

2024-03-13 13:53:03 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0 DDR5内存相对于DDR4有更高的内部时钟速度和数据传输速率,从而提供更高的带宽。DDR5的传输速率可以达到6400MT/s以上,比DDR4的最高传输速率提高了一倍以上。

2024-03-12 11:23:34 118

118 DDR6和DDR5内存的区别有多大?怎么选择更好? DDR6和DDR5是两种不同的内存威廉希尔官方网站

,它们各自在性能、功耗、带宽等方面都有不同的特点。下面将详细比较这两种内存威廉希尔官方网站

,以帮助你选择更适合

2024-01-12 16:43:05 2849

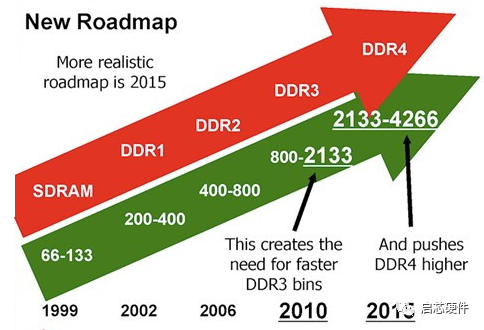

2849 DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 463

463

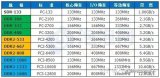

时钟频率:可通过倍频威廉希尔官方网站

升级的核心频率。时钟频率可以理解为IO Buffer的实际工作频率,DDR2中时钟频率为核心频率的2倍,DDR3 DDR4中时钟频率为核心频率的4倍。

2023-12-25 18:18:47 1188

1188

的引脚介绍

DDR内存条的引脚数,取决于内存条的类型和规格。以下是一些常见的 DDR内存条类型和它们的引脚数 :

DDR1内存条,184引脚(92针对每侧)

DDR2内存条,240引脚(120针对每侧

2023-12-25 14:02:58

的引脚介绍

DDR内存条的引脚数,取决于内存条的类型和规格。以下是一些常见的 DDR内存条类型和它们的引脚数 :

DDR1内存条,184引脚(92针对每侧)

DDR2内存条,240引脚(120针对每侧

2023-12-25 13:58:55

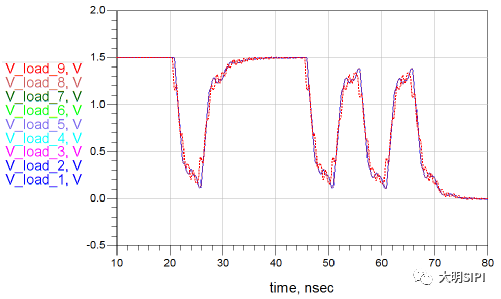

大家如果做过DDR的设计可能会发现在进行多片DDR连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?

2023-12-18 15:58:26 299

299

法人方面解释说:“标准型dram和nand目前由三星、sk hynix、美光等跨国企业主导,因此,中台湾企业在半导体制造方面无法与之抗衡。”在ddr3 ddr3的情况下,台湾制造企业表现出强势。ddr3的价格也随之上涨,给台湾半导体企业带来了很大的帮助。

2023-11-14 11:29:36 405

405 DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3885

3885 DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 516

516

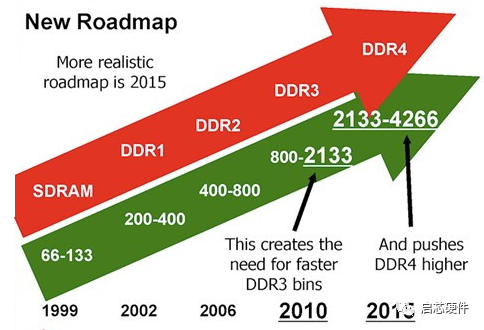

DDR存储器发展的主要方向一言以蔽之,是更高速率,更低电压,更密的存储密度,从而实现更好的性能。

2023-10-01 14:03:00 488

488

摘要:本文将对DDR3和DDR4两种内存威廉希尔官方网站

进行详细的比较,分析它们的威廉希尔官方网站

特性、性能差异以及适用场景。通过对比这两种内存威廉希尔官方网站

,为读者在购买和使用内存产品时提供参考依据。

2023-09-27 17:42:10 1088

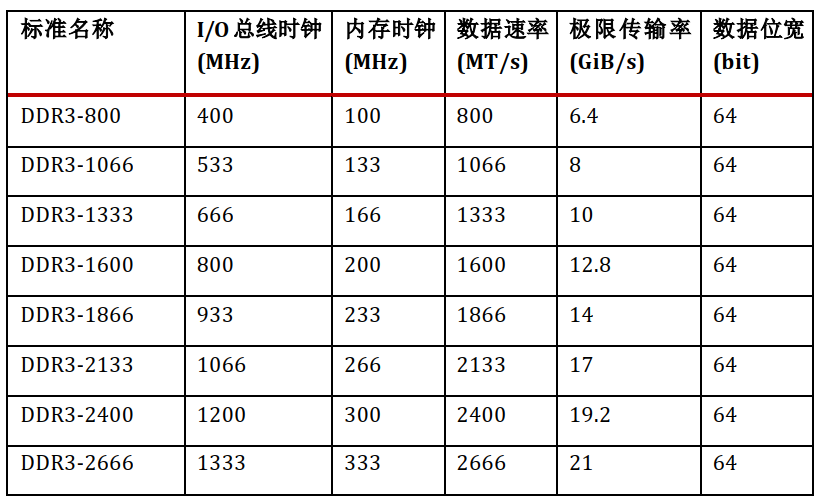

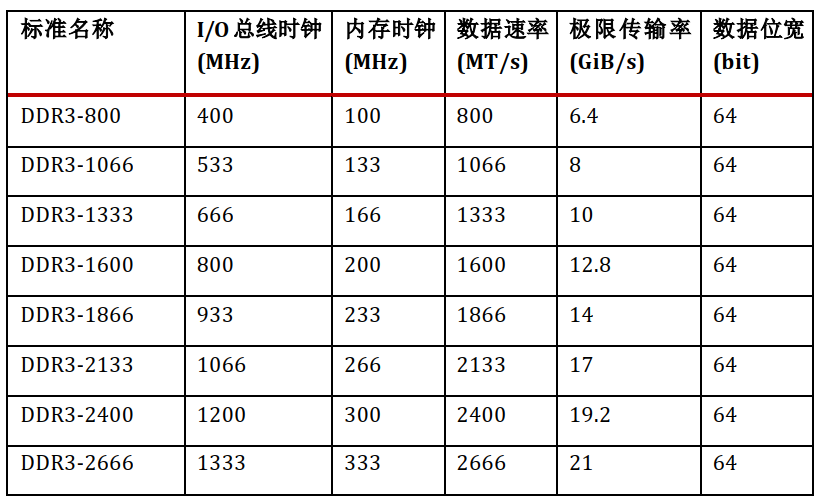

1088 我们在买DDR内存条的时候,经常会看到这样的标签DDR3-1066、DDR3-2400等,这些名称都有什么含义吗?请看下表。

2023-09-26 11:35:33 1922

1922

电子发烧友网站提供《具有最大1Gb DDR2 SDRAM的SAMA5D2 SIP MPU.pdf》资料免费下载

2023-09-25 10:11:12 0

0 。

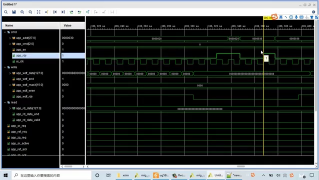

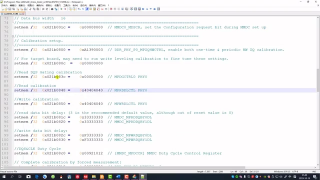

这里编写了一个简单的测速DDR3访问速度的工程,当按下KEY2,FPGA会将等同于一张4K分辨率大小的数据写入DDR3中,同时开始计时,当完成写入后停止计时,并通过Debugger的波形抓取结束时

2023-09-21 23:37:30

相对于DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

2023-09-19 14:49:44 1478

1478

三星公司计划在下半年再次削减DRAM制程的产能,而今年以来这一减产主要针对DDR4。业界普遍预期,三星的目标是在今年年底之前将库存水平降至合理水平。这一减产举措可能会导致DDR4市场价格上涨,而目前

2023-09-15 17:42:08 996

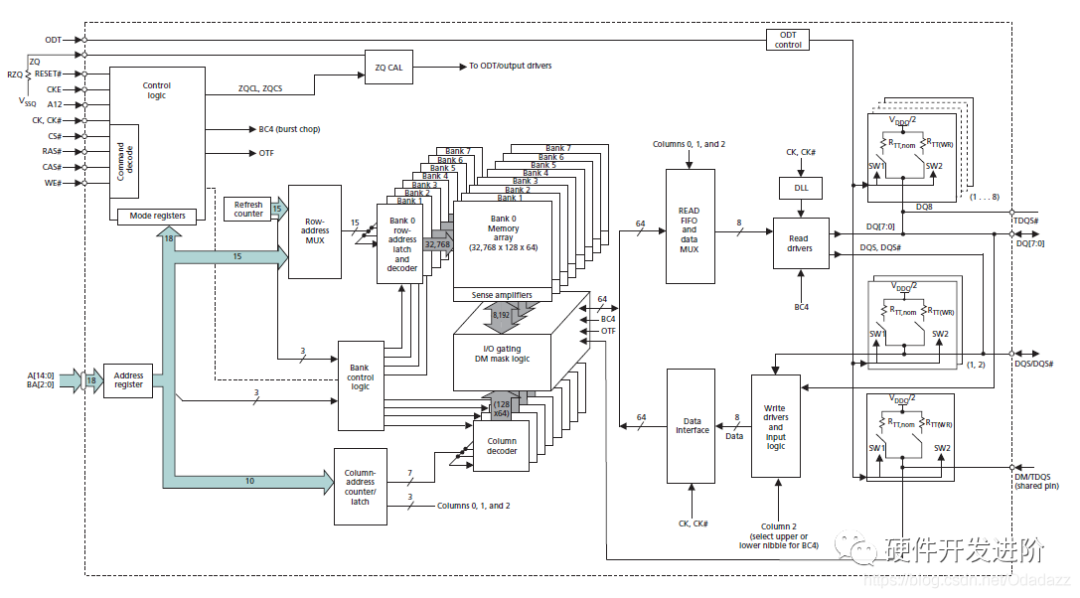

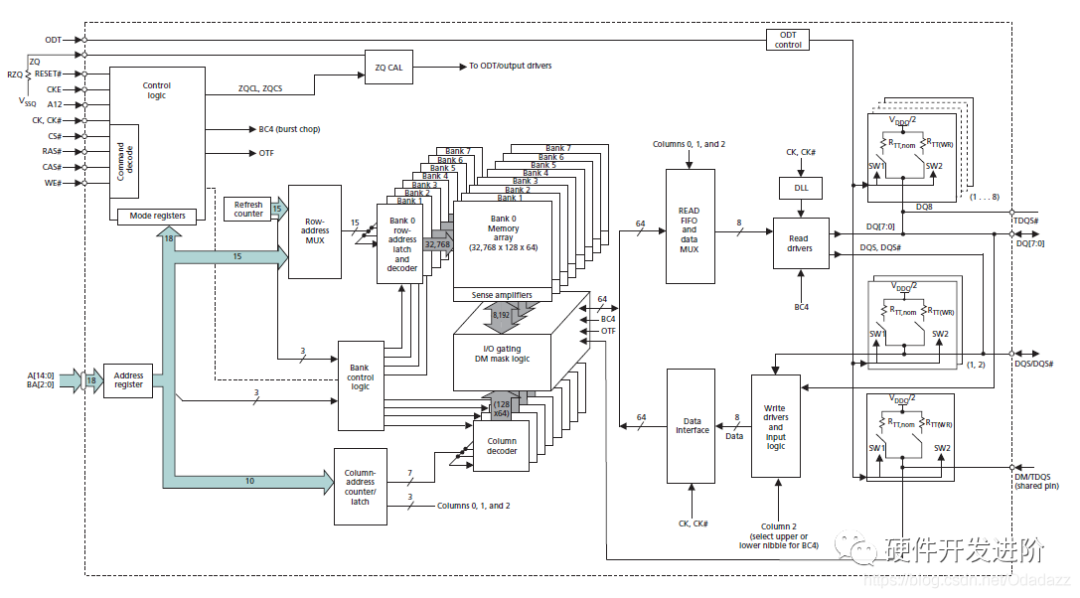

996 以MT41J128M型号为举例:128Mbit=16Mbit*8banks 该DDR是个8bit的DDR3,每个bank的大小为16Mbit,一共有8个bank。

2023-09-15 15:30:09 629

629

DDR3带宽计算之前,先弄清楚以下内存指标。

2023-09-15 14:49:46 2497

2497

一看到DDR,联想到的就是高速,一涉及到高速板有些人就比较茫然。高速板主要考虑两个问题点,当然其它3W,2H是基本点。

2023-09-15 11:42:37 757

757

内置校准: DDR3和DDR4控制器通常具有内置的校准机制,如ODT (On-Die Termination)、ZQ校准和DLL (Delay Locked Loop)。这些机制可以自动调整驱动和接收电路的特性,以优化信号完整性和时序。

2023-09-11 09:14:34 420

420 本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 741

741

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1887

1887

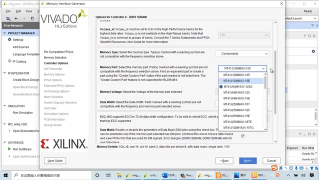

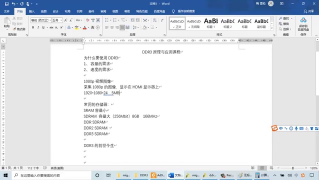

MCU200T的DDR3在官方给的如下图两份文件中都没有详细的介绍。

在introduction文件中只有简略的如下图的一句话的介绍

在schematic文件中也没有明确表明每个接口的具体信息

2023-08-17 07:37:34

在配置DDR200T的DDR3时,一些关键参数的选择在手册中并没有给出,以及.ucf引脚约束文件也没有提供,请问这些信息应该从哪里得到?

2023-08-16 07:02:57

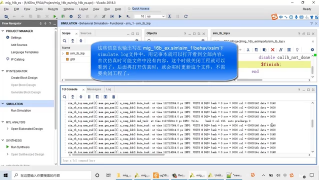

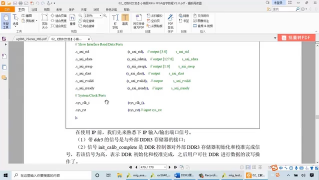

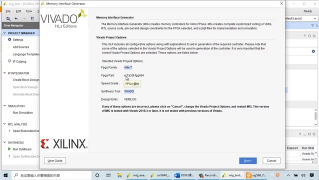

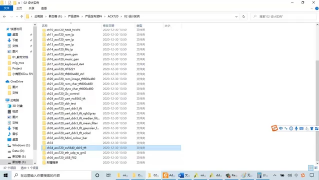

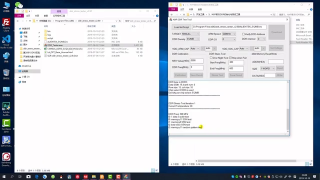

复制Vivado工程路径vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夹。粘贴到仿真路径testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夹)下。

2023-08-12 11:08:27 735

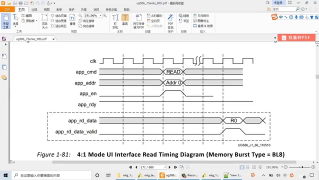

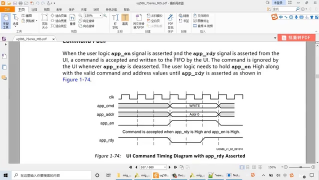

735 PL341内存控制器是一款高性能、面积优化的DDR2 SDRAM内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结了周期模型的功能与硬件的功能,以及周期模型的性能和准确性。

2023-08-12 06:01:49

PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

DDR5的主板不支持使用DDR4内存。DDR5(第五代双倍数据率)和DDR4(第四代双倍数据率)是两种不同规格的内存威廉希尔官方网站

,它们在电气特性和引脚布局上存在明显差异。因此,DDR5内存模块无法插入DDR4主板插槽中,也不兼容DDR4内存控制器。

2023-08-09 15:36:25 12792

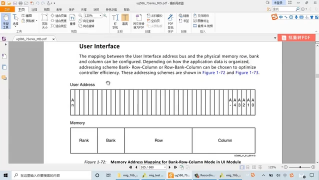

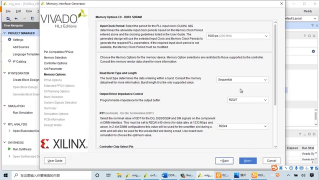

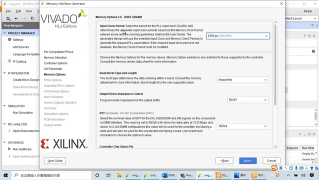

12792 xilinx平台DDR3设计教程之设计篇_中文版教程3

2023-08-05 18:39:58

CoreLink DDR2动态存储器控制器(DMC-341)威廉希尔官方网站

参考手册

2023-08-02 15:28:28

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 0

0 DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种威廉希尔官方网站

,中国大陆工程师习惯用DDR称呼用了DDR威廉希尔官方网站

的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。

2023-07-16 15:27:10 3362

3362

DDR3的速度较高,如果控制芯片封装较大,则不同pin脚对应的时延差异较大,必须进行pin delay时序补偿。

2023-07-04 09:25:38 312

312

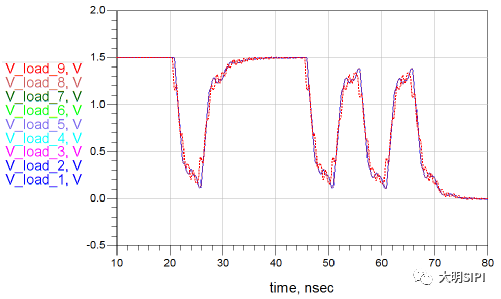

这里介绍两种方式改善带有ECC的奇数负载的DDR2信号质量。一种不需要改变拓扑结构,另一种需要对拓扑结构进行调整。

2023-06-15 17:39:34 474

474

视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024 我正在尝试基于 LS1028ARDB 评估板开发定制板。

在我拥有的定制板中,我们已将 DDR4 替换为 DDR3。

我已经看到 DDR3 正在使用自定义 RCW + PBI 工作。所以现在我想要

2023-06-01 09:03:54

)DDR3 IP 文件:6_IP_setup_packet\\\\DDR3\\\\ipsxb_hmic_s_v1_4

(2)IP 安装步骤:1_Demo_document\\\\工具使用篇

2023-05-31 17:45:39

我正在使用带有 ECC 芯片的 4GB DDR3 RAM 连接到 T1040 处理器 DDR 控制器。

我尝试了这个序列,但未能成功生成 DDR 地址奇偶校验错误:

步骤1:

ERR_INT_EN

2023-05-31 06:13:03

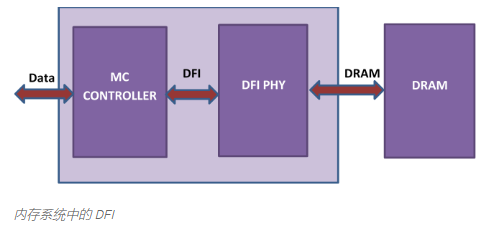

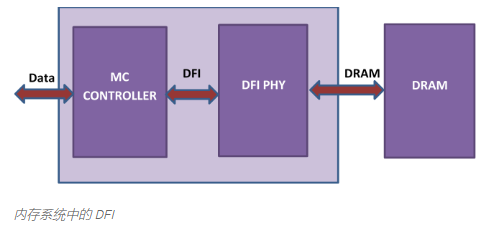

、时序和可编程参数。DFI 适用于所有 DRAM 协议,包括 DDR4、DDR3、DDR2、DDR、LPDDR4、LPDDR3、LPDDR2 和 LPDDR。

2023-05-26 15:27:31 4566

4566

以下步骤完成:

(1)DDR3 IP 文件:6_IP_setup_packet\\\\DDR3\\\\ipsxb_hmic_s_v1_4

(2)IP 安装步骤:1_Demo_document

2023-05-19 14:28:45

你好 :

专家,我们想使用S32R45和DDR3,你能帮我在哪里找到示例项目或用例吗?

2023-05-17 08:13:46

内存是数据中心、服务器以及个人计算机等威廉希尔官方网站

发展的重要组成。目前内存的发展是由DDR威廉希尔官方网站

路线引导,TE Connectivity(以下简称“TE”)经历了DDR1、DDR2、DDR3、DDR4的迭代

2023-05-06 17:33:42 1392

1392

在 i.MX6 SOLO 中有没有办法读取芯片 DDR3 的大小?

2023-05-06 07:04:11

IC CONV DDR DDR2 DDR3

2023-04-06 19:44:54

IC MUX/DEMUX DDR3 1:2 42WQFN

2023-04-06 11:36:35

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

IP CORE DDR2 SDRAM XO2

2023-03-30 12:02:09

SITE LICENSE IP CORE DDR3 ECP3

2023-03-30 12:02:09

SITE LICENSE DDR2 SDRAM ECP3

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2M

2023-03-30 12:01:46

SITE LICENSE DDR3 SDRAM ECP3

2023-03-30 12:01:46

IP CORE DDR2 SDRAM XO2

2023-03-30 12:01:19

IP CORE DDR3 PHY ECP3 USER CONF

2023-03-30 12:01:19

IP CORE DDR2 SDRAM CTLR ECP2M

2023-03-30 12:01:17

IP CORE DDR2 SDRAM CTLR ECP3

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR ECP2

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR SC/SCM

2023-03-30 12:01:16

IP CORE DDR3 SDRAM CTLR ECP3

2023-03-30 12:01:16

正在加载...

电子发烧友App

电子发烧友App

评论