中心议题:

讨论辐射发射产生的原因

详细描述解决高速电路辐射发射超标的过程

解决方案:

使中频板停止工作,排除中频板产生干扰的可能

采用关断干扰源 、减小高频电流幅度解决辐射发射超标问题

问题的提出

通信威廉希尔官方网站 的发展要求器件的速度愈来愈高,由此引起的电磁兼容问题就更加严重。本文以无线宽带接入系统的终端用户单元(SU)为例,来探讨通信产品的辐射发射超标问题。

无线宽带接入系统的终端用户单元由860小系统、8240小系统、FPGA(现场可编程门阵列)和基带中频单元组成,其中860小系统、8240小系统和FPGA电路在一块PCB(印刷电路板)上,称为网络接口板;基带中频电路单独为一块PCB,称为基带中频板。二者通过插座相连,传递信号和电源。设备外壳为注塑壳体,内层没有喷涂导电漆。笔者对该产品辐射发射指标进行了测试。

测试环境为电波暗室,测试设备为宽带天线、频谱分析仪和信号放大器,天线可以在1 m与4 m高度范围内升降,被测产品放置在一个可360°旋转的平台上,距离天线3 m。测量时转动平台,升降天线找到最大干扰,天线测量取水平和垂直两种极化。

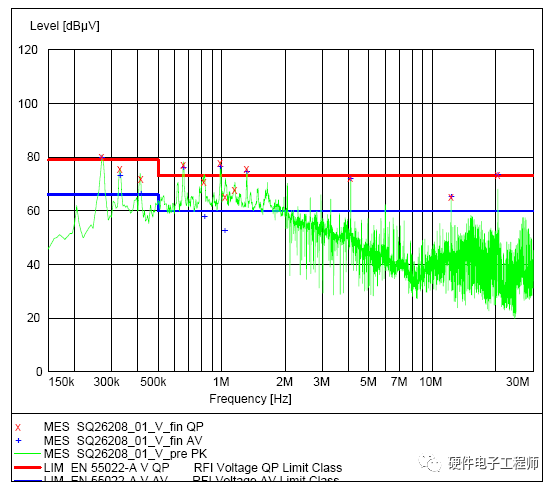

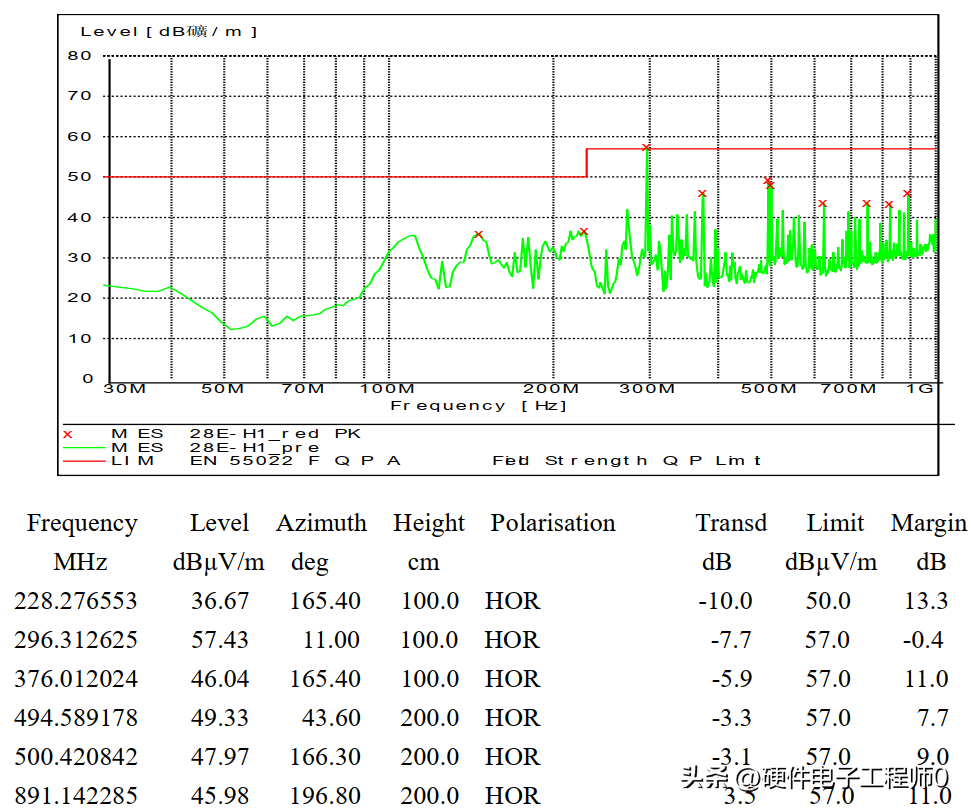

按照接入设备的电磁兼容(EMC)测试要求,设备上电正常运行,测试仪器在30~1 000 MHz的频率范围内进行扫描,其中在30~230 MHz频率范围内要求电磁干扰(EMI)的准峰值低于40 dBuV/m,在230~1000 MHz频率范围内,EMI的准峰值低于47 dBuV/m。测试的结果是:在垂直方向上,412.5 MHz处超标4.08 dB,577.5 MHz处超标3.5 dB;在水平方向上,577.5 MHz处超标7.9 dB,参见图1。

考虑到中频板上有调制解调电路,其载波频率比较高(为349 MHz),为此将中频板的5 V和3.3 V工作电源断开,使中频板停止工作。再测试设备的电磁干扰时,仍然在上述两个频点处有超标,因而可以排除中频板产生上述频点干扰的可能。

原因分析

任何电磁兼容性问题都包含3个要素,即干扰源、敏感源和耦合路径,这3个要素中缺少一个,电磁兼容问题就不会存在。因此,在解决电磁兼容问题时,也要从这3个要素着手进行分析,再根据具体情况,采取适当的措施消除其中的一个。

首先从干扰源开始分析。在通信产品中,电路的工作时钟越来越高,信号的上升/下降沿越来越陡,由此带来的电磁兼容问题也愈加尖锐。数字电路的电磁兼容设计中要考虑的是数字脉冲的上升沿和下降沿决定的频带宽,而不是数字脉冲的重复频率。根据经验公式,计算EMI发射带宽的公式可以表示为:

f=0.35/Tr (1)

其中,f是频率(单位是GHz),Tr是信号上升/下降时间(单位是ns)。由此不难看出,一个具有2 ns上升沿的时钟信号辐射能量的带宽可达160 MHz,其辐射带宽可达10倍频,即1.6 GHz。

在电工学中,周期电流、电压、信号等都可以用一个周期信号来表示,即f(t)=f(t+kT),T为周期函数的周期。如果给定的周期函数同时有满足狄里赫利条件,则可以将其展开成付立叶级数:

将第1项A0称为直流分量,第2项称为一次谐波(或基波分量),其他各项统称为高次谐波,即2次、3次、4次……k次谐波。一个理想的方波信号包含了丰富的谐波分量。在实际的数字电路中,方波并不是理想的,它有一定的上升和下降时间。方波频谱包络线的衰减率不仅与方波的频率有关,而且还与方波脉冲的持续时间有关。方波脉冲的持续时间越短,高次谐波的干扰幅度越大。

因为终端网络接口板上没有412.5 MHz和577.5 MHz这两个频率信号,所以怀疑这两个频点可能是某些频率信号的谐波分量。高速电路中,时钟电流是第一辐射源。笔者对终端网络接口板上的各时钟信号进行了统计,如表1所示。

通过粗略计算,412.5 MHz信号近似等于83.3 MHz的5次谐波(83.3×5=416.5 MHz),而577.5 MHz近似等于83.3 MHz的7次谐波(83.3×7=583.1 MHz)。

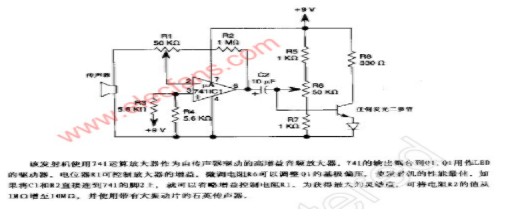

图2所示为8240时钟信号的产生原理图。8240外部有源晶振产生33 MHz的振荡频率,送入8240芯片,经内部PLL(锁相环)锁相倍频,输出83.3 MHz频率,作为SDRAM(同步动态随机读写存储器)的工作时钟,8240有4个引脚可以同时送出该83.3 MHz的时钟:SDRAM_CLK0~SDRAM_CLK3,而且可以在8240内部寄存器中设置开关。该单板在电路设计时,使用SDRAM_CLK0作为SDRAM工作时钟,另一路SDRAM_CLK3送至一测试点,方便调试时测量时钟信号,其余2路设置为关闭状态,不对外输出时钟。

初步试验

为了证实412.5 MHz和577.5 MHz这两个干扰频点是83.3 MHz时钟所致,笔者先尝试将8240的PLL配置电路取消,即8240锁相环不工作,不对外输出83.3 MHz时钟,再进入电波暗室测试。结果发现,在30~1 000 MHz的扫描频段中无超标频点,获得的测试曲线都在标准规定的准峰值以下。因此,可以判断干扰源就是8240输出的83.3 MHz时钟信号。

干扰源虽然定位了,但系统在实际应用中83.3 MHz时钟是必须要输出的,接下来的问题就是如何解决83.3 MHz时钟引起的EMI问题。因为电路的结构方案已经确定,想要去掉敏感源,难度太大,因此重点要从寻找干扰耦合路径入手。

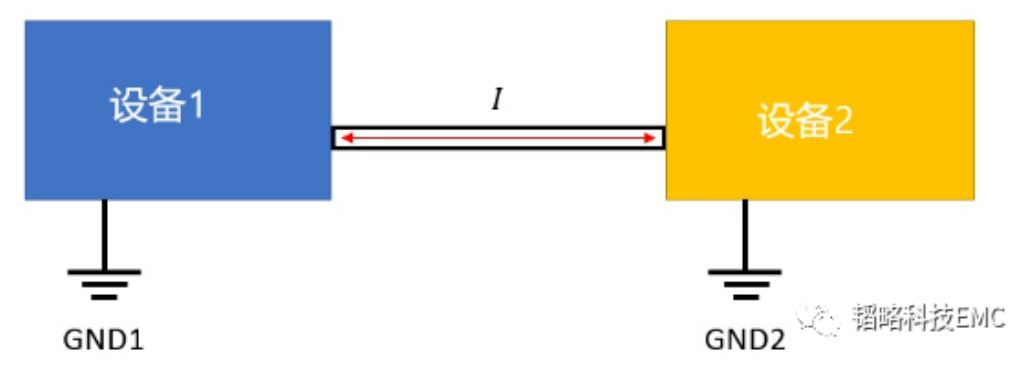

在通信产品中,通常辐射的根源在其数字电路部分,而数字电路的辐射按其方式可分为差模辐射和共模辐射:差模辐射是由于电流流过电路中的导线环路造成的,这些环路相当于正在工作的小天线,向空间辐射磁场,差模辐射与环路电流和环面积成正比,与电流频率的平方成正比;共模辐射是由于电路中存在不希望的电压造成的,此电压降使系统中某些部分处于高电位的共模电压下,PCB板上的信号线在共模电压的作用下被激励,形成辐射电场的天线辐射与频率、天线长度及流经天线的共模电流的幅度成正比。

解决方法

了解了辐射发射的机理后,可采取以下措施进行解决:

a.关断干扰源

在单板的表层有一测试孔,就是图2中的SDRAM_CLK3信号,频率为83.3 MHz,作为调试中测量时钟信号所用。因为该信号属于无负载形式,而且频率比较高,在物理上可以等效于一个天线,向空间辐射高频电磁波,该电磁波包含了83.3 MHz的高次谐波。

笔者修改8240控制寄存器,将SDRAM_CLK3信号屏蔽,不对外输出83.3 MHz时钟,再次进行EMI测试,结果577.5 MHz在垂直和水平方向上均没有超标,412.5 MHz在垂直方向有3.85 dB的裕量,在水平方向有0.25 dB的裕量。这说明该测试点的辐射效应还是很强烈的,关闭该测试点也是有效的。 (2)减小地噪声。

上述测试结果的前提条件是基带中频板没有加电运行。实际应用时,中频板也应处于工作状态。在恢复给中频板的供电后,测试结果立刻变化:412.5 MHz点在水平方向超标4.21 dB,在垂直方向超标4.51 dB;而577.5 MHz在水平方向超标5 dB,垂直方向无超标。

对中频板单独进行测试,未发现以上2处超标频点。利用直流稳压源对单板测试,在这2点仍然存在干扰,排除了电源单体引发干扰的可能。这一现象表明,随着中频板的工作,电源的工作电流增大,地噪声引起的共模干扰增强,83.3 MHz的谐波通过地噪声增大了辐射强度。

笔者用高速示波器测量出网络接口板的工作地噪声(Vp-p)为96 mV,中频板工作后,噪声增至130 mV以上。此测量方法可能存在偏差,但总体的趋势是2块单板同时工作后,的确增加了地线噪声,对EMI有一定的影响,只不过影响是有限的。

在PCB布线时,笔者已经考虑到了高速信号线的EMI问题,因此一些关键信号线、高速时钟线均在PCB内层布线,夹在电源层和地层之间,应该说屏蔽措施是比较可靠的。进一步还可以考虑在83.3 MHz时钟线两侧采取“包地”的方法,用两根平行的地线将该时钟线包裹起来,可以在一定程度上减小EMI发射。

b.减小高频电流幅度

在高速电路中,PCB线和集成电路的引脚上都不同程度地存在寄生电阻、寄生电容和寄生电感,在不同的频率下呈现不同的阻抗特性,从信号完整性的角度来看,串联阻抗匹配能够有效抑制信号反射和振荡,而这两者恰恰是EMI的主要来源。

83.3 MHz的时钟线是否因为线路阻抗匹配不当,在线路上引起信号反射而导致EMI超标呢?在单板的设计阶段,笔者使用Cadence公司的SI(信号完整性)仿真工具Signal Explore,对关键信号的串联匹配电阻进行了细致的仿真,选择51R匹配电阻,较好地抑制了时钟信号的过冲和振荡,从而最大程度地限制了EMI发射强度。选择阻值更大的匹配电阻固然可以将信号过冲压制得更低一些,同时EMI发射也将因此改善,但此举会引起信号上升/下降沿变缓,严重时会导致系统时序出错,引发一系列SI问题。因此,对匹配电阻的选择要适可而止,须兼顾信号质量和时序的双重需要。

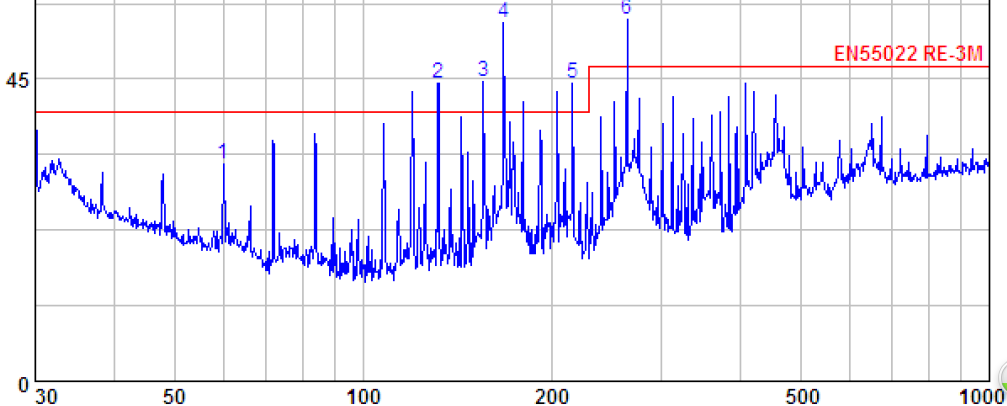

至此,从电路设计上暂时还没有更好的改进办法。在结构工程师的协助下,将终端单元使用的注塑壳体内表面喷涂导电漆,对辐射电磁波进行屏蔽,网络接口板和基带中频板均加电运行,再次测试的结果如图3所示。从图3可见,在30~1 000 MHz的频段内,没有超标频点,笔者最关心的412.5 MHz在垂直方向有10.49 dB的裕量,577.5 MHz在垂直方向有6.9 dB的裕量。由此可见,在水平方向有2.1 dB的裕量,屏蔽的效果比预期的要好。根据经验,喷涂导电漆前后的信号衰减一般在2~3 dB,而这次试验的结果衰减了将近10 dB!

结论

笔者一直负责通信产品的电磁兼容性能的测试并作相应的解决方法的研究,曾先后对终端网络接入单元和基站接入单元进行了多项电磁兼容测试。在所有的测试项目中,最难通过、也最难解决的就是辐射发射指标超标的问题。

难点之一是寻找干扰源。大多来自高速时钟信号的高次谐波,尤其是奇次谐波:3、5、7、9次,像本文提到的就是5次和7次谐波。与此同时,还要排除其他成分的干扰可能,如笔者分别对中频板和电源单体进行测试,逐一排除,最终将干扰源定位在83.3 MHz时钟源上。

难点之二是干扰源定位后,对策也很难选择。首先从辐射产生的机理,寻找最有可能产生天线效应的信号线,像本文描述的表层测试孔。最有效的方法就是切断辐射路径,使之不能成为良好的发射天线。

信号线的阻抗匹配不当引发的信号反射和振荡也是EMI的重要原因,最佳方法是在设计阶段对信号进行严格细致的仿真,从信号完整性的角度首先解决之。

能够从电路设计方面最大限度地抑制EMI是最好的,实在无能为力的情况下应该考虑从结构工艺方面着手,增加屏蔽措施,本文提到的注塑壳体内层表面喷涂导电漆对EMI的抑制效果是显而易见的。

电子发烧友App

电子发烧友App

评论