楷登电子今日正式发布Cadence® Virtuoso®定制 IC设计平台的威廉希尔官方网站

升级和扩展,进一步提高电子系统和 IC设计的生产力。新威廉希尔官方网站

涉及Virtuoso 系列几乎所有产品,旨在为系统工程师提供更稳健的设计环境和生态系统,助其实现并分析复杂芯片、封装、电路板和系统。

2018-04-11 16:40:16 9290

9290 Cadence与MathWorks的无缝集成可以简化数据交换过程,增强分析能力,缩短PCB设计周期。

2018-05-24 10:45:43 8187

8187 Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 17:13:53 4218

4218 这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 威廉希尔官方网站

显著提升设计生产力; Virtuoso Studio 与 Cadence 最前沿的威廉希尔官方网站

和最新的底层架构集成,助力设计工

2023-04-20 15:52:13 508

508

各位大佬好,我正在学习IC设计,对于Cadence Virtuoso这个软件有一些入门级的小问题:我从AnaglogLib拷贝NMOS管和PMOS管到自己的library下面,打开他们的CDF参数看

2017-10-16 00:26:33

Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和威廉希尔官方网站

增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

Cadence 宣布推出其最新版Cadence? Allegro? 与 OrCAD?印刷电路(PCB) 软件,它拥有的全新功能与特性能够提高PCB工程师的绩效与效率。Allegro与OrCAD

2018-09-10 16:37:20

本帖最后由 michael_2009 于 2011-8-5 22:27 编辑

求:Cadence SPB15.7 Allegro中文版电路板.brdConstraint详细的设置说明?哪位高人

2011-08-03 10:47:35

Integrity 3D-IC 平台实现更高的生产力,而不是孤立的单晶片实施方法。该平***特地提供了系统规划、集成的电热、静态时序分析 (STA) 和物理验证流程,从而实现更快、高质量的 3D 设计闭合。它还

2021-10-14 11:19:57

可以与Cadence主要的设计平台无缝整合:可以与Encounter整合实现裸片抽象协同设计,与CadenceVirtuoso整合实现RF模块设计,并与CadenceAllegro整合实现封装与电路板

2008-06-27 10:24:12

Cadence设计系统公司发布Cadence®Allegro®系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和威廉希尔官方网站

增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-08-28 15:28:45

Cadence设计系统公司发布Cadence?Allegro?系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和威廉希尔官方网站

增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2008-06-19 09:36:24

Cadence高速电路板设计与仿真第3版,分享资料给大家.

2017-02-28 10:45:34

)。实际 Theta JC 数据会根据使用 JEDEC 印制电路板 (PCB) 测试的封装生成。图 3 Theta-JC 解释 天啊,谁有这么多时间和耐性做完所有这种分析和测试——当然 JEDEC 除外

2018-09-14 16:36:06

集成电路生产流程见下图:[img][/img]整个流程分为六个部分:单晶硅片制造,IC设计,光罩制作,IC制造,IC测试和封装。1.IC生产流程 [单晶硅片制造] 单晶硅片是用来制造IC的,单晶硅

2019-01-02 16:28:35

cadence virtuoso教程 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

/>相比Cadence 的综合工具略为逊色然而Cadence 在仿真电路图设计<br/>自动布局布线版图设计及验证等方面却有着绝对的优势Cadence

2008-07-12 23:11:21

关于电路板IC类封装尺寸的汇总——电路板设计检验或者维修检查参考可用

2019-02-13 10:35:28

的焊点。 电路板OSP 1、工艺流程:除油→水洗→微蚀→水洗→酸洗→纯水洗→OSP→纯水洗→烘干。 2、原理:在电路板铜表面上形成一层有机膜,牢固地保护着新鲜铜表面,并在高温下也能防氧化和污染

2018-09-19 16:27:48

在PCB设计中,一般采用双面板或多面板,每一层的功能区分都很明确。在多层结构中零件的封装有两种情况,一种是针式封装,即焊点的导孔是贯穿整个电路板的;另一种是STM封装,其焊点只限于表面层;元器件

2018-08-29 10:28:18

`请问电路板上面的ic是什么?`

2019-10-30 16:31:59

往往比单一维修一块坏电路板还要便捷和容易。电路板检修的一般顺序 (1)首先,仔细观察故障电路板的表面有无明显的故障痕迹。如:有无烧焦烧裂的集成IC或其它元件,线路板是否有断线开裂的痕迹。(2)、了解

2019-08-12 22:50:15

功能予以解决。黄金工具组合及设计流程 现在有许多EDA厂商均可以提供高速系统PCB设计的EDA工具,帮助用户在这一领域中有效的提高设计质量,缩短设计周期。在应用电气规则驱动方法的EDA系统板级工具中最

2018-08-24 16:48:10

《集成电路芯片封装威廉希尔官方网站

》是一本通用的集成电路芯片封装威廉希尔官方网站

通用教材,全书共分13章,内容包括:集成电路芯片封装概述、封装工艺流程、厚膜与薄膜威廉希尔官方网站

、焊接材料、印制电路板、元件与电路板的连接、封胶材料

2012-01-13 13:59:52

`请问集成电路板上的线是什么?`

2019-10-31 16:59:25

我是一个清洁设备(洗地机、扫地机)的经销商,这些年发现设备故障率居高不下,几乎都是出在集成电路板上,一旦电路板出现问题,严重影响客户的使用,厂家也不愿意对集成电路板进行改进,我就在想:设备控制能否

2017-05-09 11:39:43

Allegro威廉希尔官方网站

建立于一种独特的芯片-封装-电路板协同设计方法,与来自Cadence Encounter数字实现系统和Virtuoso定制模拟产品线的流程直接双向综合,包括低功耗、混合信号、千兆

2020-07-06 17:50:50

Altium Designer 14电路设计与仿真从入门到精通为了让用户对电路设计过程有一个整体的认识和理解,下面我们介绍一下“PCB”电路板设计的总体设计流程。

2019-08-06 06:04:27

进行检查和修正。 3、布置各零件封装的位置 可利用系统的自动布局功能,但自动布局功能并不太完善,需要进行手工调整各零件封装的位置。 4、进行电路板布线 电路板自动布线的前提是设置安全

2019-04-15 07:35:02

`` 本帖最后由 lzr858585 于 2021-4-1 14:31 编辑

Allegro PCB高速电路的完整设计流程,手把手教会你Cadence高速电路板设计。``

2021-04-01 14:13:00

集成电路(IC)包装在瓷片内,瓷片的底部是排列成方形的插针,这些插针就可以插入获焊接到电路板上对应的插座中,非常适合于需要频繁插波的应用场合。对于同样管脚的芯片,PGA封装通常要比过去常见的双列直插封装

2019-04-13 08:00:00

内层材料层压→孔加工→孔金属化→指外层图形→镀耐腐蚀可焊金属→去除感→光胶腐蚀→插头镀金→外形加工→热熔→涂助焊剂→成品。印制电路板的功能印制电路板在电子设备中具有如下功能:提供集成电路等各种电子

2019-10-18 00:08:27

`请问印制电路板属于集成电路产业吗?`

2019-08-30 17:50:07

一般就是指芯片的集成,像电脑主板上的芯片,CPU内部结构,全是叫集成电路,而印刷电路板就是指大家通常见到的线路板等,也有在电路板上包装印刷焊接芯片。集成电路(IC)是焊接在PCB板上的;PCB板

2023-06-27 14:38:24

基于Cadence virtuoso与Mentor Calibre的CMOS模拟集成电路版图该如何去设计?怎样去验证一种基于Cadence virtuoso与Mentor Calibre的CMOS模拟集成电路版图?

2021-06-22 06:12:49

的设计平台。在综合比较后,本文选定了CadenceVirtuoso全定制IC设计工具。VirtUOSO是Cadence公司推出的用于模拟/数字混合电路仿真和射频电路仿真的专业软件。基于此平台

2018-11-26 10:56:11

之间的电气连接通常是通过电路板横断面上的镀通孔实现的。多层线路板的优缺点优点: 装配密度高、体积小、质量轻由于装配密度高,各组件(包括元器件)间的连线减少,因此提高了可靠性;可以增加布线层数,从而

2019-06-15 06:30:00

在多层电路板设计中,一般内电层会有电源层、地层两种。为了有效实现电磁屏蔽,一般令电源层面积比地层小(电源层比地层内缩)。并在内缩区域打上一圈回流地过孔。 在allegro中操作如下

2021-12-29 06:35:51

互联汽车带来更智能的驾驶体验自主驾驶的互联汽车实现无缝驾驶的智能系统

2021-03-09 06:20:45

对未知电路板的测绘所使用的常用办法有哪几种?未知电路板原理图测绘系统的设计与实现

2021-04-22 06:18:37

图布局结构,最后根据芯片内各个信号的关系来进行电路布线的操作。以上的操作都可以在Cadence的IC 5.1集成设计环境下的Virtuoso中完成,当完成布局布线后全定制Asic的版图基本就确定了,然后

2013-01-07 17:10:35

rt,用cadence画了完整的电路板,但是不会仿真,有赏求指导。QQ:1145275787.

2017-03-20 22:34:05

线路板、电路板、PCB抄板流程与技巧是什么

2021-04-26 06:49:33

请问 cadence中的创建电路板的向导中,有一步是要确定每一层的定义,有个地方需要打钩,“generate negative layers for power planes”请问这个是什么意思,翻译说为电源平面产生负层?啥叫负层啊?请高手指点。

2013-03-03 15:53:10

`请问阻抗电路板可以帮助解决哪些问题?`

2020-04-03 17:43:25

。 FDMS96xx系列的引脚输出经仔细设计,可在PCB布局中轻易地直接连接至PWM控制器,这种创新封装概念缩短了设计时间,并减少了电路板布局迹线的寄生电感,有助于提高总体系统效率。 FDMS96xx系列

2018-11-22 15:48:58

我司定制生产各种柔性FPC电路板,硬性PCB电路板,单层电路板,多层电路板,双层电路板,刚柔一体电路板等。 打样周期7天左右,批量生产周期15天内。 主要应用于手机,便携计算机

2022-09-20 18:11:35

业务流程集成是协同管理平台的核心威廉希尔官方网站

之一。本文提出采用基于BPEL 的集成方式实现协同管理平台与应用系统之间的业务流程集成,并设计了协同管理平台的业务流程集成方案

2009-06-19 09:26:42 9

9 、实现方式以及其在轻便、高效与安全方面的优势。一、设计理念FH8A150挂脖小风扇电路板的设计,始终围绕着轻便、高效与安全这三个核心理念。在轻便方面,电路板采用了高

2024-03-11 22:40:55

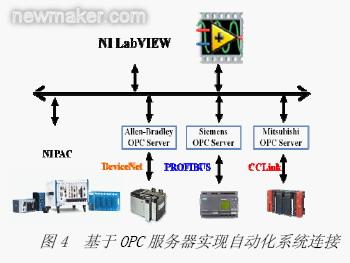

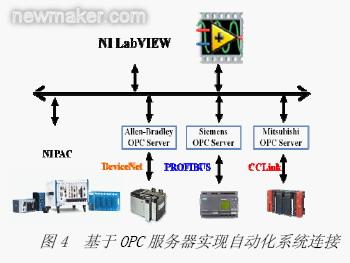

NI LabVIEW及PAC平台与传统自动化系统的无缝集成

现今,流程型和离散型工业生产企业正面临全球化市场竞争下不断增长的压力:最大

2009-06-13 16:07:16 1625

1625

Cadence Allegro SiP and IC Packaging 16.3版推出

Cadence设计系统公司宣布,利用最新的系统封装(SiP)和IC封装软件,封装设计者将在芯片封装协同设计过程中和整个半导体设计链中

2009-11-04 08:52:51 1826

1826 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence® Virtuoso®统一定制/模拟(IC6.1)以及Encounter®统一数字流程生产其混合信号芯片。

2011-09-27 11:06:26 1483

1483 Cadence 设计系统公司日前宣布,汽车零部件生产商Denso公司在改用了Cadence定制/模拟与数字流程之后,在低功耗混合信号IC设计方面实现了质量与效率的大幅提升。将Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 Cadence教程:基于Cadence的IC设计

2013-04-07 15:46:14 0

0 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 842

842 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布推出用于实现电学感知设计的Virtuoso®版图套件,它是一种开创性的定制设计方法,能提高设计团队的设计生产力和定制IC的电路性能。

2013-07-15 17:13:14 2080

2080 全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字威廉希尔官方网站

交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 1384

1384 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence ® Encounter® 数字威廉希尔官方网站

交付出55纳米平台的参考设计流程。

2013-08-16 12:02:40 1446

1446 基于Wide I/O接口的3D堆叠,在逻辑搭载存储器设计上进行了验证 ,可实现多块模的整合。它将台积电的3D堆叠威廉希尔官方网站

和Cadence®3D-IC解决方案相结合,包括了集成的设计工具、灵活的实现平台,以及最终的时序物理签收和电流/热分析。

2013-09-26 09:49:20 1346

1346 Mentor Graphics 公司(纳斯达克代码:MENT)今天宣布推出最新 Xpedition® Package Integrator 流程,这是业内用于集成电路 (IC)、封装和印刷电路板 (PCB) 协同设计与优化的最广泛的解决方案。

2015-03-24 12:03:16 1684

1684 IC design 集成电路的设计流程以及cadence的简介,使用方法和入门须知。

2016-03-14 14:11:33 25

25 2017年4月18日,中国上海 – 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日正式发布针对7nm工艺的全新Virtuoso® 先进工艺节点平台。通过与采用7nm FinFET

2017-04-18 11:09:49 1165

1165 、对基带低频大信号有高线性度要求的模块、发射端大电流的PA 模块、锁相环频率综合器中的数字块,以及非线性特性的VCO等各具特点的电路。众多的电路单元及其丰富的特点必然要求在这种系统的设计过程中有一个功能丰富且强大的设计平台。在综合比较后,本文选定了Cadence Virtuoso 全定制IC 设计工具。

2018-06-06 09:37:00 10797

10797

采用Virtuoso电路原理图编辑器与Virtuoso版图套件将总周转时间缩短30-50%:Virtuoso电路原理图编辑器内置种类齐全的的,用于各种仿真的,定义明确的元件库,可以加快模拟电路

2018-08-08 18:11:11 1324

1324 该流程无缝集成在Cadence Virtuoso平台中,并使用Xpeedic加速矩量法引擎和人工神经网络(ANN)威廉希尔官方网站

,既提供在设计阶段快速准确的无源器件建模和电路综合功能,又能在Sign-Off

2018-11-09 11:53:09 3716

3716 区别于altium的一库走天下,cadence的PCB套件流程中,PCB封装的制作需要单独制作pad,然后绘制封装。这两步的工具分别为Padstack和PCB Editor

2019-11-02 09:32:55 9632

9632

中;在设计阶段中实现快速无源器件建模和合成;在签核sign-off 阶段实现精确验证,同时能把封装的影响考虑进来。在本文中,演示了IRIS-HFSS整合流程,它无缝地集成在Cadence Virtuoso平台中(如图1所示)。在设计阶段,IRIS和 iModeler采用加速矩量法(

2020-10-20 10:42:00 2

2 cadence 公司 IC5141 工具主要包括集成平台 design frame work II、原理图编辑工具 virtuoso schematic editor、仿真工具、版图编辑工具

2020-07-21 08:00:00 3

3 Cadence 3D-IC Integrity 平台在统一的环境中提供 3D 芯片和封装规划、实现和系统分析。

2021-10-28 14:53:35 2114

2114 Integrity 3D-IC 是 Cadence 新一代多芯片设计解决方案,它将硅和封装的规划和实现,与系统分析和签核结合起来,以实现系统级驱动的 PPA 优化。 原生 3D 分区流程可自动智能

2021-11-19 11:02:24 3347

3347 Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 16:52:50 1594

1594

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence® 射频集成电路解决方案支持 TSMC 的 N6RF 设计参考流程和制程设计套件(PDK),加速推进移动、5G 及无线应用创新。

2022-06-22 16:34:01 1774

1774 。8nm 射频集成电路设计参考流程中支持的 Cadence 产品包括:Virtuoso ADE Product SuiteSpectre® RF SimulatorQuantus™ Extraction

2022-10-18 14:16:56 1342

1342 联华电子(NYSE:UMC;TWSE:2303)与楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平台的 Cadence 3D-IC 参考工作流程已通过联电的芯片堆栈威廉希尔官方网站

认证,将进一步缩短产品上市时间。

2023-02-03 11:02:23 1418

1418 ,包括最新的 N3E 和 N2 工艺威廉希尔官方网站

。这一新的生成式设计迁移流程由 Cadence 和台积电共同开发,旨在实现定制和模拟 IC 设计在台积电工艺威廉希尔官方网站

之间的自动迁移。与人工迁移相比,已使用该流程的客户成功地将迁移时间缩短了 2.5 倍。

2023-05-06 15:02:15 801

801 3Dblox 标准适用于在复杂系统中实现 3D 前端设计分区。通过此次最新合作,Cadence 流程优化了所有 TSMC 最新 3DFabric 供需目录上的产品,包括集成扇出(InFO)、基板

2023-05-09 09:42:09 615

615 设计过程。该平台实现了跨学科的工作流程无缝协作、集成了Cadence一流的签核级仿真分析工具,并提供了更强大的layout性能。

2023-05-22 15:40:10 1796

1796

了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-06-13 12:15:02 557

557

与 Pegasus Verification System 和 Voltus-XFi Solution 集成,为 Samsung PDK 用户提高了生产力,帮助他们更快地将高质量设计推向市场 中国上海

2023-06-30 10:08:30 681

681 内容提要 1 轻松实现节点到节点的设计和 layout 迁移 2 将定制/模拟设计迁移速度提升 2 倍 3 Cadence Virtuoso Studio 针对所有 Samsung Foundry

2023-07-04 10:10:01 471

471 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381 ❖ 双方利用 Cadence 的 Integrity 3D-IC 平台,优化多晶粒规划和实现,该平台是业界唯一一个整合了系统规划、封装和系统级分析的平台。 ❖ Integrity 3D-IC

2023-07-06 10:05:04 329

329 了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-07-11 12:15:02 241

241

了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-09-01 12:20:01 413

413

Cadence Virtuoso定制设计平台的一套全面的集成电流(IC)设计系统,能够在多个工艺节点上加速定制IC的精确芯片设计,其定制设计平台为模拟、射频及混合信号IC提供了极其方便、快捷而精确的设计方式。

2023-09-11 15:14:16 3202

3202

● AI 驱动的 Cadence Virtuoso Studio 助力 IC 设计在 TSMC 的制程威廉希尔官方网站

之间实现迁移时自动优化电路 ● 新的生成式英国威廉希尔公司网站

可将设计迁移时间缩短

2023-09-27 10:10:04 301

301 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布与台积电(TSMC)合作将新推出的 Cadence Virtuoso Studio 集成到 TSMC N16 毫米波设计参考流程

2023-09-28 10:10:02 533

533 平台以独特的方式将系统规划、实现和系统层级分析整合成为一个解决方案,实现无缝的原型验证 ● 共同客户可为其 AI、移动、5G、超大规模计算和物联网 3D-IC 设计进行系统原型建模,加快

2023-10-08 15:55:01 249

249 Cadence印刷电路板指南

2022-12-30 09:19:47 13

13 Cadence高速电路板设计与仿真(第2版)

2022-12-30 09:19:52 2

2 Cadence高速电路板设计与仿真(第3版)

2022-12-30 09:19:52 2

2 CADENCE高速电路板设计与仿真(第4版)

2022-12-30 09:19:53 56

56 Cadence高速电路板设计与仿真

2022-12-30 09:19:53 19

19 内容提要●热、应力和电子散热设计同步分析,让设计人员可以无缝利用ECAD和MCAD对机电系统进行多物理场仿真●融合FEM和CFD引擎,应对各种热完整性挑战——从芯片到封装,从电路板到完整的电子系统

2024-02-19 13:00:09 216

216

Cadence 与 Intel 代工厂合作开发并验证了一项集成的先进封装流程。该流程能利用嵌入式多晶粒互连桥接(EMIB)威廉希尔官方网站

来应对异构集成多芯粒架构不断增长的复杂性。

2024-03-11 11:48:05 210

210

电子发烧友App

电子发烧友App

评论