摘要:本文介绍了Dallas Semiconductor对传统8051微控制器的改进威廉希尔官方网站

,创造了引脚兼容的高性能替代产品,能够达到33 MIP的速度。除此之外,还包括多数据指针、扩展存储器寻址(达16MB)和闪存,大大提高的器件的速度和有效性。

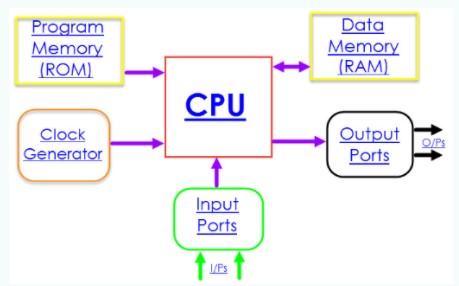

系统设计者都知道,微控制器是所有嵌入式系统的心脏—各种系统活动的策源地。过去18年来,Dallas Semiconductor (Maxim Integrated Products的全资子公司)对无处不在的8051微控制器进行了重新定义。也许,过去十年来对于微控制器的最大改进,表现在其执行指令的速度方面。我们的单周期处理器达到了振奋人心的性能目标—每机器周期一个时钟,目前为33百万指令每秒(MIPS)。基于这个内核,我们的安全型、网络型、和混合信号8051微控制器家族在功能集成和创新性方面始终为业界典范。

为什么将创新的微控制器家族建立在古老的8051指令集之上?道理很简单,因为它是世界范围内最为流行的8位微控制器架构之一。这种指令集简单易懂,深受嵌入式系统设计者的喜爱。许多指令可直接访问I/O引脚,便于迅速操作(位操作)外围设备。种类繁多的片内外设具有几乎无限种组合方式。此外,用于8051微控制器家族的开发工具随处可见,这样,你可以非常容易地,而且不需要花费很高成本,就可以着手一个应用的开发。

由于采用非易失SRAM威廉希尔官方网站 ,数据和程序存储器都可重新在系统编程,允许逐字节、运行中编程。而在一个标准的微控制器系统中,要重新编程就必须将程序存储器从系统中拿下来(EPROM),或者进行块擦除,擦除过程中要禁止存储器访问(flash)。基于非易失SRAM的微控制器的编程非常容易并且迅速,可利用PC或一个专用编程器通过串口对其进行编程。驻留于ROM的自举装载器直接将程序或数据下载到微控制器,实现快速调试或现场升级。

非易失SRAM独具特色的优点为系统固件的安全性提供了新的手段。由于自举装载器完全控制着向非易失SRAM的程序装载,我们采用一个40位或80位的加密密钥对地址和数据总线进行加密。任何装载到微控制器内的程序或数据在存入SRAM之前都自动进行了加密。这种加密手段可以防止黑客窃取微控制器中的程序或数据。指令运行期间,微控制器取出经过加密的操作码,在一个机器周期内完成解密并执行。由于采用了非易失SRAM,允许全速进行读/写访问,指令解密不会引起任何延迟。

这些安全特性在DS5250中达到了极致,这是一种安全型8051微控制器,广泛用于世界各地的金融终端和支付系统。这种抗攻击微控制器整合了一个4时钟机器周期内核,以及用于程序存储器加密的增强型三DES加密逻辑。另外,还增加了侵入探测和片内篡改检测器,一旦检测到有篡改发生便自动擦除存储器。一个内部的微探针屏蔽层可防止对晶片进行篡改。还有,非易失SRAM对于要求高度安全的应用来讲可谓是最佳选择。由于可以高速写入,微控制器能够迅速擦除机密信息和敏感数据,这一点胜出了任何其他类型的存储器。

DS5250是唯一一款既提供最高水准的安全性,又能全速运行每条指令的微控制器。

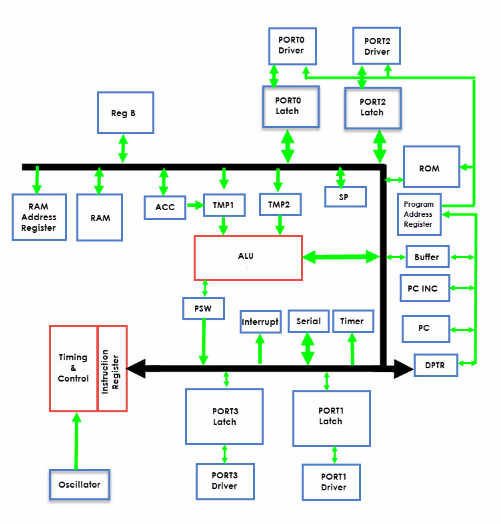

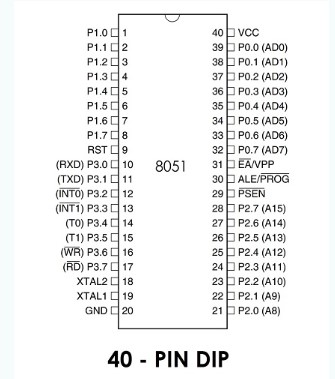

性能的瓶颈在于过时的、诞生于上个世纪七十年代的8051微控制器处理内核。尽管外部晶振的速度已接近40MHz,传统的8051仍然要求12个时钟才能运行一个机器周期。每条指令需要1到4个机器周期,这意味着执行一条指令就需要少则12多则48个时钟周期。这样,吞吐率被限制于仅3MIPS,即便是运行一串象NOP这样的单周期指令(图1)。

图1. 由于每机器周期所需时钟数的降低,相同指令集的性能提高了3倍以上(对比12时钟、4时钟和1时钟每机器周期)。

1991年,我们开始着手重新设计8051微控制器,以期获得性能上的突破。设计小组首先对传统8051的设计进行了分析。我们发现,原先的12时钟每机器周期架构中存在着巨大的浪费:多数指令被强制去执行哑周期。工程师们彻底重构了CPU,每个机器周期只需4个时钟而非12个。第二条内部数据总线消除了阻碍性能发挥的结构性瓶颈。高功率I/O驱动器提升了访问外部存储器时口线的转换速度。所有内置的外围设备,例如定时器和串行口,都运行于更高的时钟频率。不过,在此变革之路上的每一步,都有一条绝对不变的准则―指令集必须保持和8051指令集操作码的兼容性。

最终,一种全新的基于8051的微控制器诞生了,相比原来的8051核效率提升了三倍,相同的频率下,大多数指令的运行速度提高了三倍。除了内核效率提升以外,大多数器件的最高外部振荡频率也提高到了33MHz或40MHz。饱受古老、低速的8051困扰的系统设计者现在无需修改软件,就可轻易地将他们的系统升级到最高10MIPS的速度。

除了速度方面的改进以外,重新设计的内核也带来了另外一个好处:更低的功率消耗。基本物理法则告诉我们,数字电路的功率消耗正比于有开关动作的晶体管数量以及开关的速率(频率)。由于新的内核每机器周期使用更少的振荡周期,执行每条指令所需的能量比传统8051显著降低了。

另外,特殊的功率管理模式通过软件可配置的内部时钟分频器,可以临时性地降低微控制器的功耗。通过将机器周期速率由4时钟每机器周期降低到64或256时钟每机器周期,可进一步降低功耗。回切功能使器件在接收到一个外部中断或检测到一个串行口起始位后立即返回到除4模式。这个特性允许器件在工作较少时保持低功耗守候状态,必要时又可迅速恢复全速工作状态。图2显示了不同模式中的相对功率消耗。

图2. 在工作量降低期间,我们的功率管理模式消耗的电流比闲置模式还低,而且CPU仍处于活动状态。

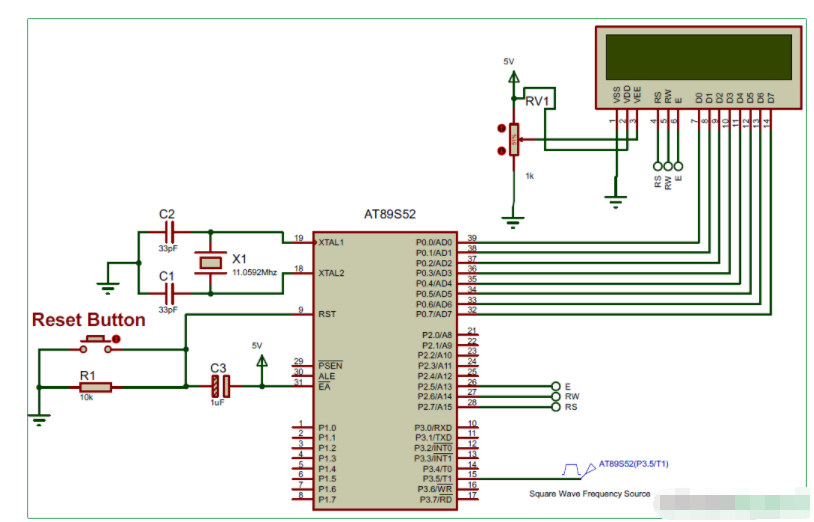

最终,我们推出了全新的DS89C430/DS89C450—―超高性能、每机器周期一个时钟的微控制器,运行速率高达33MIPS (图3)。这些器件突破了原有的性能障碍,以8位微控制器的价格,提供16位的性能。这些微控制器提供多种不同的总线寻址模式,允许用户按照特定应用要求,对处理器的工作进行优化。最为重要的是,它们保持了与8051指令集100%的兼容性,同时,又能够以更高的速度运行现有的8051应用,速度高出任何一种其它基于8051的微控制器。

图3. DS89C430 33MIPS的性能远超竞争对手。

除了闪电般快速的内核,DS89C430/DS89C450还整合了多达64kB可在系统编程的闪速存储器。驻留于ROM的自举装载器允许用户在任意时间对微控制器代码进行调整,使设计非常灵活。不同于其它使用专有或非标接口的微控制器,DS89C430的自举装载器可由标准PC,使用任何终端仿真软件,通过串行口进行操作。

有些设计者采用分区切换的办法来扩展寻址空间。I/O线被充作地址线使用,以牺牲部分I/O资源为代价换取更多存储空间。但这种做法有两个重要缺陷。首先,代码必须以64kB或更小的单位分段,这是一件很费时的工作,因为每次调整代码后都必须重新进行分段。第二,每一次代码跨段时都必须通过专门的软件流程去切换I/O线。由于这方面的软件开销,会使系统的总体性能有所下降。

更好的解决方案应该是给器件配备更宽的地址总线。DS80C400便是如此,它具有24位地址总线,可直接寻址16MB的程序存储器和16MB的数据存储器。而新功能的实现,并没有依靠8051指令集之外的新增操作码。提供两种总线模式,第一种页寻址模式采用了先进的自动分区切换威廉希尔官方网站 ,极大地加速了扩展存储器的访问,同时又保持了与传统8051编译器二进制码的兼容性。第二种连续模式可透明寻址整个16MB存储空间,但要求编译器能够产生24位地址所需的额外的操作数。更大的地址空间允许更大的程序以更高的速度运作,为微控制器开拓了更广的应用空间,例如大型的数学函数库、检索表、甚至是Java™虚拟机,后者已得到网络型微控制器DS80C390和DS80C400的支持,并成为微型因特网接口(TINI®)运行环境的一部分。

前进道路上的每一步都有一个必须遵循的条件―指令集必须保持与8051指令集操作码的兼容性。

DS89C430保持了与8051指令集100%的兼容性,因此它可直接运行原来的8051应用,而速度仍快于任何其他基于8051的微控制器。

这种操作的低效率在执行块拷贝操作时尤为突出,这种操作需要将数据从MOVX存储器中的某个位置转移到另一位置。在块拷贝操作中,单一数据指针必须兼作源地址和目的地址指针。在传统8051微控制器中,这种操作是一个复杂、多步骤的过程:

也许你已经注意到了,上述过程中几乎有一半的步骤,用来将单个数据指针在目标和源地址之间换来换去,这会妨碍整体性能的发挥。解决方案是增加第二个数据指针,为源和目标指针分配专门的寄存器。有了第二个数据指针,很多数据操作可由硬件完成,降低了软件开销。双数据指针可独立访问,通过专门的数据指针选择位可以选择执行MOVX指令时,当前活动的数据指针。采用双数据指针,同样的块拷贝操作所需的步骤要少很多:

只需一次初始化:

图4. 双数据指针提高了块拷贝操作的速度。

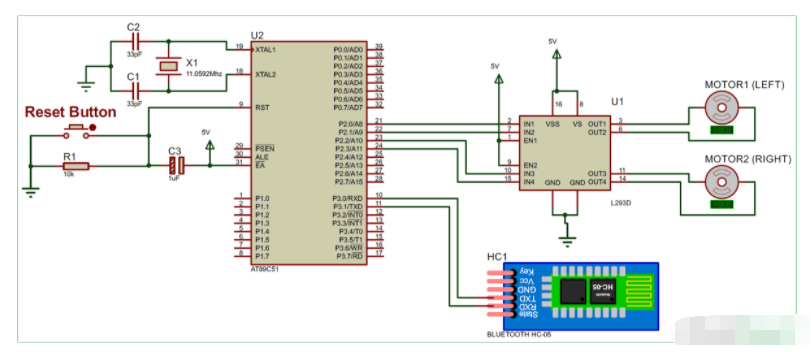

但是,有竞真力的设计不仅仅要求速度。更复杂的应用需要更大的程序空间,因此,我们正在将直接替换原8051的微控制器系列扩充为64kB闪存。我们的新产品流水线正在将更多的外设设计进来,以便提升嵌入式系统的能力,同时降低板上空间需求。网络型微控制器具有一些更先进的功能,包括CAN,以太网,及1-Wire®等多层次组网能力。安全微控制器具有硬件实现的数学加速器,用于公钥加密系统,并在检测到有篡改发生时,迅速删除密钥。混合信号微控制器能够处理来自真实世界的信号,用来实现更好的终端设备。

我们对于微控制器性能的追求超越了8051内核。我们的一个新的系列,MAXQ® 16位RISC微控制器达到了更高的性能-功耗比。引领我们到达此目标的途径是单周期指令。单周期指令增加了指令带宽,从而可提供更高的性能,而且,有可能通过降低时钟频率来降低功耗。除了长跳转/长调用和某些扩展寄存器的访问外,所有MAXQ指令都在单个时钟周期内执行。虽然许多RISC微控制器声称支持单周期指令,但事实通常是只有一部分指令或寻址模式是单周期的。在MAXQ中,绝大部分是单周期指令。

另外,MAXQ架构提高了时钟周期的利用率,因为其单周期操作并未依赖指令流水线(常见于许多RISC微控制器)。MAXQ指令的译码和执行硬件是如此之简单(且快速),以致它们可以和取指在同一个时钟周期内完成,且对最高工作频率的影响很小。为了说明取消指令流水线的优点,我们来考察一个流水线结构的普通RISC CPU。当遇到程序分支时,CPU需要一个或更多时钟周期(因流水线深度而异)来将程序转向目标分支地址,抛弃已取得的指令。显然,将时钟周期用在抛弃指令(而非执行指令)上面是一种浪费且令人不快的做法,因为它降低了性能且增加了功耗。尽管这种操作令人不快,CPU窃取时钟来重装流水线仍然是这种架构不可避免的一个瑕疵。MAXQ架构区别于其他8位和16位RISC微控制器的一个显著特点就是,单周期指令的执行不依赖于指令流水线(也就避免了它所带来的时钟周期浪费问题)。

有关如何以最低的功耗获取最高的性能方面的更多信息,参见白皮书“Teaching Old Dogs New Tricks: Improving the Power Efficiency of 8051-Based Designs” (English only)。

系统设计者都知道,微控制器是所有嵌入式系统的心脏—各种系统活动的策源地。过去18年来,Dallas Semiconductor (Maxim Integrated Products的全资子公司)对无处不在的8051微控制器进行了重新定义。也许,过去十年来对于微控制器的最大改进,表现在其执行指令的速度方面。我们的单周期处理器达到了振奋人心的性能目标—每机器周期一个时钟,目前为33百万指令每秒(MIPS)。基于这个内核,我们的安全型、网络型、和混合信号8051微控制器家族在功能集成和创新性方面始终为业界典范。

为什么将创新的微控制器家族建立在古老的8051指令集之上?道理很简单,因为它是世界范围内最为流行的8位微控制器架构之一。这种指令集简单易懂,深受嵌入式系统设计者的喜爱。许多指令可直接访问I/O引脚,便于迅速操作(位操作)外围设备。种类繁多的片内外设具有几乎无限种组合方式。此外,用于8051微控制器家族的开发工具随处可见,这样,你可以非常容易地,而且不需要花费很高成本,就可以着手一个应用的开发。

安全及保密

1987年,Dallas Semiconductor/Maxim推出了DS5000T,一款独立开发的,基于8051指令集和功能集的新型微控制器。为了提供新的性能和优势,工程师们将设计建立在非易失SRAM威廉希尔官方网站 之上,而非传统的EPROM。仰赖其居于领导地位的低功耗威廉希尔官方网站 ,存储器分区和电池备份电路被直接集成到微控制器晶片上。这种系统的主要优势在于其速度。其他类型的非易失存储器的写操作通常很慢,但是非易失SRAM能够在很高的速度下,在单个周期内读出和写入。这对于高速、非易失数据采集应用来讲非常理想,这些应用常常要求捕捉实时数据。配合一个外部SRAM和电池,就构成完整的微控制器系统,具有多达64kB的非易失程序和数据存储空间。由于采用非易失SRAM威廉希尔官方网站 ,数据和程序存储器都可重新在系统编程,允许逐字节、运行中编程。而在一个标准的微控制器系统中,要重新编程就必须将程序存储器从系统中拿下来(EPROM),或者进行块擦除,擦除过程中要禁止存储器访问(flash)。基于非易失SRAM的微控制器的编程非常容易并且迅速,可利用PC或一个专用编程器通过串口对其进行编程。驻留于ROM的自举装载器直接将程序或数据下载到微控制器,实现快速调试或现场升级。

非易失SRAM独具特色的优点为系统固件的安全性提供了新的手段。由于自举装载器完全控制着向非易失SRAM的程序装载,我们采用一个40位或80位的加密密钥对地址和数据总线进行加密。任何装载到微控制器内的程序或数据在存入SRAM之前都自动进行了加密。这种加密手段可以防止黑客窃取微控制器中的程序或数据。指令运行期间,微控制器取出经过加密的操作码,在一个机器周期内完成解密并执行。由于采用了非易失SRAM,允许全速进行读/写访问,指令解密不会引起任何延迟。

这些安全特性在DS5250中达到了极致,这是一种安全型8051微控制器,广泛用于世界各地的金融终端和支付系统。这种抗攻击微控制器整合了一个4时钟机器周期内核,以及用于程序存储器加密的增强型三DES加密逻辑。另外,还增加了侵入探测和片内篡改检测器,一旦检测到有篡改发生便自动擦除存储器。一个内部的微探针屏蔽层可防止对晶片进行篡改。还有,非易失SRAM对于要求高度安全的应用来讲可谓是最佳选择。由于可以高速写入,微控制器能够迅速擦除机密信息和敏感数据,这一点胜出了任何其他类型的存储器。

DS5250是唯一一款既提供最高水准的安全性,又能全速运行每条指令的微控制器。

高速度,低功耗

8051处理器核自从诞生之日起(二十世纪七十年代末到八十年代)就基本停滞不前,而嵌入式系统却并非如此。通过增加新的软件特性和外围设备,系统设计者不断地对其基于8051的应用进行了改进和升级。这种“功能蔓延”将现有的8051性能推向了极限。不幸的是,对于8051内核的改进却没有跟得上,看起来,系统设计者似乎不得不转向其他的处理器,并花费昂贵的代价去重新设计和更新他们的系统。性能的瓶颈在于过时的、诞生于上个世纪七十年代的8051微控制器处理内核。尽管外部晶振的速度已接近40MHz,传统的8051仍然要求12个时钟才能运行一个机器周期。每条指令需要1到4个机器周期,这意味着执行一条指令就需要少则12多则48个时钟周期。这样,吞吐率被限制于仅3MIPS,即便是运行一串象NOP这样的单周期指令(图1)。

图1. 由于每机器周期所需时钟数的降低,相同指令集的性能提高了3倍以上(对比12时钟、4时钟和1时钟每机器周期)。

1991年,我们开始着手重新设计8051微控制器,以期获得性能上的突破。设计小组首先对传统8051的设计进行了分析。我们发现,原先的12时钟每机器周期架构中存在着巨大的浪费:多数指令被强制去执行哑周期。工程师们彻底重构了CPU,每个机器周期只需4个时钟而非12个。第二条内部数据总线消除了阻碍性能发挥的结构性瓶颈。高功率I/O驱动器提升了访问外部存储器时口线的转换速度。所有内置的外围设备,例如定时器和串行口,都运行于更高的时钟频率。不过,在此变革之路上的每一步,都有一条绝对不变的准则―指令集必须保持和8051指令集操作码的兼容性。

最终,一种全新的基于8051的微控制器诞生了,相比原来的8051核效率提升了三倍,相同的频率下,大多数指令的运行速度提高了三倍。除了内核效率提升以外,大多数器件的最高外部振荡频率也提高到了33MHz或40MHz。饱受古老、低速的8051困扰的系统设计者现在无需修改软件,就可轻易地将他们的系统升级到最高10MIPS的速度。

除了速度方面的改进以外,重新设计的内核也带来了另外一个好处:更低的功率消耗。基本物理法则告诉我们,数字电路的功率消耗正比于有开关动作的晶体管数量以及开关的速率(频率)。由于新的内核每机器周期使用更少的振荡周期,执行每条指令所需的能量比传统8051显著降低了。

另外,特殊的功率管理模式通过软件可配置的内部时钟分频器,可以临时性地降低微控制器的功耗。通过将机器周期速率由4时钟每机器周期降低到64或256时钟每机器周期,可进一步降低功耗。回切功能使器件在接收到一个外部中断或检测到一个串行口起始位后立即返回到除4模式。这个特性允许器件在工作较少时保持低功耗守候状态,必要时又可迅速恢复全速工作状态。图2显示了不同模式中的相对功率消耗。

图2. 在工作量降低期间,我们的功率管理模式消耗的电流比闲置模式还低,而且CPU仍处于活动状态。

超越33MIPS

Dallas Semiconductor/Maxim于1997年开始设计一个新的内核,以获得更高的性能。基于8051的应用在不断发展,用户在呼唤更高的性能。设计团队将他们的目标锁定在性能的顶峰:运行8051指令集,但是每机器周期仅一个时钟的全新微控制器。采用高度并行架构和新的制造工艺,一种引脚对引脚兼容,直接替换原有8051的设计问世了。最终,我们推出了全新的DS89C430/DS89C450—―超高性能、每机器周期一个时钟的微控制器,运行速率高达33MIPS (图3)。这些器件突破了原有的性能障碍,以8位微控制器的价格,提供16位的性能。这些微控制器提供多种不同的总线寻址模式,允许用户按照特定应用要求,对处理器的工作进行优化。最为重要的是,它们保持了与8051指令集100%的兼容性,同时,又能够以更高的速度运行现有的8051应用,速度高出任何一种其它基于8051的微控制器。

图3. DS89C430 33MIPS的性能远超竞争对手。

除了闪电般快速的内核,DS89C430/DS89C450还整合了多达64kB可在系统编程的闪速存储器。驻留于ROM的自举装载器允许用户在任意时间对微控制器代码进行调整,使设计非常灵活。不同于其它使用专有或非标接口的微控制器,DS89C430的自举装载器可由标准PC,使用任何终端仿真软件,通过串行口进行操作。

韩信用兵,多多益善

如果程序员没有足够的存储器地址空间可以支配的话,速度方面的优势将无从施展。传统8051采用16位存储器总线,使存储器空间限制在64kB以内。对于有些应用,这样有限的存储空间已经足够了。但是随着应用的升级,代码的复杂性和规模迅速膨胀,我们意识到,这类应用需要一个解决方案,同时还要尽可能保持与8051的兼容性。有些设计者采用分区切换的办法来扩展寻址空间。I/O线被充作地址线使用,以牺牲部分I/O资源为代价换取更多存储空间。但这种做法有两个重要缺陷。首先,代码必须以64kB或更小的单位分段,这是一件很费时的工作,因为每次调整代码后都必须重新进行分段。第二,每一次代码跨段时都必须通过专门的软件流程去切换I/O线。由于这方面的软件开销,会使系统的总体性能有所下降。

更好的解决方案应该是给器件配备更宽的地址总线。DS80C400便是如此,它具有24位地址总线,可直接寻址16MB的程序存储器和16MB的数据存储器。而新功能的实现,并没有依靠8051指令集之外的新增操作码。提供两种总线模式,第一种页寻址模式采用了先进的自动分区切换威廉希尔官方网站 ,极大地加速了扩展存储器的访问,同时又保持了与传统8051编译器二进制码的兼容性。第二种连续模式可透明寻址整个16MB存储空间,但要求编译器能够产生24位地址所需的额外的操作数。更大的地址空间允许更大的程序以更高的速度运作,为微控制器开拓了更广的应用空间,例如大型的数学函数库、检索表、甚至是Java™虚拟机,后者已得到网络型微控制器DS80C390和DS80C400的支持,并成为微型因特网接口(TINI®)运行环境的一部分。

前进道路上的每一步都有一个必须遵循的条件―指令集必须保持与8051指令集操作码的兼容性。

成倍提升性能的数据指针设计

为了避免产生新的性能瓶颈,有必要对芯片的各个方面都进行长远的改进。其中最为重要的改进之一是针对MOVX数据存储器访问的改进。数据存储器的操作对于原8051来讲是一件很麻烦的事情。要访问MOVX存储器中的单个字节,首先需要花费数个周期装载一个16位数据指针,然后才能对目标地址进行读写操作。DS89C430保持了与8051指令集100%的兼容性,因此它可直接运行原来的8051应用,而速度仍快于任何其他基于8051的微控制器。

这种操作的低效率在执行块拷贝操作时尤为突出,这种操作需要将数据从MOVX存储器中的某个位置转移到另一位置。在块拷贝操作中,单一数据指针必须兼作源地址和目的地址指针。在传统8051微控制器中,这种操作是一个复杂、多步骤的过程:

- 装载源地址到数据指针。

- 递增或调整数据指针指向下一单元。

- 从MOVX存储器取数据到累加器。

- 保存源地址到寄存器。

- 装载目标地址到数据指针。

- 递增或调整数据指针指向下一单元。

- 数据由累加器写入MOVX存储器。

- 保存目标地址到寄存器。

也许你已经注意到了,上述过程中几乎有一半的步骤,用来将单个数据指针在目标和源地址之间换来换去,这会妨碍整体性能的发挥。解决方案是增加第二个数据指针,为源和目标指针分配专门的寄存器。有了第二个数据指针,很多数据操作可由硬件完成,降低了软件开销。双数据指针可独立访问,通过专门的数据指针选择位可以选择执行MOVX指令时,当前活动的数据指针。采用双数据指针,同样的块拷贝操作所需的步骤要少很多:

只需一次初始化:

- 第一数据指针初始化为源地址。

- 第二数据指针初始化为目标地址。

- 取数据到累加器。

- 递增或调整第一数据指针指向下一单元。

- 选择第二数据指针。

- 数据由累加器写入MOVX存储器。

- 递增或调整数据指针指向下一单元。

图4. 双数据指针提高了块拷贝操作的速度。

前景展望

随着应用越来越高的速度要求,Maxim正在努力工作以超越一个又一个性能极限。无论是其更快的堆栈访问速度、扩展的寻址空间,抑或是基本处理速度,我们的微控制器设计终能满足嵌入式系统设计者的各种要求。但是,有竞真力的设计不仅仅要求速度。更复杂的应用需要更大的程序空间,因此,我们正在将直接替换原8051的微控制器系列扩充为64kB闪存。我们的新产品流水线正在将更多的外设设计进来,以便提升嵌入式系统的能力,同时降低板上空间需求。网络型微控制器具有一些更先进的功能,包括CAN,以太网,及1-Wire®等多层次组网能力。安全微控制器具有硬件实现的数学加速器,用于公钥加密系统,并在检测到有篡改发生时,迅速删除密钥。混合信号微控制器能够处理来自真实世界的信号,用来实现更好的终端设备。

我们对于微控制器性能的追求超越了8051内核。我们的一个新的系列,MAXQ® 16位RISC微控制器达到了更高的性能-功耗比。引领我们到达此目标的途径是单周期指令。单周期指令增加了指令带宽,从而可提供更高的性能,而且,有可能通过降低时钟频率来降低功耗。除了长跳转/长调用和某些扩展寄存器的访问外,所有MAXQ指令都在单个时钟周期内执行。虽然许多RISC微控制器声称支持单周期指令,但事实通常是只有一部分指令或寻址模式是单周期的。在MAXQ中,绝大部分是单周期指令。

另外,MAXQ架构提高了时钟周期的利用率,因为其单周期操作并未依赖指令流水线(常见于许多RISC微控制器)。MAXQ指令的译码和执行硬件是如此之简单(且快速),以致它们可以和取指在同一个时钟周期内完成,且对最高工作频率的影响很小。为了说明取消指令流水线的优点,我们来考察一个流水线结构的普通RISC CPU。当遇到程序分支时,CPU需要一个或更多时钟周期(因流水线深度而异)来将程序转向目标分支地址,抛弃已取得的指令。显然,将时钟周期用在抛弃指令(而非执行指令)上面是一种浪费且令人不快的做法,因为它降低了性能且增加了功耗。尽管这种操作令人不快,CPU窃取时钟来重装流水线仍然是这种架构不可避免的一个瑕疵。MAXQ架构区别于其他8位和16位RISC微控制器的一个显著特点就是,单周期指令的执行不依赖于指令流水线(也就避免了它所带来的时钟周期浪费问题)。

有关如何以最低的功耗获取最高的性能方面的更多信息,参见白皮书“Teaching Old Dogs New Tricks: Improving the Power Efficiency of 8051-Based Designs” (English only)。

电子发烧友App

电子发烧友App

评论