资料介绍

描述

这是一个由 5 部分组成的博客:

第 2 部分:在 Spartan 6 FPGA 上使用 Xilinx ISE 的组合逻辑

第 3 部分:在 Cyclone-IV FPGA 上使用 Quartus Prime 的顺序逻辑

第 4 部分:在 Artix-7 FPGA 上使用 Vivado 的组合逻辑与顺序逻辑

第 5 部分:最终项目 - DE0 Nano 开发板上的 Pong 游戏

目标:

比较和分析使用在 Artix-7 FPGA 上实现的组合逻辑和顺序逻辑的移位器的性能

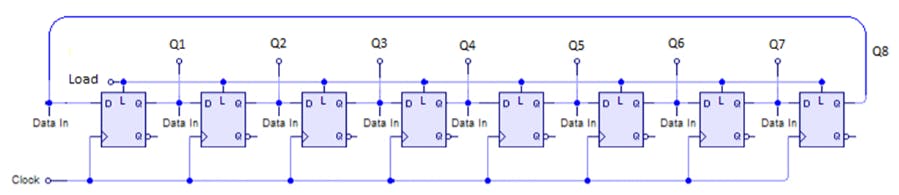

顺序逻辑:移位寄存器

我们都知道什么是移位寄存器,以及为什么要使用它们——对寄存器中的位进行移位吗?

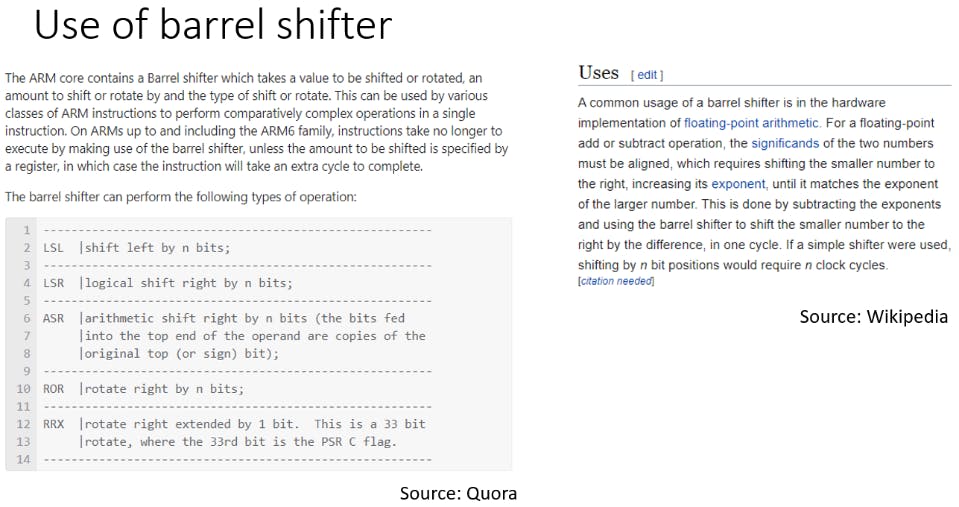

但是 CPU 或微控制器内部的应用程序非常广泛,并且在算术和逻辑单元中发挥着至关重要的作用,尤其是在如今的 ARM 处理器中。

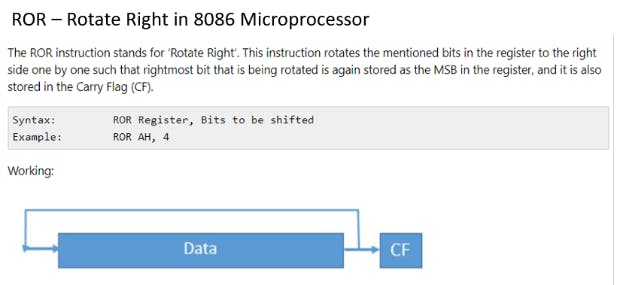

下面给出的设计专门用于右移。但为什么?此操作在老式8086微处理器中用于实现 ROR 指令。

8 位移位寄存器设计:

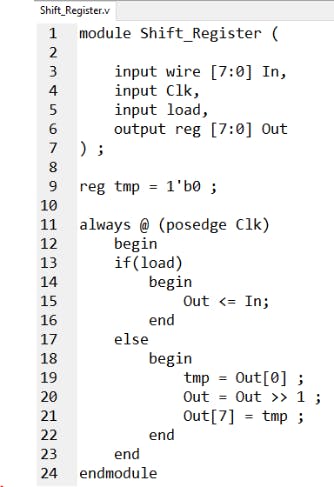

Verilog 实现:

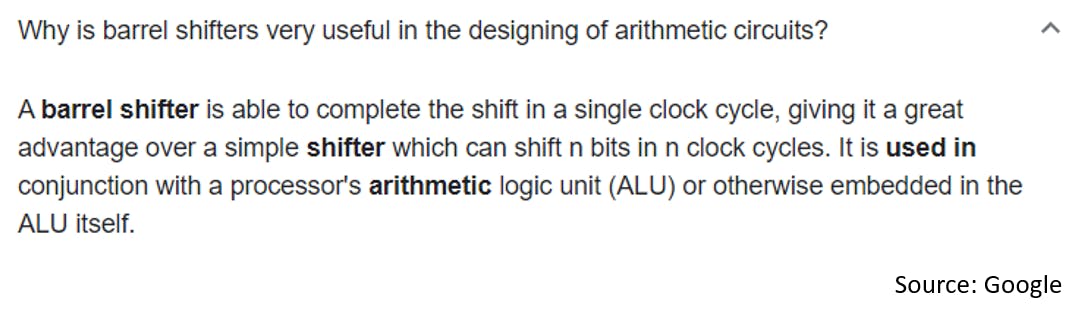

有没有其他方法可以移动位?

- 是的,桶形移位器。

组合逻辑:桶形移位器

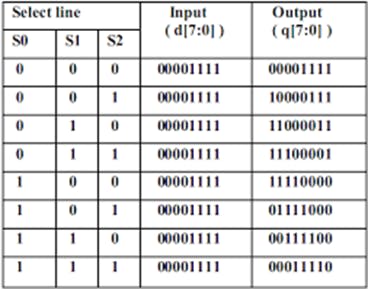

真值表:

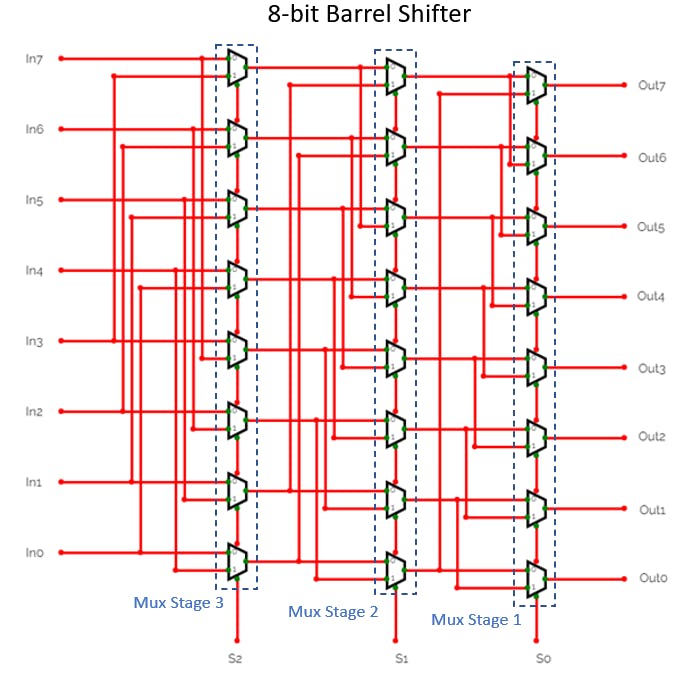

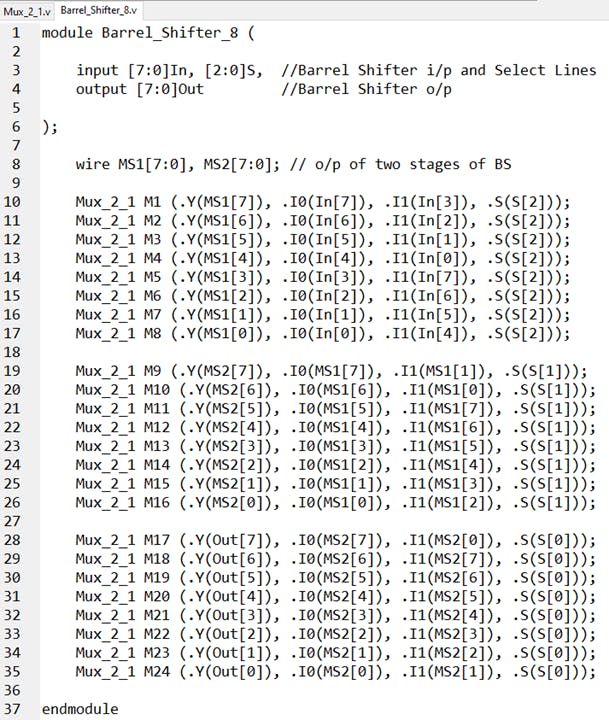

在这篇博客中,我将讨论使用多路复用器的 8 位桶形移位器的设计和实现。

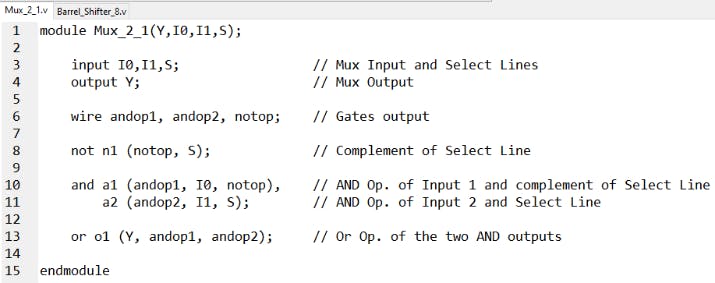

我要遵循的建模是 Verilog HDL 中的结构设计。

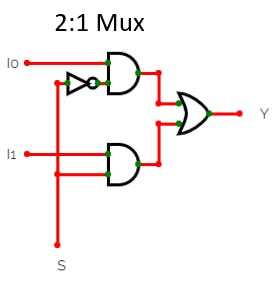

首先,让我们设计一个 2:1 Mux

结构模型中 2:1 Mux 的 Verilog 代码非常简单,我们有 2 个与门、1 个非门和 1 个或门。

除了常规的输入和输出外,还为门输出声明了三根线,并根据结构进行连接。

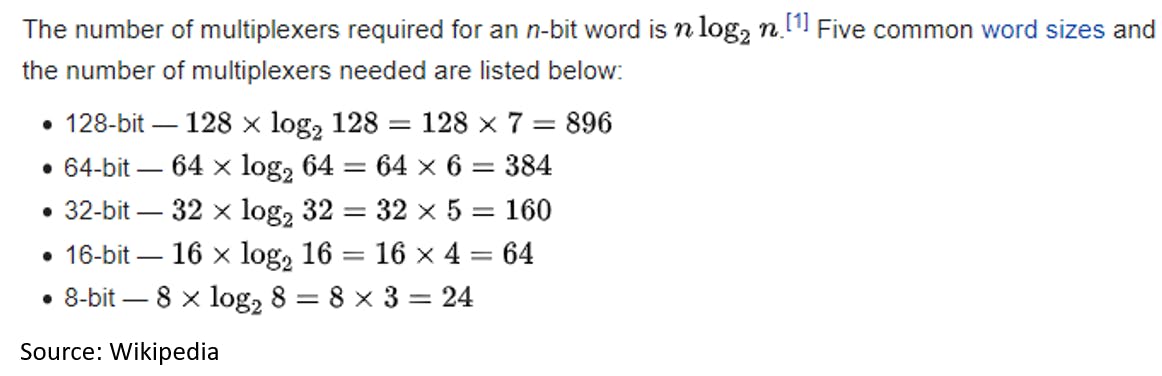

8位桶形移位器的设计:

通过使用结构设计,我们可以确保设计以我们想要的方式实现。

Verilog 实现:

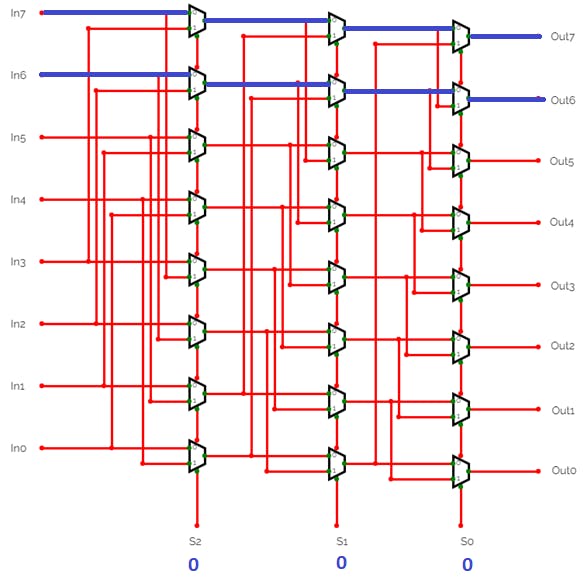

桶形移位器的工作:

这就是桶形移位器如何根据选择线移动位。

在 Artix-7 FPGA 上的实现:

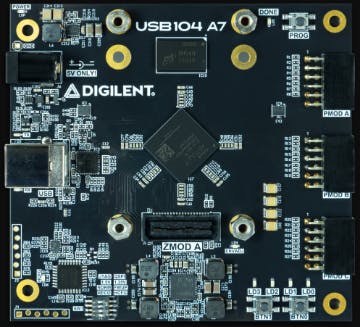

我将使用 USB104-A7 FPGA 开发板来实现。这是几个月前的路试。在此处阅读评论:USB104 A7:Artix-7 FPGA 开发板 - 评论

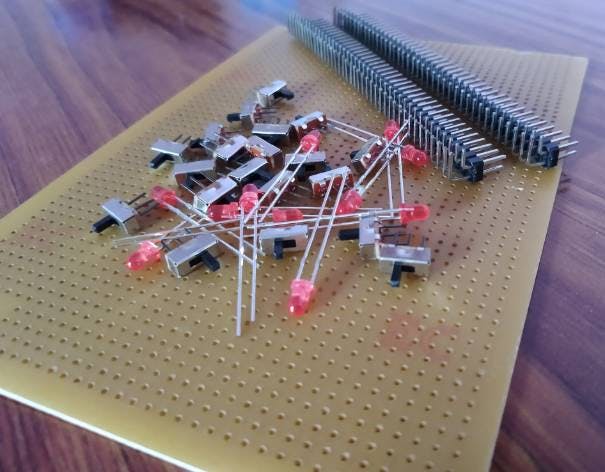

定制 Pmod 的制作:

由于按钮和 LED 等用户 I/O 外设非常少,因此要制造定制 Pmod(外设模块)以实现数字设计。

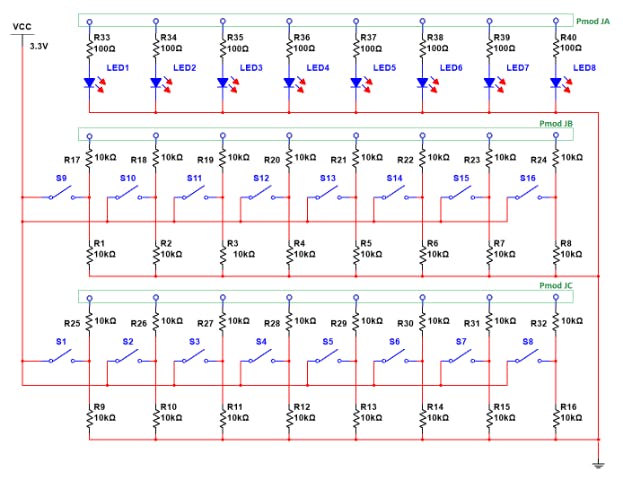

让我们看一下制造的示意图。

使用 NI Multisim 进行的设计:

从原理图中可以看出,使用 10k 电阻器将用于上拉和下拉目的。

由于已经有一个 200 欧姆的电阻串联到 Pmod GPIO 上,以防止意外将输入驱动为输出时损坏 FPGA,

仅 100 欧姆电阻与 LED 串联使用。所有开关均处于高电平有效。电路图如下:

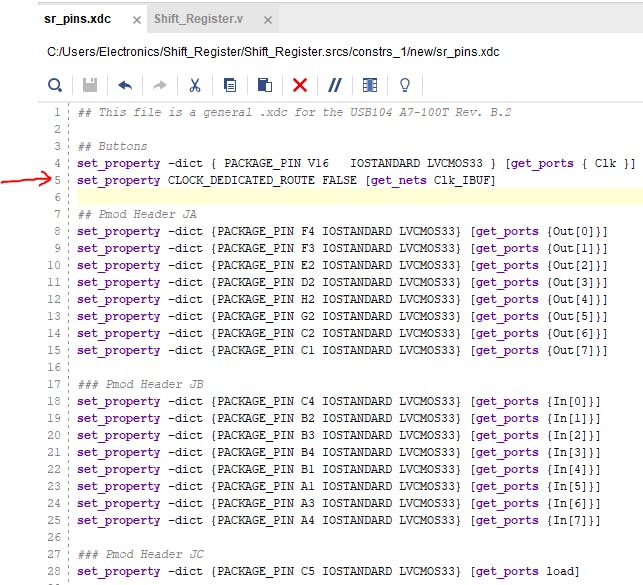

这是上面制作的 Pmod 的一般约束文件:

## Pmod Header JA

#set_property -dict { PACKAGE_PIN F4 IOSTANDARD LVCMOS33 } [get_ports { led[0] }]; #IO_L13P_T2_MRCC_35 Sch=ja[1]

#set_property -dict { PACKAGE_PIN F3 IOSTANDARD LVCMOS33 } [get_ports { led[1] }]; #IO_L13N_T2_MRCC_35 Sch=ja[2]

#set_property -dict { PACKAGE_PIN E2 IOSTANDARD LVCMOS33 } [get_ports { led[2] }]; #IO_L14P_T2_SRCC_35 Sch=ja[3]

#set_property -dict { PACKAGE_PIN D2 IOSTANDARD LVCMOS33 } [get_ports { led[3] }]; #IO_L14N_T2_SRCC_35 Sch=ja[4]

#set_property -dict { PACKAGE_PIN H2 IOSTANDARD LVCMOS33 } [get_ports { led[4] }]; #IO_L15P_T2_DQS_35 Sch=ja[7]

#set_property -dict { PACKAGE_PIN G2 IOSTANDARD LVCMOS33 } [get_ports { led[5] }]; #IO_L15N_T2_DQS_35 Sch=ja[8]

#set_property -dict { PACKAGE_PIN C2 IOSTANDARD LVCMOS33 } [get_ports { led[6] }]; #IO_L16P_T2_35 Sch=ja[9]

#set_property -dict { PACKAGE_PIN C1 IOSTANDARD LVCMOS33 } [get_ports { led[7] }]; #IO_L16N_T2_35 Sch=ja[10]

### Pmod Header JB

#set_property -dict { PACKAGE_PIN C4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[0] }]; #IO_L7P_T1_AD6P_35 Sch=jb[1]

#set_property -dict { PACKAGE_PIN B2 IOSTANDARD LVCMOS33 } [get_ports { sw_b[1] }]; #IO_L10N_T1_AD15N_35 Sch=jb[2]

#set_property -dict { PACKAGE_PIN B3 IOSTANDARD LVCMOS33 } [get_ports { sw_b[2] }]; #IO_L10P_T1_AD15P_35 Sch=jb[3]

#set_property -dict { PACKAGE_PIN B4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[3] }]; #IO_L7N_T1_AD6N_35 Sch=jb[4]

#set_property -dict { PACKAGE_PIN B1 IOSTANDARD LVCMOS33 } [get_ports { sw_b[4] }]; #IO_L9P_T1_DQS_AD7P_35 Sch=jb[7]

#set_property -dict { PACKAGE_PIN A1 IOSTANDARD LVCMOS33 } [get_ports { sw_b[5] }]; #IO_L9N_T1_DQS_AD7N_35 Sch=jb[8]

#set_property -dict { PACKAGE_PIN A3 IOSTANDARD LVCMOS33 } [get_ports { sw_b[6] }]; #IO_L8N_T1_AD14N_35 Sch=jb[9]

#set_property -dict { PACKAGE_PIN A4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[7] }]; #IO_L8P_T1_AD14P_35 Sch=jb[10]

### Pmod Header JC

#set_property -dict { PACKAGE_PIN C5 IOSTANDARD LVCMOS33 } [get_ports { sw_a[0] }]; #IO_L1N_T0_AD4N_35 Sch=jc[1]

#set_property -dict { PACKAGE_PIN C6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[1] }]; #IO_L1P_T0_AD4P_35 Sch=jc[2]

#set_property -dict { PACKAGE_PIN B6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[2] }]; #IO_L2N_T0_AD12N_35 Sch=jc[3]

#set_property -dict { PACKAGE_PIN C7 IOSTANDARD LVCMOS33 } [get_ports { sw_a[3] }]; #IO_L4N_T0_35 Sch=jc[4]

#set_property -dict { PACKAGE_PIN A5 IOSTANDARD LVCMOS33 } [get_ports { sw_a[4] }]; #IO_L3N_T0_DQS_AD5N_35 Sch=jc[7]

#set_property -dict { PACKAGE_PIN A6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[5] }]; #IO_L3P_T0_DQS_AD5P_35 Sch=jc[8]

#set_property -dict { PACKAGE_PIN B7 IOSTANDARD LVCMOS33 } [get_ports { sw_a[6] }]; #IO_L2P_T0_AD12P_35 Sch=jc[9]

#set_property -dict { PACKAGE_PIN D8 IOSTANDARD LVCMOS33 } [get_ports { sw_a[7] }]; #IO_L4P_T0_35 Sch=jc[10]

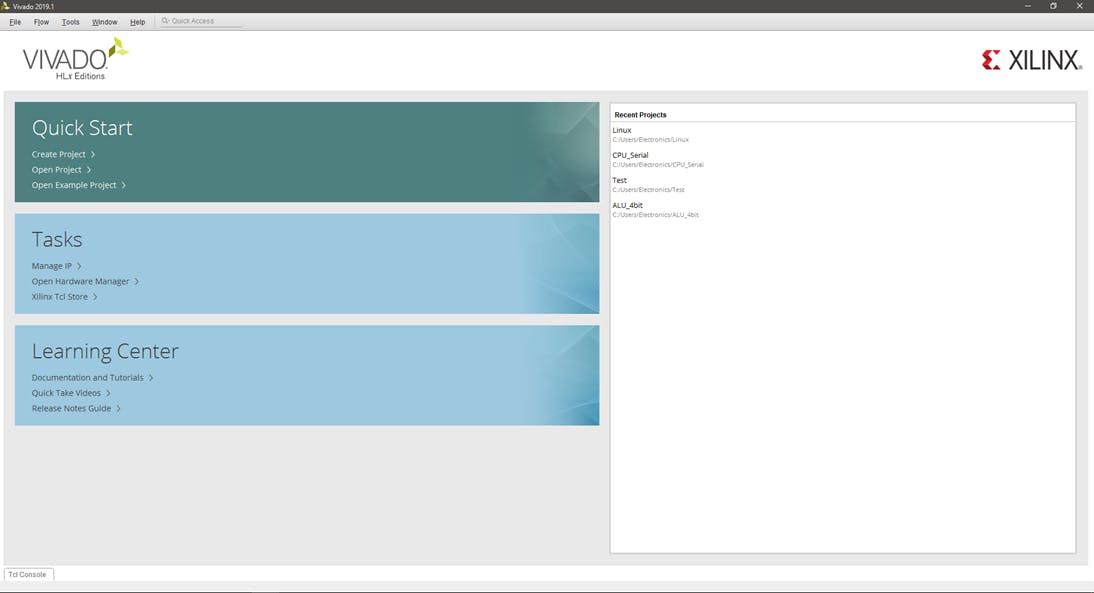

Vivado 入门:

如果您计划使用 FPGA 板上的按钮,请确保在移位寄存器项目的约束文件中添加命令,因为由于时钟专用路由错误,实现将无法完成。

Artix-7 FPGA 上的 8 位移位寄存器:

Artix-7 FPGA 上的 8 位桶形移位器:

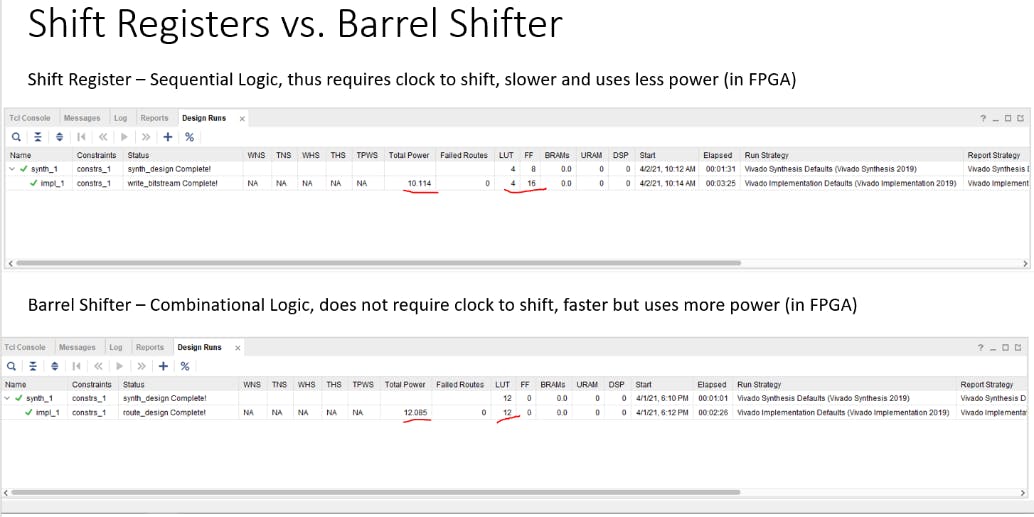

实施后的最终比较:

谢谢阅读!

- XILINX ARTIX7系列FPGA芯片产品目录 27次下载

- Artix-7 FPGA数据表下载 10次下载

- FPGA时序逻辑和组合逻辑的入门基础教程 12次下载

- Xilinx 7系列FPGA可配置逻辑块的用户指南 6次下载

- 组合逻辑电路和时序逻辑电路的学习课件免费下载 31次下载

- 组合逻辑电路的学习教程课件免费下载 15次下载

- XA ARTIX-7 FPGA的数据手册免费下载 8次下载

- XA Artix-7 FPGA芯片的选型手册免费下载 17次下载

- Multisim在组合逻辑电路设计中的常用元件和详细作用分析 10次下载

- 组合逻辑电路 33次下载

- 组合逻辑设计实例_国外 24次下载

- 组合逻辑电路设计基础 0次下载

- 组合逻辑电路电子教案 0次下载

- 组合逻辑电路设计实验 0次下载

- 组合逻辑电路.ppt

- 组合逻辑电路之与或逻辑 1146次阅读

- 组合逻辑电路和时序逻辑电路的区别和联系 6240次阅读

- 组合逻辑电路的分析和设计 2980次阅读

- 组合逻辑生成的时钟有哪些危害 3992次阅读

- 什么是组合逻辑电路 如何使用verilog描述组合逻辑电路 5630次阅读

- FPGA电路组合逻辑设计中的毛刺如何解决 3529次阅读

- digilent Nexys 4:Artix-7 FPGA训练板介绍 7951次阅读

- xilinx7系列FPGA的7种逻辑代码配置模式 2928次阅读

- 采用Artix-7 XCA75T FPGA的高速多通道数字转换器 2480次阅读

- 组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别 9.2w次阅读

- 组合逻辑电路实验原理 6.5w次阅读

- 组合逻辑电路设计步骤详解(教程) 12.1w次阅读

- 组合逻辑电路的特点详解 3.8w次阅读

- FPGA中组合逻辑和时序逻辑的区别 8773次阅读

- 什么是组合逻辑电路,组合逻辑电路的基本特点和种类详解 7.4w次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论