资料介绍

描述

介绍

安全哈希算法 (SHA-256) 是一种加密哈希函数,用于保护密码或网站服务器等安全性。它的一个著名用途是比特币的工作量证明,它基于 SHA256 算法来验证交易。

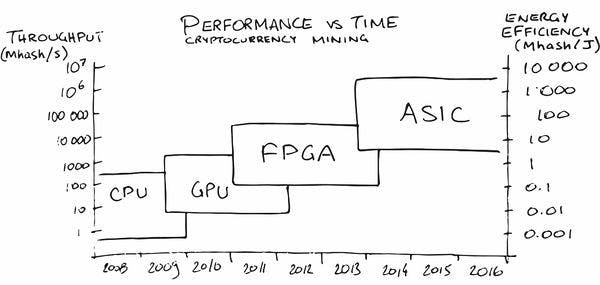

我想很多人会听说 GPU 被用于挖矿,因为 GPU 更适合哈希算法所需的数字运算。但是,您知道吗,可以使用 FPGA 完成定制化程度更高的加速?通过配置 FPGA 以在硬件中加速它,它的性能甚至会比 GPU 更高。事实上,比特币矿工早在 2011 年就开始使用 FPGA 进行挖矿。

如今,挖比特币的复杂性越来越高,FPGA 挖矿可能不再有利可图。然而,我们可以将其作为一个有用的案例研究来了解如何使用 Xilinx FPGA 轻松完成加速。也许下次当我们看到另一个潜在的算法加速用例时,我们就会知道该怎么做。

开发流程总结

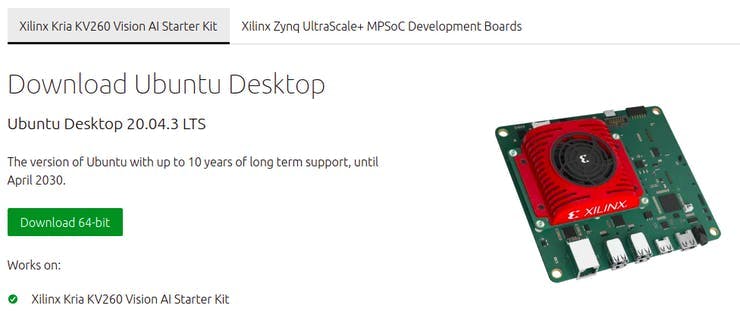

我们将使用 Xilinx Kria KV260 的硬件套件以及新发布的 Ubuntu 20.04 LTS 操作系统。我们将安装 PYNQ,以便我们可以从 Python notebook 获得硬件加速的好处。

在我们的 PC 上,我们将使用 Vitis HLS 将开源 C 代码实现转换为硬件 IP 模块。之后,Vivado 用于创建与处理器的连接并生成比特流。

最后,我们将比特流传输到 Xilinx Kria 并在 PYNQ 环境中对性能增益进行基准测试。

设置 SD 卡映像

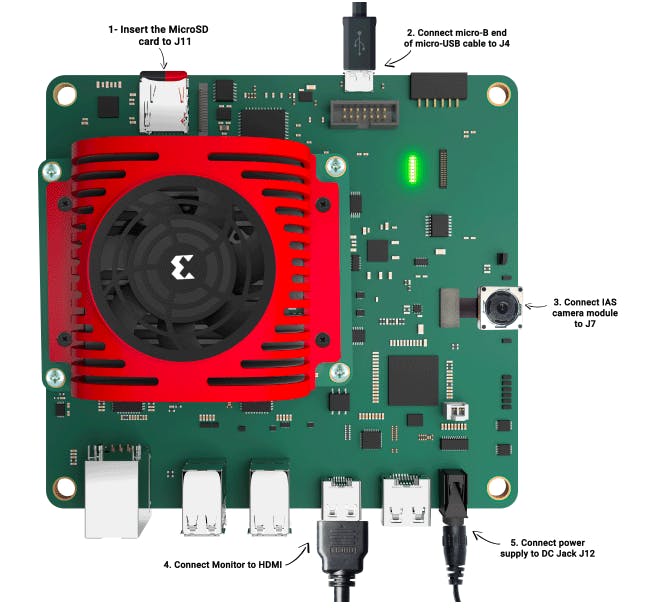

首先我们需要为 Kria KV260 Vision AI Starter Kit 准备 SD 卡。

包装盒中提供了一张 16GB 的 SD 卡,但我建议至少使用 32GB的,因为设置可能会超过 16GB 的空间。

我们将使用 Ubuntu 20.04.3 LTS 下载。从网站下载图像并将其保存在您的计算机上。

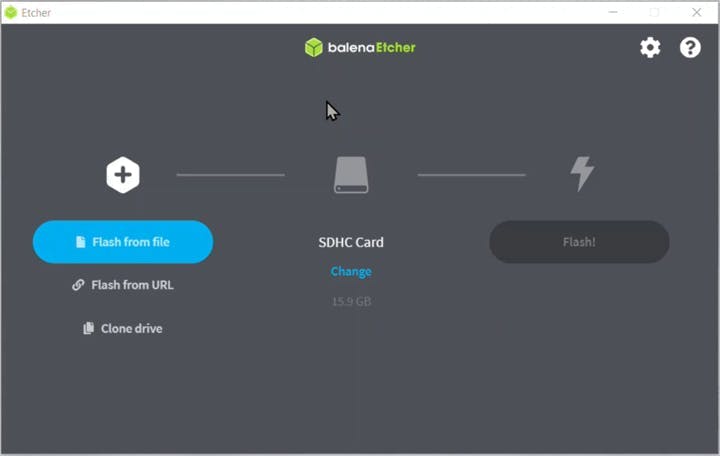

在您的 PC 上,下载 Balena Etcher 以将其写入您的 SD 卡。

完成后,您的 SD 卡已准备就绪,您可以将其插入 Kria 以设置 Xilinx Ubuntu!将 USB 键盘、USB 鼠标、HDMI/DisplayPort 和以太网连接到 Kria。

连接电源打开 Kria,您将看到 Ubuntu 登录屏幕。

默认登录凭据是用户名:ubuntu密码:ubuntu

启动时,界面可能会非常慢,所以我运行了这些命令来禁用动画调整以加快速度。

gsettings set org.gnome.desktop.interface enable-animations false

gsettings set org.gnome.shell.extensions.dash-to-dock animate-show-apps false

接下来,通过执行系统更新并调用此命令将系统更新到最新版本

sudo apt upgrade

安装用于系统管理的 xlnx-config snap 并对其进行配置(有关 Xilinx wiki 的更多信息):

sudo snap install xlnx-config --classic

xlnx-config.sysinit

现在检查设备配置是否工作正常。

sudo xlnx-config --xmutil boardid -b som

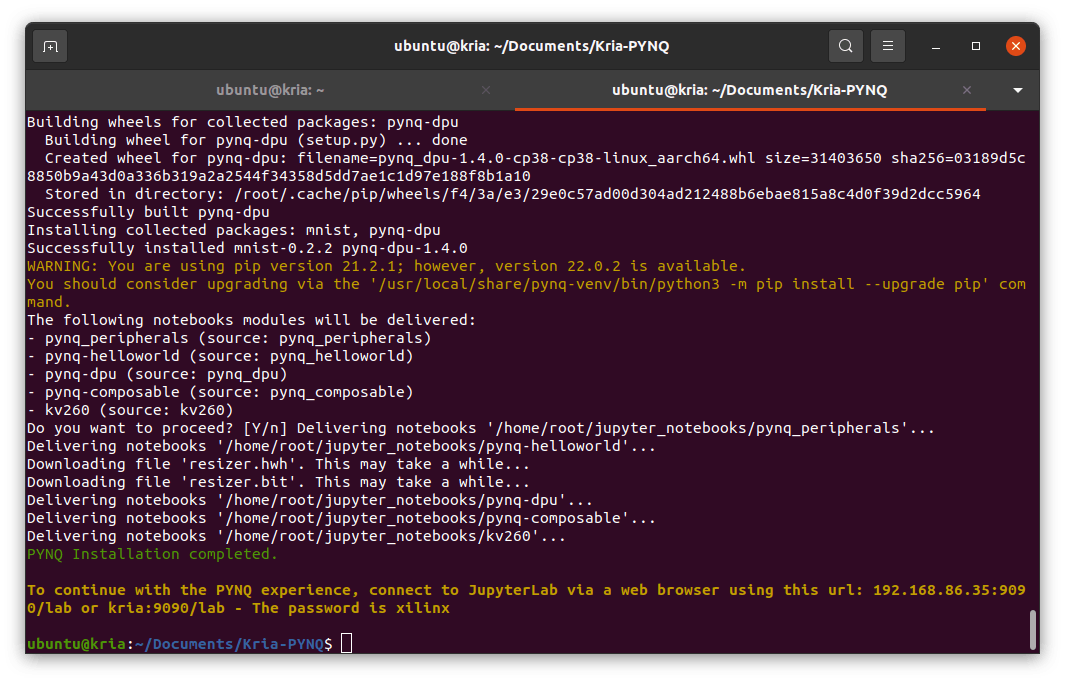

安装最新的Kria-PYNQ 包。这最多需要 30 分钟。

git clone https://github.com/Xilinx/Kria-PYNQ.git

cd Kria-PYNQ/

sudo bash install.sh

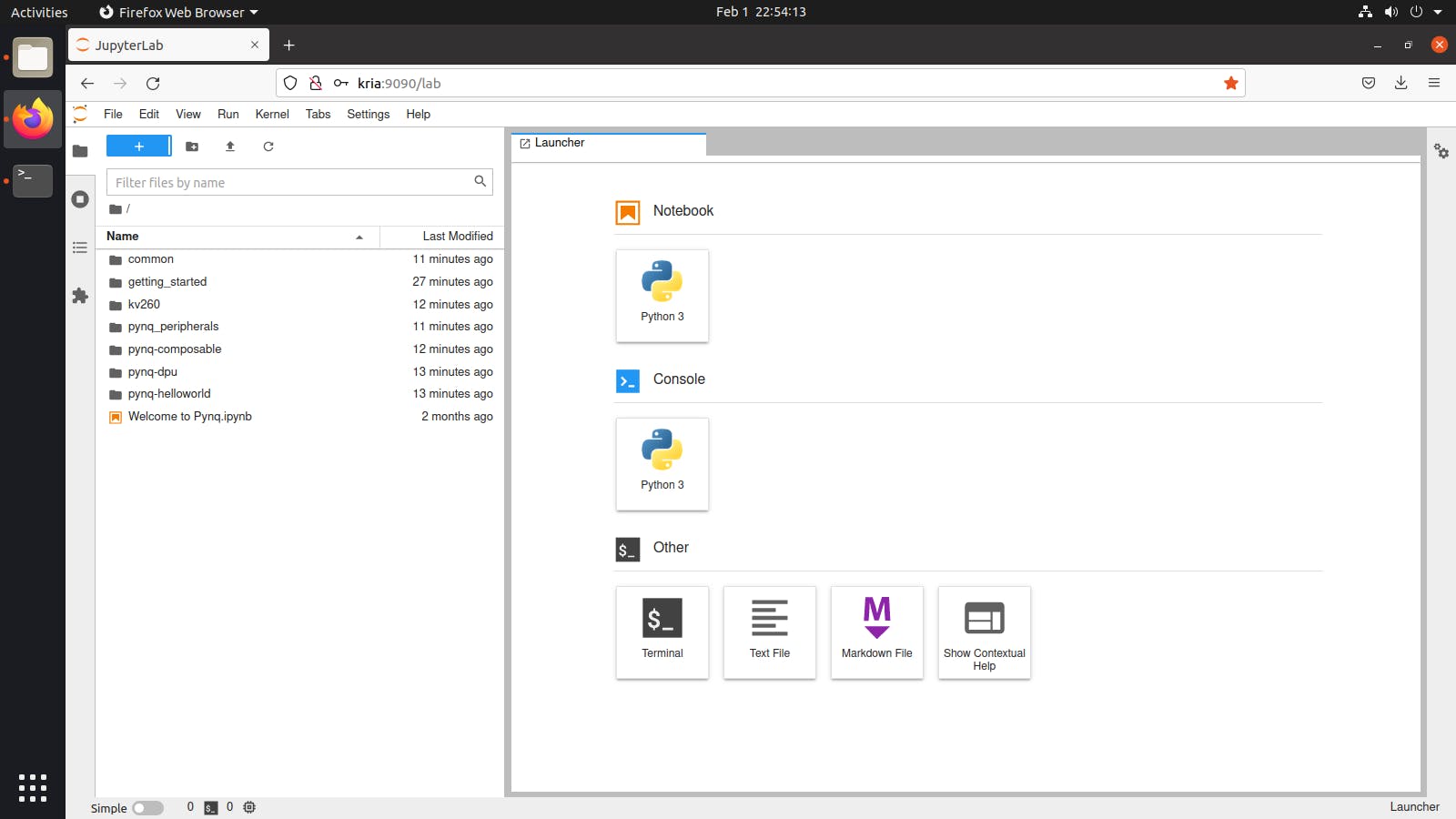

安装后,您可以在网络浏览器中转到“ kria:9090 ”以查看 Jupyter 笔记本。默认密码为xilinx 。

Kria 系统已准备就绪。现在让我们回到我们的 PC 来创建 PYNQ 覆盖比特流。

Vitis HLS 中的加速器 IP

使用 Vitis HLS,我们可以将许多现有的 C/C++ 代码转换为硬件 IP 模块。我将在不做任何修改的情况下调整此 SHA256 C 代码实现。

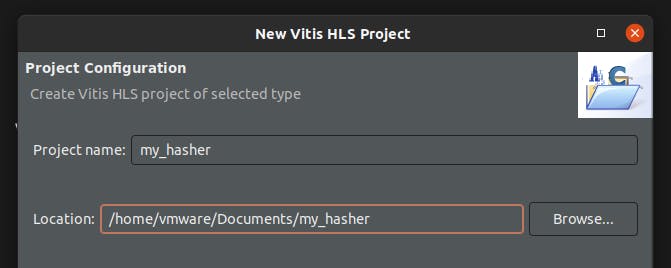

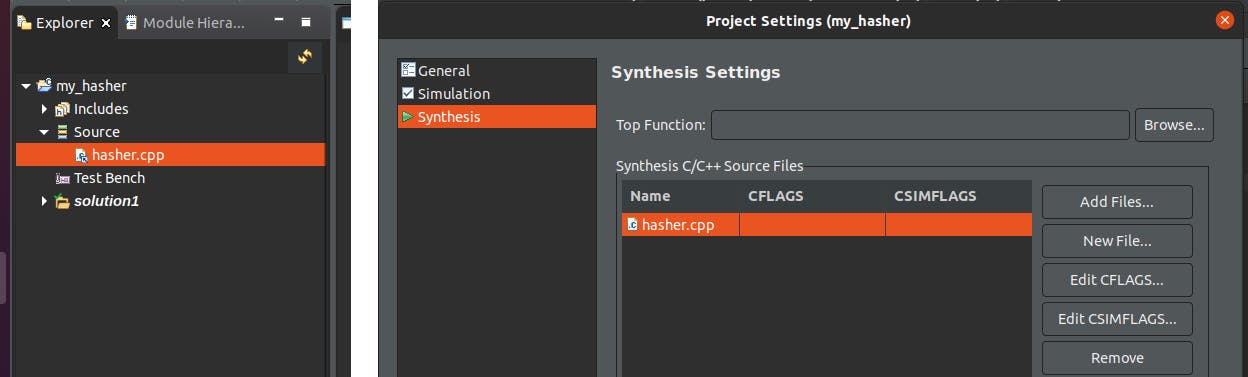

启动 Vitis HLS 并创建一个新项目。

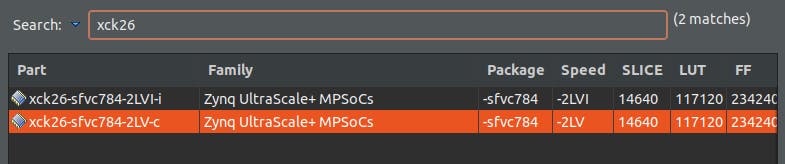

在下一页上,选择目标设备。对于 Kria KV260 Vision AI 入门套件,它使用的是零件:xck26-sfvc784-2lv-c。

进入工作区后,创建一个源文件。选择该文件作为项目综合设置中的顶级函数。

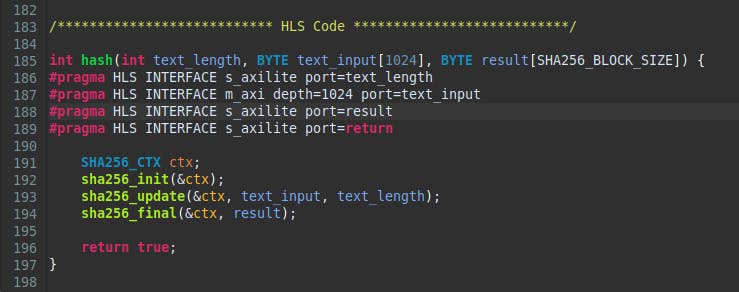

在代码中,我创建了一个名为hash(). 它基本上只调用 SHA256 散列函数。

现在请注意,此功能是在可编程逻辑 (PL) 中实现的。这意味着 的参数hash()实际上是需要传输到处理系统 (PS) 或从处理系统 (PS) 传输的输入和输出。因此,需要选择合适的通信接口。

对于 和 之类的小变量text_length,result我选择了s_axilitewhich 是适合小变量的串行协议。以后从 PYNQ 访问它也相对容易。

对于像 的大型缓冲区text_input[1024],我选择m_axi了并行协议。它占用了更多的逻辑和互连,但这是必要的,以便传输数据足够快。

有关更多信息,代码在本项目末尾提供。

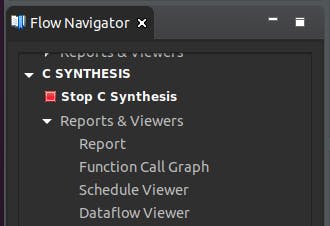

在 Flow Navigator 下启动 C 综合。

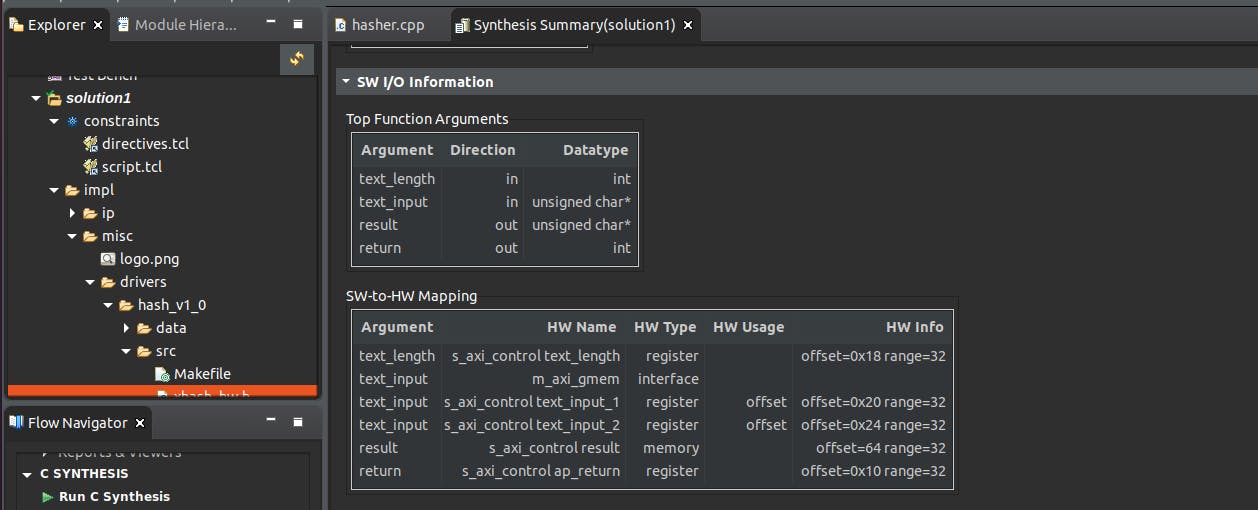

综合后,您可以验证我们稍后将在 PYNQ 中访问的参数。

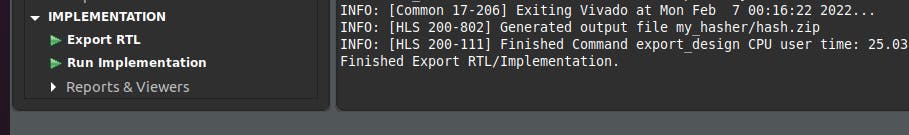

最后,选择 Export RTL 并选择要将其保存到的位置。它将输出一个 zip 文件,其中包含要在 Vivado 中导入的 IP 模块。

Vivado 中的框图综合

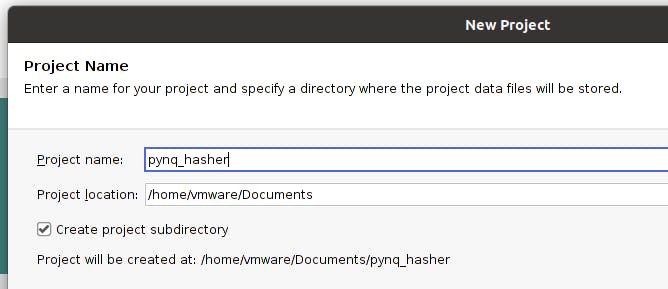

打开 Vivado 并创建一个新项目

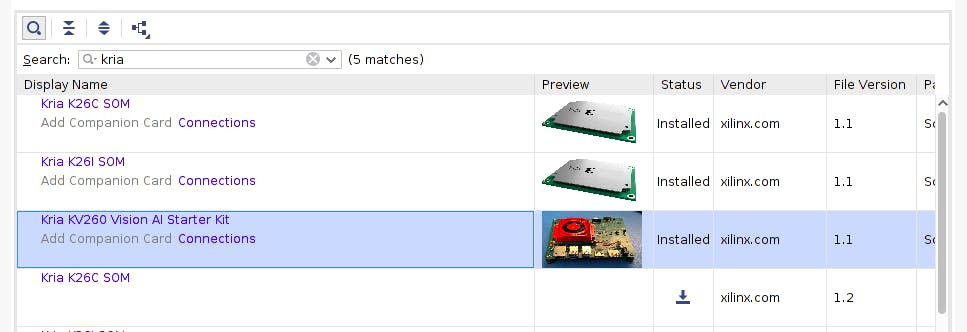

选择 Kria KV260 Vision AI 入门套件。继续使用所有默认值,直到到达项目工作区。

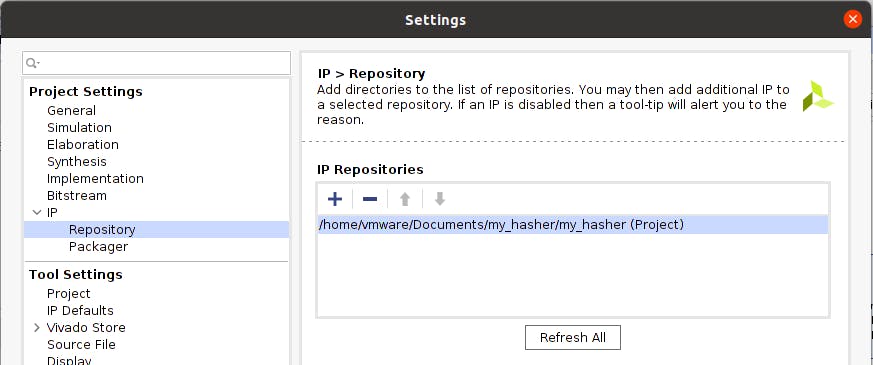

在我们做任何其他事情之前,我们需要添加我们之前创建的 IP。

转到Project Manager > Settings > IP > Repository ,然后添加包含 zip 文件的文件夹。

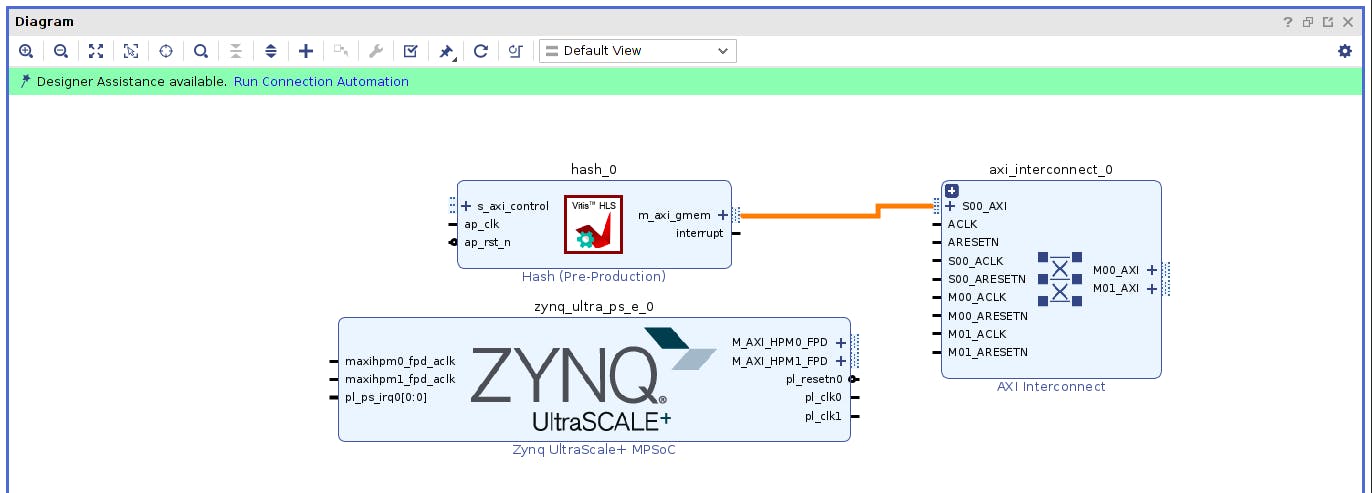

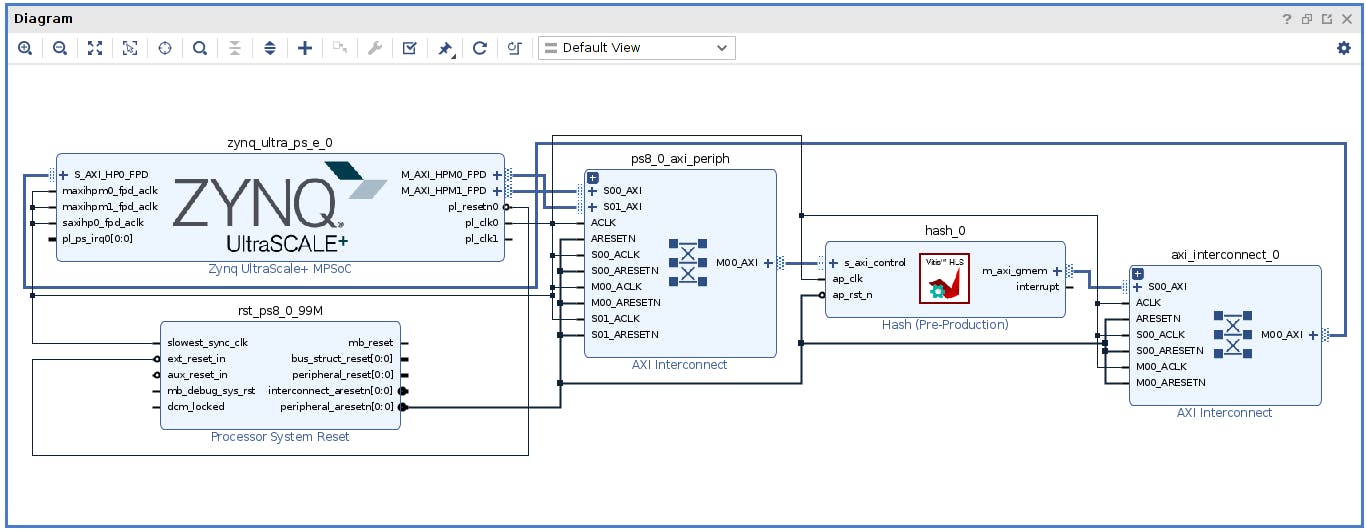

在 IP Integrator 下,选择 Create Block Diagram。添加以下块:

- Zynq UltraScale+ MPSoc(这是 PS)

- 哈希(我们从 Vitis HLS 生成的 IP)

-

AXI 互连(从我们的 IP 互连到

m_axi总线)

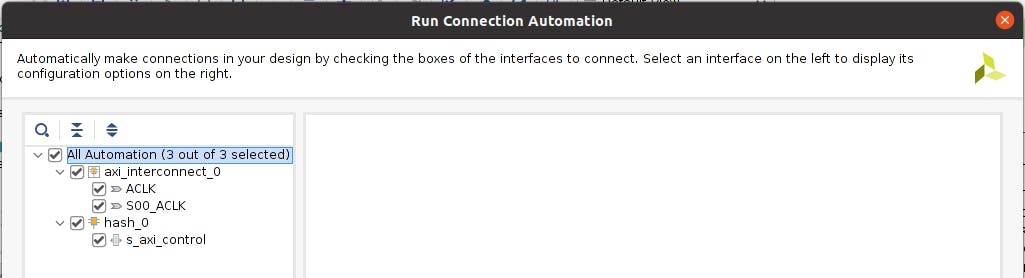

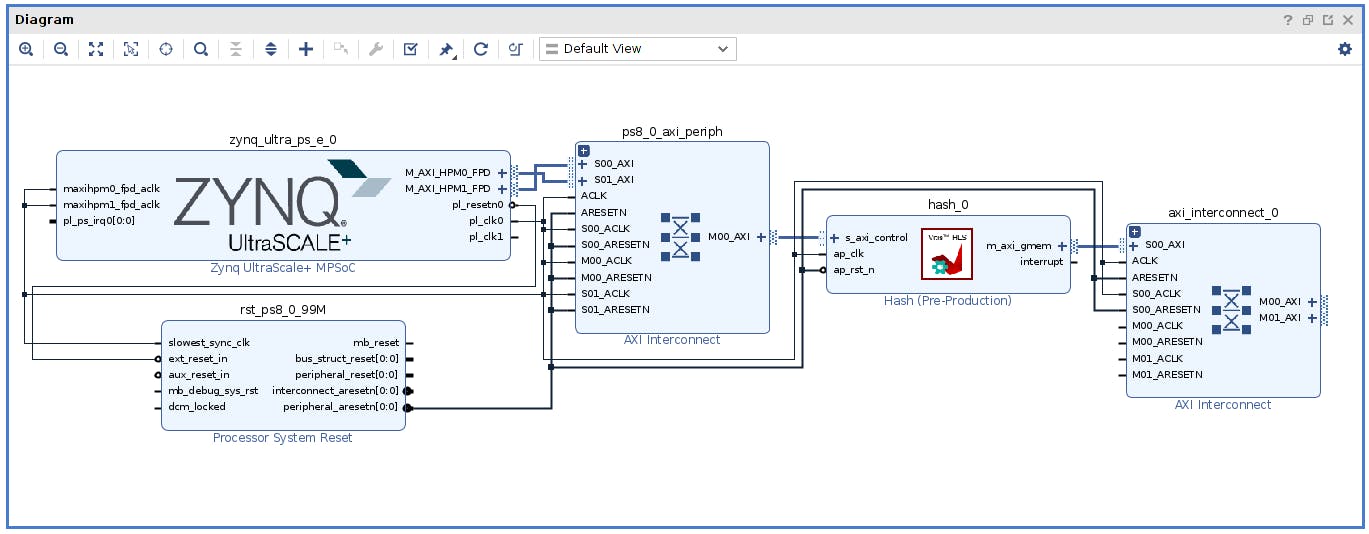

之后,运行连接自动化。选择所有可能的自动化并接受默认设置。

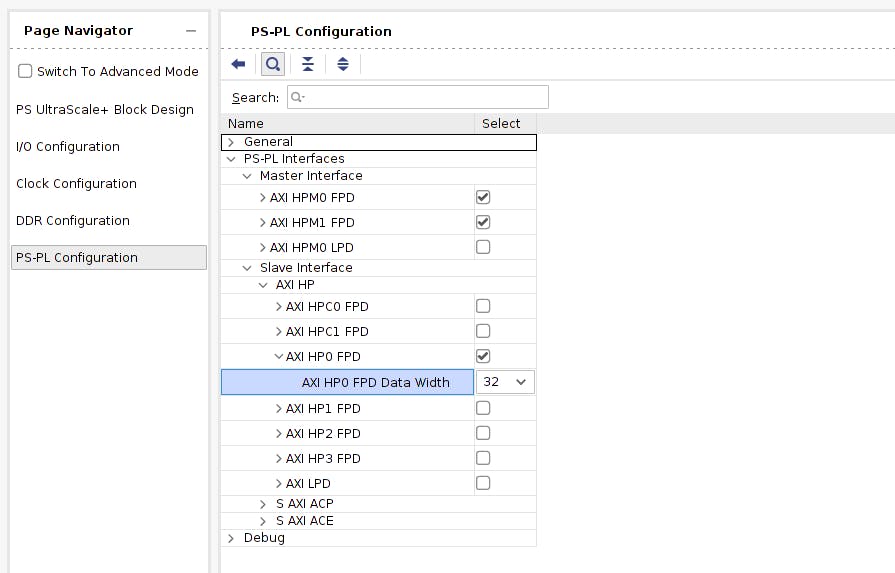

请注意,m_axi(Master)的互连总线仍未连接。这是因为我忘记在PS上启用Slave接口。

双击 Zynq UltraScale+ MPSoc 块。启用 AXI HP0 FPD (高性能)。检查数据宽度是否为 32 位,这与 HLS 中合成的内容相匹配。

再次运行连接自动化。这是最终的框图。

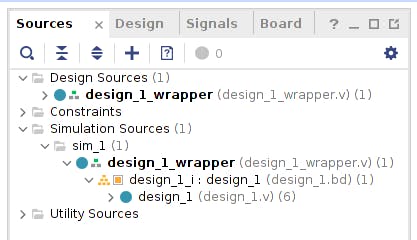

在 Sources 下,右键单击设计并选择 Create HDL Wrapper。它会自动包装设计,以便您为综合做好准备。

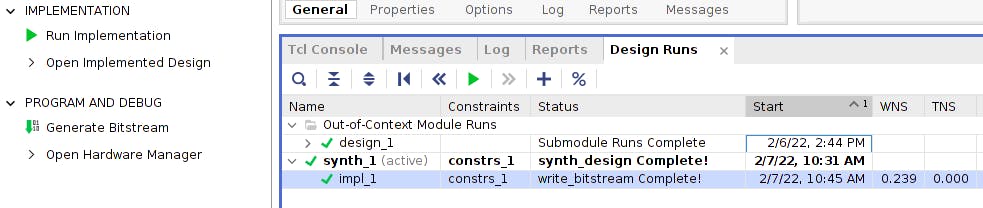

生成比特流。完成综合和实施可能需要长达一个小时的时间。

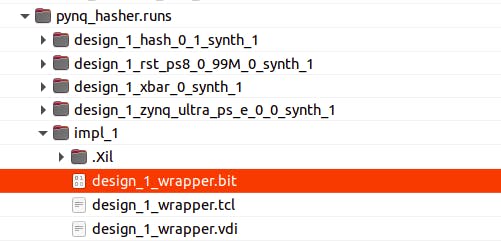

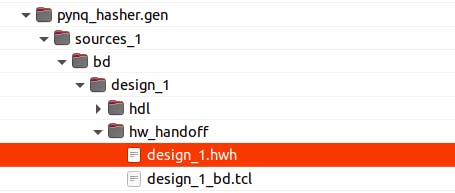

最后,为了获得 PYNQ 覆盖,我们必须检索 2 个文件:.bit文件和.hwh文件。

可以在以下位置找到比特流文件:*.runs/impl_1/design_1_wrapper.bit

硬件切换文件可在以下位置找到:*.gen/sources_1/bd/design_1/hw_handoff/design_1.hwh

将这些文件复制到 Kria。

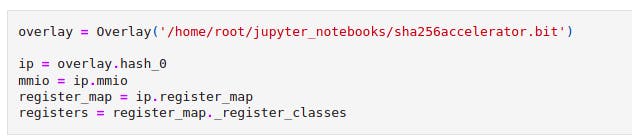

PYNQ 中的接口

我复制了 2 个文件并将其重命名为sha256accelerator.bitand sha256accelerator.hwh。请注意,两个文件必须具有相同的名称才能正确用作 PYNQ 覆盖。

我将解释我的代码的一些片段。您可以在下面找到完整的代码。

创建一个新的 Jupyter notebook,我们可以在其中编程比特流。

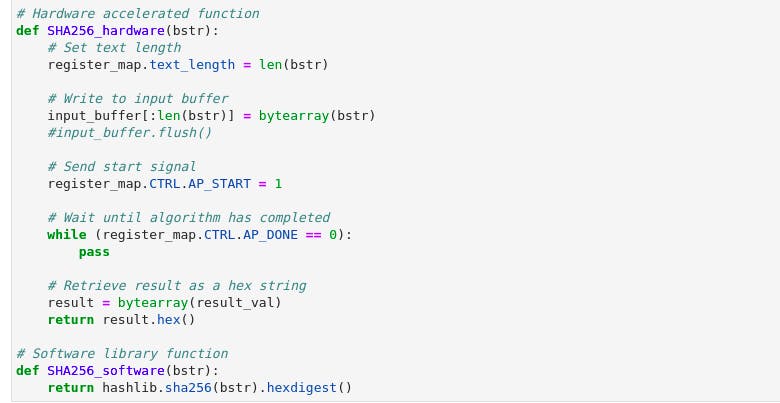

在这里,我定义了硬件功能,即将输入数据写入缓冲区并启动该过程。完成后,该函数将返回。我还定义了一个称为内置库的软件功能。

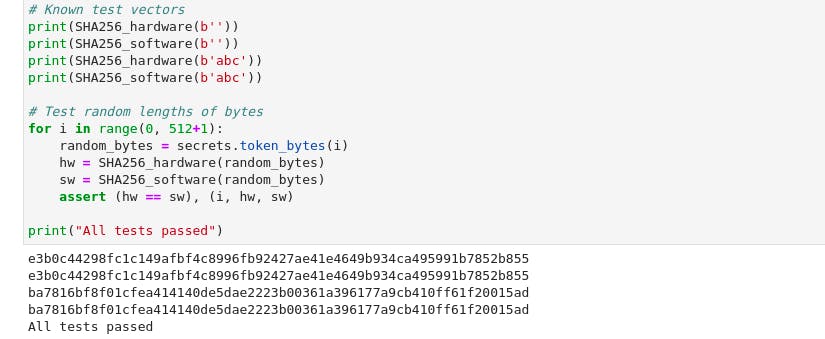

运行一些测试,我们可以比较两个函数的输入,以验证一切都在硬件上正确实现。

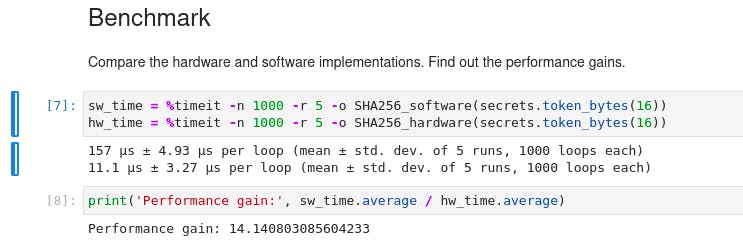

基准性能

运行一些基准测试,我们发现硬件实现比在软件上运行快约 14 倍。

结论

总而言之,使用 Vitis HLS 无需任何修改即可轻松加速 C 函数。尽管需要对硬件协议及其变体有一定的了解和了解,但软件过程相对简单。

从这里,我们了解过去如何使用 FPGA 来加速这些重复性计算,例如区块链挖掘。通过直接针对算法,硬件更具体,因此性能更高。

- Vitis HLS:使用任务级并行性的高性能设计

- Vitis HLS移植指南

- 使用PYNQ和Vitis AI的智能办公室热办公桌

- 《医用电子直线加速器》pdf 0次下载

- 基于STM32的C语言SHA256加密算法

- 基于FPGA的SIMD卷积神经网络加速器 24次下载

- 神经网络加速器简述 12次下载

- 基于深度学习的矩阵乘法加速器设计方案 3次下载

- Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上

- Vitis Vision | 利用Vitis HLS tcl shell 一键跑通视觉加速例程

- 工具包和Eval板帮助加速加速器应用 13次下载

- Green网络加速器 24次下载

- DRM系统的SHA256算法设计及FPGA实现 141次下载

- 加速器控制威廉希尔官方网站

- 基于FPGA的SHA-256算法实现

- 在Windows 10上创建并运行AMD Vitis™视觉库示例 434次阅读

- 一个微型的粒子加速器 648次阅读

- 通过SHA-256主/从身份验证系统实现更高的安全性 978次阅读

- 使用AXI CDMA制作FPGA AI加速器通道 1616次阅读

- 理解Vitis HLS默认行为 1636次阅读

- Vitis HLS知识库总结 3242次阅读

- Vitis HLS如何添加HLS导出的.xo文件 2935次阅读

- 使用AXI4-Lite将Vitis HLS创建的IP连接到PS 736次阅读

- Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上的教程 3614次阅读

- 如何在Vitis HLS中使用C语言代码创建AXI4-Lite接口 1580次阅读

- Vitis HLS工具简介及设计流程 2206次阅读

- 如何在Vitis HLS中使用C语言代码创建AXI4-Lite接口 6248次阅读

- XIlinx利用HLS进行加速设计进度 6541次阅读

- Hash算法简介 4932次阅读

- 基于SHA-256安全认证工作原理的最新安全认证解决方案 5255次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论