资料介绍

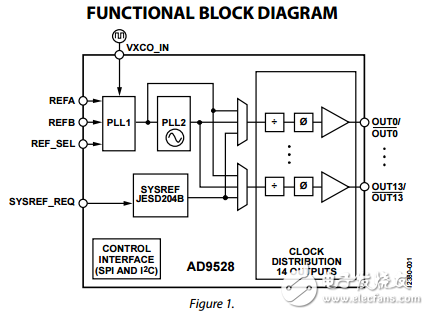

The AD9528 is a two-stage PLL with an integrated JESD204B SYSREF generator for multiple device synchronization. The first stage phase-locked loop (PLL) (PLL1) provides input reference conditioning by reducing the jitter present on a system clock. The second stage PLL (PLL2) provides high frequency clocks that achieve low integrated jitter as well as low broadband noise from the clock output drivers. The external VCXO provides the low noise reference required by PLL2 to achieve the restrictive phase noise and jitter requirements necessary to achieve acceptable performance. The on-chip VCO tunes from 3.450 GHz to 4.025 GHz. The integrated SYSREF generator outputs single shot, N-shot, or continuous signals synchronous to the PLL1 and PLL2 outputs to time align multiple devices. The AD9528 generates two outputs (Output 1 and Output 2) with a maximum frequency of 1.25 GHz, and 12 outputs up to 1 GHz. Each output can be configured to output directly from PLL1, PLL2, or the internal SYSREF generator. Each of the 14 output channels contains a divider with coarse digital phase adjustment and an analog fine phase delay block that allows complete flexibility in timing alignment across all 14 outputs. The AD9528 can also be used as a dual input flexible buffer to distribute 14 device clock and/or SYSREF signals. At power-up, the AD9528 sends the VCXO signal directly to Output 12 and Output 13 to serve as the power-up ready clocks. Note that, throughout this data sheet, the dual function pin names are referenced by the relevant function where applicable.

- 采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

- LMK0482x超低噪声JESD204B兼容时钟抖动消除器数据表

- JESD204B:适合您吗?

- 理解JESD204B协议

- AD9250:14位、170 MSPS/250 MSPS、JESD204B、双模数转换器数据表

- LTC2123:带JESD204B串行输出的双14位250 Msps ADC数据表

- AD9694:14位、500 MSPS、JESD204B、四路模数转换器数据表

- LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表

- AD9697:14位,1300 MSPS,JESD204B,模拟到数字转换器数据Sheet

- AD9528:具有14个LVDS/HSTL输出的JESD204B时钟发生器数据表

- LTC2122:带JESD204B串行输出的双14位170 Msps ADC数据表

- 集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

- AD9522-5:12 LVDS/24 CMOS输出时钟发生器数据表

- AD9516-5:14-输出时钟发生器数据表

- LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表

- 抓住JESD204B接口功能的关键问题 876次阅读

- SC6301低功耗超低噪声时钟抖动消除器简介 902次阅读

- 采用系统参考模式设计JESD 204B时钟 1251次阅读

- 在赛灵思FPGA上快速实现JESD204B 3965次阅读

- JESD204B学习手册 2277次阅读

- JESD204B与串行LVDS接口在宽带数据转换器应用中的考虑因素 1266次阅读

- 在串行LVDS和JESD204B接口之间选择 1353次阅读

- 宽带数据转换器应用的JESD204B与串行LVDS接口考量 1271次阅读

- 什么是JESD204B标准为什么需要关注JESD204B接口 1.2w次阅读

- 为便于实现如此庞大的吞吐量,JESD204B标准应运而生 4484次阅读

- 针对高速数据转换器的最新高速JESD204B标准带来了验证挑战 3021次阅读

- JESD204B接口及协议状态过程 3039次阅读

- JESD204B标准及演进历程 1.4w次阅读

- 采用系统参考模式设计JESD204B时钟 3120次阅读

- JESD204B SystemC module 设计简介(一) 3157次阅读

下载排行

本周

- 1TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 2开关电源基础知识

- 5.73 MB | 6次下载 | 免费

- 3100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 4嵌入式linux-聊天程序设计

- 0.60 MB | 3次下载 | 免费

- 5基于FPGA的光纤通信系统的设计与实现

- 0.61 MB | 2次下载 | 免费

- 651单片机窗帘控制器仿真程序

- 1.93 MB | 2次下载 | 免费

- 751单片机大棚环境控制器仿真程序

- 1.10 MB | 2次下载 | 免费

- 8基于51单片机的RGB调色灯程序仿真

- 0.86 MB | 2次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33564次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6653次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537796次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191185次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论