本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟,并且探讨

2013-09-26 14:34:31 3258

3258

不够的情况下有可能会造成 FIFO 的溢出。本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟。

2013-09-29 10:05:45 2100

2100

本文提出了一台基于S12的简易便携式数字示波器的设计方案,该设计方案中的数字示波器能对任意小于1MHz的波形进行频率和峰峰值的测量,且能够对被测周期信号或单次非周期信号进行单次采集与储存,连续显示。该设计方案中的以S12为主控单片机,制作出的示波器不仅可以测量低频的直流信号,也可以测量高频的交流信号。

2013-11-05 09:10:46 2665

2665

/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道

2019-05-29 17:52:03

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35:42

的。特别是在数字控制电源中,DVS 很常见,也很容易实现。稳压器一般用于生成恒定的输出电压。利用控制环路,可通过未经调节的输入电压生成稳定、精准的输出电压。动态电压调节(DVS)有什么作用?动态电压

2021-01-20 07:00:00

数字电子钟设计方案数字钟是一种用数字电路威廉希尔官方网站

实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型

2009-12-17 11:31:30

本帖最后由 eehome 于 2013-1-5 10:02 编辑

数字语音解码器的低功耗设计方案

2012-08-20 12:50:40

嗨,我有一个项目,我必须在发送器端序列化16位数字输入数据,然后在接收器端反序列化数据。这种数字链路的预期速度是100MHz-500MHz。这种实现必须是系统同步的,即没有任何时钟转发,我必须在Rx

2019-08-06 10:31:49

接(Dual Link)两种方式,对于单连接,仅用图1所示的1/2、9/10、17/18脚传输,它的传输速率可达4.9Gbps,双连接可达9.9Gbps。DVI接口在数字电视中的应用● 基本方案论证分析

2018-12-12 10:18:10

随着SerDes芯片集成度,复杂度,传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。为解决该测试难题,通过Nautilus UDI方案的导入,成功得实现了32 Gbps

2021-05-10 06:58:55

介绍一种包含千兆采样率ADC的系统设计方案

2021-05-14 06:07:02

介绍一种汽车LED照明系统的设计方案

2021-05-13 06:52:48

介绍一种视频监控系统的设计方案

2021-05-31 07:07:58

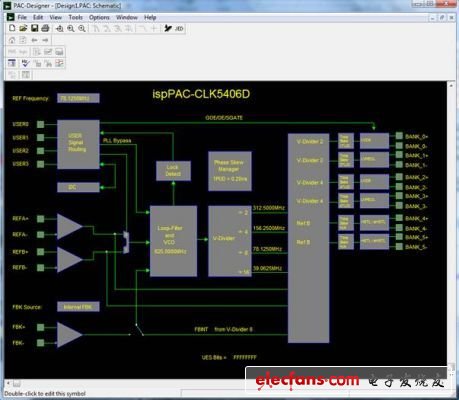

从ASIC到FPGA的转换系统时钟设计方案

2011-03-02 09:37:37

本帖最后由 eehome 于 2013-1-5 09:51 编辑

入侵报警系统设计方案

2012-08-18 15:36:22

分享一份智能视频监控应用系统的设计方案

2021-06-08 06:49:09

分享一款不错的AMBE-2000TM声码器在数字加密电话中的应用方案

2021-06-08 06:58:49

分享一款不错的保安公司监控报警联网综合管理系统设计方案

2021-06-01 06:12:27

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案

2021-04-30 06:34:54

分享一款不错的多功能对讲机通信系统设计方案

2021-05-20 06:45:08

一种基于PLC的智能钳型吊电气控制系统的设计方案

2021-05-07 07:07:42

本文提出了一种能够很好地反映卫星通信中星地链路特性的模拟系统设计方案。在确定硬件设计方案之前,搭建了合理的信道仿真模型,并对仿真结果进行了分析。

2021-04-08 06:09:33

基于51单片机的时钟-跑表设计方案(程序+仿真)

2018-11-29 12:07:49

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步威廉希尔官方网站

来支持高效采集。基于这种目的,采用FPGA威廉希尔官方网站

设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

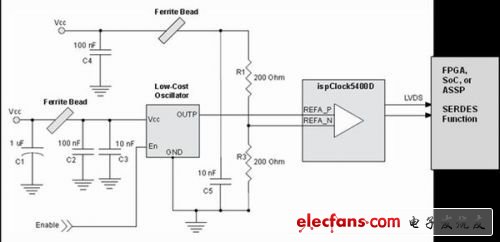

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)威廉希尔官方网站

的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线

2019-05-21 05:00:13

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

小区智能化系统设计方案

2012-08-18 15:38:43

本帖最后由 eehome 于 2013-1-5 09:50 编辑

平安城市视频监控系统设计方案-20091213

2012-08-20 09:56:45

SerDes是怎么工作的?SerDes有传输时钟信号吗?

2021-10-18 08:53:42

为 EMI 敏感和高速 SERDES 系统供电

2019-05-21 14:34:36

求一款RFID读卡器测试系统的设计方案

2021-05-11 07:11:35

求大神分享一款天平系统的设计方案

2021-05-11 06:20:54

求一款看守所智能网络门禁系统的设计方案

2021-06-01 07:07:25

本文提出的一种数字信道化IFM接收机方案结合了数字信道化接收机高效结构和相位差分瞬时测频方法,从而降低了系统复杂度,提高了实时处理能力,仿真结果表明该方案具有较好的信号检测能力。用现代威廉希尔官方网站

来实现宽带

2021-02-23 07:05:58

求一种数字式温度测量电路的设计方案

2021-05-17 06:16:41

求一种以CPLD为核心处理电路的数字电压表的设计方案

2021-04-28 07:14:04

漂移及漂移形成的原因是什么?光纤漂移引起的SERDES FIFO溢出问题分析BBU SERDES 双系时钟方案及具体实现

2021-04-19 08:35:11

本文介绍了一种基于ARM的视频监控系统的设计方案,采用软压缩算法,讨论了系统的硬件和软件设计。

2021-06-08 06:27:10

求一种基于单片机的简易洗衣机系统仿真设计方案

2022-01-17 08:09:52

一种基于FPGA威廉希尔官方网站

的多按键状态识别系统的设计方案

2021-05-06 08:44:59

求一种多路模拟数字采集与处理系统的设计方案

2021-04-28 07:04:52

求一种多通道同步数据采集及压缩系统的设计方案。

2021-04-28 06:13:04

求一种天然气发动机电控系统的设计方案

2021-05-13 06:12:56

求一种新型系统级可编程芯片的设计方案

2021-05-06 07:44:32

求一种智能物品清点系统的设计方案

2021-05-20 07:29:31

求一种智能电源模块测试系统的设计方案

2021-05-10 06:35:30

一种基于CPLD控制的直流固态功控系统的设计方案。

2021-05-06 06:23:55

求一种视频检测和远程控制的嵌入式系统设计方案

2021-05-27 06:38:21

TPMS主要有哪几种实现方式?如何选用新型送器(遥控钥匙)与接收器中几种芯片?一种基于LIN总线分布式实时轮胎压力监测系统的设计方案

2021-05-13 06:03:12

求一种陶瓷扬声器系统的放大器设计方案

2021-06-04 07:10:45

求大佬分享一种多光谱可见光遥感图像压缩系统的设计方案

2021-06-02 06:39:48

求大佬分享一种小型通信系统的设计方案

2021-05-28 06:13:52

求大神分享一种PPSM嵌入式RTOS中的窗口系统设计方案

2021-04-27 06:20:09

测温系统设计方案,原理方案都有,有图有真相!

2014-09-05 16:29:53

用单片机实现电子时钟设计方案时钟电路在计算机系统中起着非常重要的作用,是保证系统正常工作的基础。在一个单片机应用系统中,时钟有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振

2009-12-17 11:20:48

电气CAD文件中高效的工作流程性能卓越的 PCschemetic ELautomation软件具有作电气设计时所需要的所有功能。其独一无二的工作流程可节省您大量的时间,它代替了所有的订货信息——从

2009-12-04 11:24:24

的serdes?2、如果serdes是各自的,是否共享输入时钟?(外部时钟,对于我们来说是156.25MHz)3、在研究SRIO速率配置时发现文档中描述:serdes的输出时钟不能超过3.125GHz,该描述是否准确?是否适用于所有的serdes模块?谢谢!

2018-08-06 06:17:36

为了保证图像采集的高速性和连续性,求一种适用嵌入式系统的数字图像采集模块设计方案?

2021-04-08 06:13:26

直播PPT:直播简介:电源威廉希尔官方网站

的发展日新月异,高可靠性,高频率,高效率,高功率密度,节能环保是未来电源产品发展的趋势和主流。其中LLC电源设计方案越来越受到电子工程师的青睐和追捧并成为中高功率等级

2019-01-04 11:41:20

什么是达芬奇威廉希尔官方网站

?达芬奇威廉希尔官方网站

在数字视频系统的应用是什么?

2021-06-04 07:17:50

针对单片机的时钟频率电路有哪几种设计方案?分别有何优缺点?

2022-02-22 06:20:34

问一下哪里能找到模拟路灯控制系统的设计方案吗?

2015-07-20 11:06:39

100MHz的时候,有些接口功能是有限制的;使用外部的REF_CLK则可以灵活选择配置时钟。Serdes方案表输入文字在LS1028A芯片中,SerDes可以配置下表的功能,不在表中的搭配是不允许

2020-10-28 17:15:14

的SerDes设计方案做个简单解读。PART.2 LS1028A飞凌9月份发布了NXP的LS系列家族新成员——FET1028A-C核心板。其包含丰富的高速接口:PCIE、SATA、USB、以太网。与我

2020-11-01 20:21:02

数字电视系统设计方案

一、客户需求 1、通过改造,建设传输750M带宽内的40个模拟频道和50个数字电视频道的双平台传输网络系

2010-03-26 17:39:40 39

39 数字电路实验的虚拟化设计方案

介绍了虚拟仪器的简单使用方法及其在数字电路实验教学中的应用, 列举了几个例子, 并通过虚拟仪器与传统仪器的比较得出

2010-03-30 16:15:28 20

20 在数字通信系统中,由于有高斯噪声和多径的影响,接收信号产生损失,从而导致时钟信号的提取更加困难,而时钟信号的不准确性会降低整个系统的性能。本文我们给出一种改进

2010-08-03 17:04:27 33

33 高速串行接口设计的高效时钟解决方案

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)威廉希尔官方网站

的高速串行接口来取代传统的并行总线架

2010-04-09 13:24:59 968

968

病房呼叫系统设计方案

2011-01-28 09:39:13 19619

19619

本内容提供了全数字扩频接收机的设计方案

2011-10-11 15:10:08 39

39 一种多功能数字时钟的pcb设计方案,供大家学习使用。

2016-05-16 15:53:04 0

0 厂区监控系统设计方案_-_完本

2017-01-04 14:29:25 0

0 高效单级变换式LED驱动电源设计方案

2017-01-14 11:16:50 13

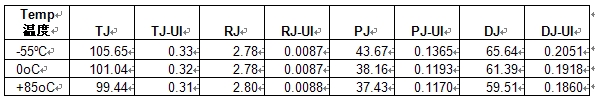

13 我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40:10 5965

5965

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)威廉希尔官方网站

的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线

2017-10-26 15:37:45 4

4 时钟的管理。本文详细介绍了利用嵌入式微控制器MSP430单片机和数字锁相环(DPLL)来实现嵌入式同步时钟系统的方案和设计实例。 系统总体结构 同步设备的同步时钟系统要求能达到3级时钟标准,可使用从SDH网络上提取的时钟或外部时

2017-11-04 10:21:44 6

6 在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟,然后将此时钟作为SERDES的参考时钟。

2017-11-18 12:08:49 5865

5865

熟悉电磁兼容设计的工程师都知道,设计好时钟电路是保证达到系统辐射指标的关键,时钟电路EMC设计的好坏直接影响整个系统的性能。对于经验丰富的工程师来说,在数字系统中有许多种方法可用于解决电磁干扰问题。

2018-04-23 08:14:00 1560

1560

随着SerDes芯片集成度、复杂度、传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。但通过Nautilus UDI方案的导入,成功实现了32 Gbps SerDes

2018-06-10 10:51:17 4434

4434

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 4073

4073

为满足目前的56GPAM-4 SerDes威廉希尔官方网站

,以支持更高带宽的100G+以太网和光网络设计。硬件开发人员通常需要100fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。

2020-11-12 15:25:55 4154

4154 一种数字式可调直流稳压电源系统设计方案

2021-06-25 10:32:54 34

34 基于STM32单片机的时钟树设计方案

2021-08-04 16:37:06 38

38 8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数

2023-07-27 16:10:01 1566

1566

的。在使用SerDes的过程中,设计者有太多的疑惑:为什么在传输的过程中没有时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?时钟怎么恢复?等等这些问题,如果设计者能够完全理解

2023-10-16 14:50:37 558

558

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 SerDes(Serialization/Deserialization)是一种在数字通信系统中提供重要优势的串行/并行转换电路。

2023-10-20 15:31:24 832

832

电子发烧友App

电子发烧友App

评论