随着嵌入式威廉希尔官方网站 的发展,基于SoPC威廉希尔官方网站 的嵌入式系统所具有的软硬件可裁减、可扩充、可升级以及可在线修改的特点越来越受到人们的重视。SoPC系统通常具有以下基本特征:采用大容量可编程逻辑器件来实现,单芯片、低功耗;至少包含1个以上的嵌入式处理器IP核;具有一个或多条片上总线作为系统扩展功能的接口;具有充足的片上可编程逻辑资源,用户可以根据需要扩充功能部件。

异步串行通信协议(UART)以低成本、高可靠性等优点而广泛应用于嵌入式系统中,多篇文献也讨论了UART协议的硬件设计方法,但多数只限于讨论 UART协议的硬件实现,缺少从SoPC系统的角度论述UART IP核的设计方法。本文以UART IP核和PLB总线为例,讨论了在SoPC系统下UART IP核的设计方法,该方法对其他IP核的设计有一定的参考作用。

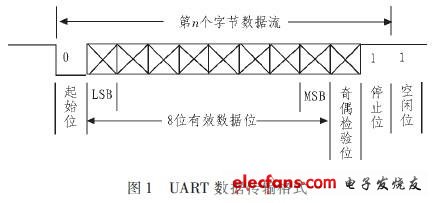

1 UART协议介绍

UART是一种串行异步通信方式,它采用RS232电平在串行链路上进行全双工的通信,其数据传输格式如图1所示:UART协议在空闲时为高电平,通过发送起始位提示接收方数据传输即将开始,接着传输8位有效数据位和奇偶检验位,最后发送停止位表示一个字符传输完成。

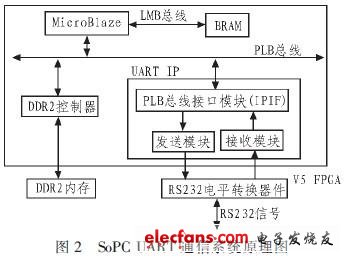

2 SOPC UART通信系统介绍

本文设计的SOPC UART通信系统主要包括MicroBlaze处理器、PLB总线、UART IP核和DDR2控制器IP核,如图2所示。

MicroBlaze处理器是Xilinx公司针对其FPGA器件优化的32位微处理器核,它采用RISC(Reduced Instruction System Computer)架构和哈佛总线结构,具有独立32位数据和指令总线,能够高速执行和访问片上存储器和片外存储器上的程序与数据;提供本地块存储器总线(LMB)、处理器本地总线(PLB)等总线接口。

PLB总线作为IBM CoreConnect总线协议簇中的一部分,广泛的应用于IBM PowerPC处理器架构中。该总线具有总线地址空间大,总线吞吐率高,能支持多个主从设备连接等特点。如图3所示,MicroBlaze处理器通过 PLB总线与UARTIP核、DDR2控制器相互连接,各部件之间通过PLB总线协议进行交互。其中,MicroBlaze处理器作为主设备完成系统控制和UART通信流程控制,UART IP核作为从设备在主设备的控制下完成异步串行通信,DDR2存储指令和数据。

MicroBlaze处理器和DDR2控制器采用Xilinx公司提供的IP核,UART IP核由用户编写逻辑,它是文中设计的主要内容,对此模块的设计将在下一节进行详细阐述。

3 UART IP核设计

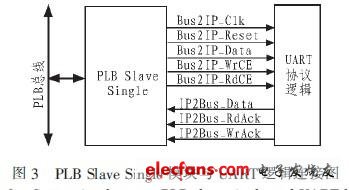

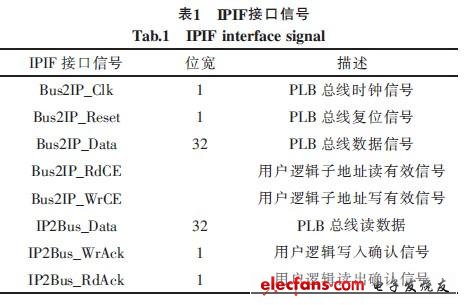

3.1 PLB Slave Single模块介绍

如上,UABT IP核作为PLB总线的从设备,必须提供PLB总线接口。但由于PLB总线协议复杂,实现其接口难度较大,Xilinx公司为了使用户编写的逻辑能够方便的连结到PLB总线上,提供了一种PLB总线与用户逻辑之间的接口模块(IPIF,IP Interface),利用它简化了PLB总线接口信号、总线协议和其他接口相关问题。IPIF接口逻辑中最简单的模块称为PLB Slave Single模块,它提供了一种轻量级的PLB总线接口,为PLB总线主设备提供了解析从设备地址空间,读写从设备寄存器/存储空间等基本服务。本文设计的UARTIP核与MicroBlaze处理器之间仅通过寄存器的读写进行交互,PLB Slave Single模块很好的满足了该设计要求,因此采用PLB Slave Single模块与UART逻辑共同构成了UART IP核。PLB Slave Single模块与UART逻辑之间的连接关系如图3所示,接口信号说明如表1所示。

在系统中,UART IP核的内部寄存器组映射为处理器的某段地址空间,MicroBlaze处理器通过对该段地址的读写实现对UART IP核的访问。当MicroBlaze处理器访问UART IP核的某个寄存器时,PLB总线会产生相应的地址信号和读写信号,该信号被UART IP核中的PLB Slave Single模块解析并生成相应的IPIF信号,UART IP核中的UABT逻辑响应该IPIF信号,完成寄存器的读写。

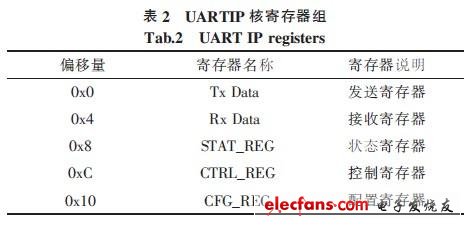

3.2 UART IP核寄存器组设计

文中设计的UART IP核提供了5个寄存器,如表2所示。其中发送寄存器和读接收寄存器完成UART数据的发送和接收。状态寄存器提供了UART IP核内部状态,包括接收数据有效,发送FIFO满,接收FIFO满,奇偶校验错等状态。控制寄存器提供了UART IP核复位功能。配置寄存器提供了波特率设置,奇偶校验位设置等功能。

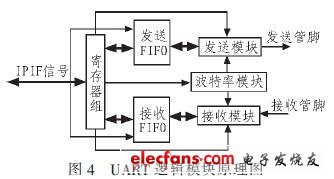

3. 3 UART协议逻辑模块设计

本文设计的UART协议逻辑模块主要包括波特率产生模块,发送模块,接收模块,寄存器组等几个部分,其结构如图4所示。寄存器组说明如表2,其他几个模块的设计如图4所示。

3. 3.1波特率模块

波特率模块根据PLB总线提供的时钟产生需要的发送时钟和接收时钟。由于UABT在发送数据时只需要按照发送波特率将数据串行地发出就可以了,因此发送时钟就等于发送波特率。而当UART在接收数据时,需要对串行数据进行采样以判断接收数据。由于接收方和发送方的时钟不可能完全同步,所以需要对每一位接收数据持续电平的时间进行分段。分段越多,接收出现误判的概率就越低,但系统开销也越大。在实际的设计中通常采用发送时钟的16倍作为接收时钟。波特率模块的分频功能由两个16位计数器实现,它将PLB总线时钟按配置寄存器的设定进行分频,产生发送时钟和接收时钟。

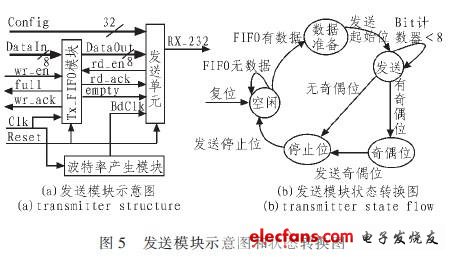

3.3.2发送模块

发送模块主要包括发送FIFO和发送单元两部分,如图5(a)所示。发送FIFO数据位宽度为8bit,深度为16字节。发送FIFO缓存 MicroBlaze处理器需要发送的数据。当FIFO空间满时,发送模块将状态寄存器中“发送FIFO满”标志位置1,MicroBlaze处理器通过查询该位以判断UART IP核是否可以接收下一个发送数据。

发送单元的设计用有限状态机的方法实现,其状态转换图如图5(b)所示。系统在复位后,发送单元处于空闲状态。当FIFO有发送数据时(Empty管脚为低),发送单元发出读FIFO操作,并进入数据准备状态。当数据从FIFO中读出,发送单元首先发送起始位,进入发送状态。在发送状态下,发送单元依次串行发送8比特数据,并计算当前的奇偶校验码。在数据发送结束后,若配置寄存器中奇偶校验位为1,则发送奇偶校验位。最后发送单元发送停止位,回到空闲状态,完成次数据发送。

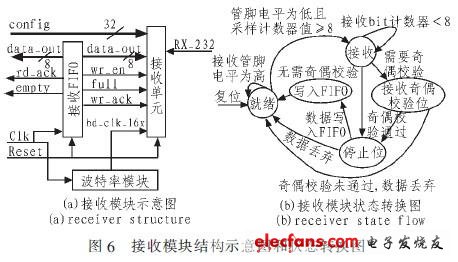

3.3.3接收模块

接收模块由接收FIFO和接收单元两部分组成,如图6(a)所示。接收FIFO数据位宽度为8bit,深度16字节,它负责缓存接收单元收到的数据,并在收到数据后将状态寄存器中“接收数据有效”标志位置1.MicroBlaze处理器通过查询该位来判断是否有数据到达。

接收单元的设计同样采用了有限状态机的方法,其状态转换图如图6(b)所示。系统在复位后接收单元处于就绪状态。当接收单元在接收管脚连续检测到8个低电平时认为起始位有效,进入接收状态。在接收状态下,接收单元每16个接收时钟采集一次接收数据。8个接收数据都采集完成后,接收单元根据配置寄存器中“奇偶校验位”是否为1决定是否进行奇偶校验。若奇偶校验通过,接收单元将接收到的数据写入接收FIFO.若奇偶校验未通过接收FIFO满,接收单元丢弃收到的数据,并在状态寄存器中置“奇偶校验出错”位或“接收FIFO满”位为1.

4实验验证

4. 1系统硬件介绍

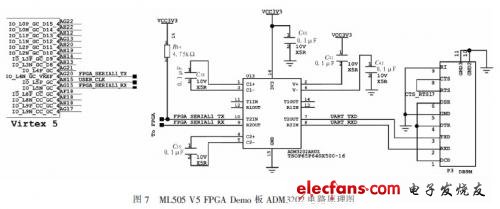

本文采用Xilinx公司提供的ML505 V5 FPGA Demo板作为SoPC系统硬件平台。ML505 FPGA演示验证板主要由一块Virtex-5 XC5VLX50T FPGA构成,此外还包括RAM、Flash、以太网接口芯片、USB接口芯片以及ADM3202 RS-232电平转换芯片等外围扩展芯片,其中ADM3202电路原理图如图7所示。

实验采用Xilinx公司ISE工具完成UART IP核的逻辑综合和仿真,仿真波形如图8所示,发送数据为0x01.UART IP核仿真通过后,用EDK工具提供的Peripheral Import Wizard生成一个采用PLB Slave Single模块的自定义IP核框架。在该IP核目录下的user_logic.v文件中例化波特率模块、发送模块、接收模块和寄存器组,并增加相应总线访同逻辑后即生成了本文设计的UART IP核。

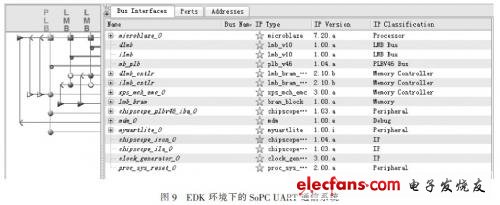

用EDK工具中的Base System Builder wizard新建一个如图3所示的SoPC系统,如图9所示。在Port界面下将UART IP核的收发管脚定义为External,并在UCF文件中加入收发管脚的管脚映射描述。在Address界面下生成UART IP核的地址空间,UART通信测试程序将通过该地址空间访问UART IP核。用EDK工具中Hardware菜单下Generate Bit Stream命令生成该SoPC系统的FPGA配置文件。用该配置文件配置ML505板载FPGA后,即生成了SoPC UART通信系统硬件。

用EDK工具中的Xilinx SDK软件开发工具编写相应的UART通信测试程序,编译后将程序下载至MicroBlaze处理器程序空间。将ML505板串口与PC机串口连接后运行 UART通信测试程序,在PC机上可以观察到此UART通信系统可以正确的发送和接收UART数据,证明了该UART IP核工作正常。

5结论

文中详细介绍了一种基于SoPC概念的UART IP核的设计。通过将Xilinx公司提供的PLB Slave Single模块和本文设计的UART逻辑模块结合,快速搭建了一个满足PLB总线接口要求的UART IP核,仿真与综合结果表明该UART IP核各项功能均达到预期要求。该设计方法既采用了成熟的商业IP核,也利用总线接口模块将用户自定义IP核与商业IP核连接成为一个完整的SoPC系统。该方法增加了系统的灵活性、扩展性,同时缩短了系统开发时间,降低了系统开发难度,可为其他嵌入式系统的开发提供有益的参考。

电子发烧友App

电子发烧友App

评论