输入对称离散无记忆信道下,极化码可以“达到”香农容量,并且有着低的编码和译码复杂度。客观地看所有polar码的文章和公开源码matlab,但原著,发布者均和华为无关。华为在polar码中得到了什么利益

2016-11-22 10:43:19

在RFID系统中,标签摆放姿态的不固定要求读取其信息的阅读器天线是圆极化,而小型圆极化天线在RFID中有重要应用且成为研究热点。文中设计并研究了一款902~928 MHz的6 dBi小型圆极化天线,轴比

2019-08-22 07:09:35

这几个论文是FLOWMAP和DAG-MAP算法,用来对组合逻辑进行fpga分割的,看完终于知道ISE或者quartus怎么对组合逻辑分割到4或者6输入LUT中了,以后继续研究布局布线的算法。

2015-01-15 16:30:44

BCD码的硬件实现,采用左移加3的算法,具体描述如下:(此处以8-bit 二进制码为例) 1、左移要转换的二进制码1位2、左移之后,BCD码分别置于百位、十位、个位3、如果移位后所在的BCD码列大于或

2017-05-11 16:21:02

CRC校验码算法的研究与实现

2012-08-06 11:09:12

论坛里面的大神们,有没有已经完成LDPC码编译码算法的FPGA实现,本人目前在做这方面的项目,时间比较紧,紧急求购IP核。。

2012-04-16 23:43:28

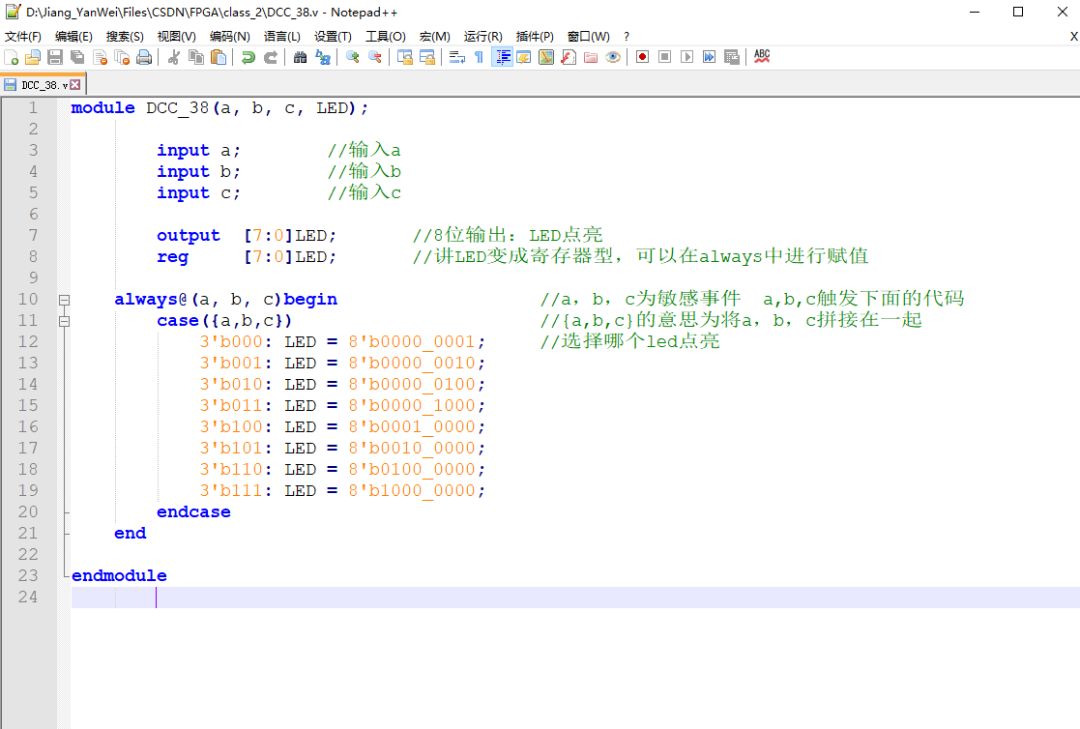

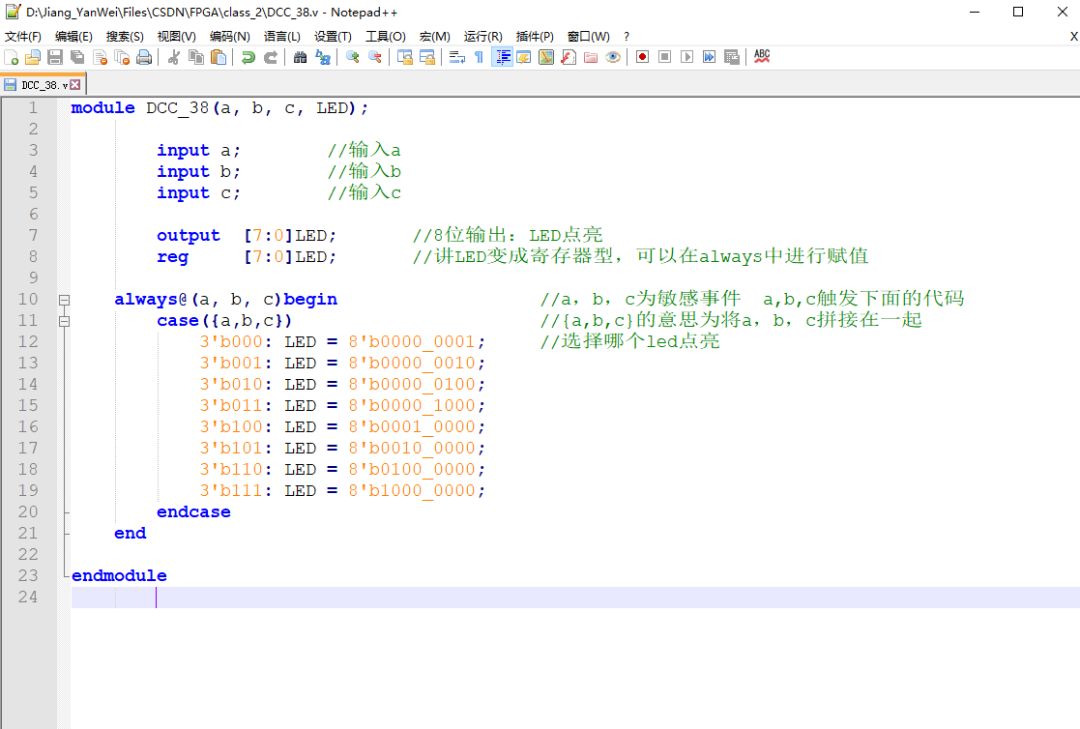

,OFF,ON1D7点亮 ONON,ON,OFF1D8点亮 ONON,ON,ON1D9点亮注:X表示ON或OFF,即任意状态。 2 板级调试下载sp6.bit文件到FPGA中,可以如图视频一样操作拨码开关,实现3-8译码器的功能。 `

2015-11-02 13:17:03

的不足,同时也方便在现场可编程门阵列(FPGA)中增加一些其他相关的应用功能,因此在FPGA中实现CVSD语音编译码调制功能的前景将是非常广阔的。这里将详细介绍什么是CVSD?其算法分析如何在FPGA中实现?

2019-08-07 07:04:27

什么是Turbo码的迭代译码算法?Turbo 码获得优异性能的第二个重要因素是应用了基于最大后验概率准则 (MAP) 的迭代译码算法。当前Turbo译码算法有哪些?(1) 标准算法(MAP)它对

2008-05-30 16:24:49

进行多次迭代实现了伪随机译码。 其他的编码方式,一时在信息和编码理论界引起了轰动。从此以后,Turbo 码得到了广泛的关注和发展,并对当今的编码理论和研究方法产生了深远的影响,信道编码

2008-05-30 16:21:20

的信息损失。可以考虑令内码译码的输出也是一个软判决输出,这样外码也可采用软判决译码,使整体性能得到提高。近几年的研究发现,如果采用迭代译码算法,将会大大降低级联码的门限效应,最大程度上发挥它的纠错能力

2008-05-30 16:16:10

什么是硬判决和软判决Viterbi 译码算法 ?接收到的符号首先经过解调器判决,输出0、1 码,然后再送往译码器的形式,称为硬判决译码。即编码信道的输出是0、1 的硬判决信息。我们选择似然概率P

2008-05-30 16:11:37

有没有关于曼彻斯特码译码的程序思路或样例?

2015-05-19 11:27:34

基于FPGA的FFT算法研究

2012-08-24 01:09:50

数据,I1′,Q1′,输出到 DSP 中。3.2 计算下行同步码功率(SYNC_DL)模块计算下行同步码功率(SYNC_DL)模块对应于图 2 中的判断部分,是 AGC 中最为重要算法计算

2020-08-14 09:06:10

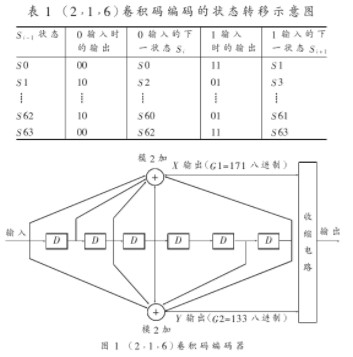

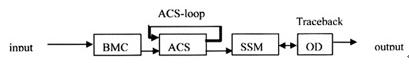

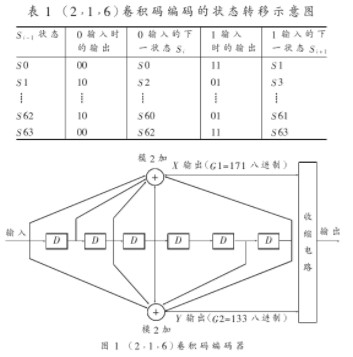

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

2019-11-01 08:05:38

和实测验证,该算法能有效快速地消除回声;同时,该算法应用灵活,能实现多路的回声消除,在VOIP终端设备上具有较强的应用价值和应用前景。页 码:9-11页主 题 词:回声消除VOIPFPGA Echo cancellationVOIPFPGA学科分类:TN91核心收录:暂无

2018-05-08 10:23:36

、同步算法方案论证等相关内容。

引言

扩频威廉希尔官方网站

是通信系统中的重要组成部分,具有低的截获率、信号隐蔽性强、易于组网、多用户随机选址能力强和抗干扰能力强等优点。扩频威廉希尔官方网站

是通过一个独立的码序列、编码及调制

2023-08-23 16:32:43

基于FPGA的模糊PID控制算法的研究及实现

2013-03-18 14:25:05

纠错方法,广泛应用于卫星通信和移动通信中。V iterbi译码算法是用于卷积码译码的一种最大似然算法,采用迭代译码原理。为提高译码性能,Hagenauer提出了软判决V iterbi算法(SOVA),该算法序列检测的概率最大,比硬判决提高2.2 dB。早全文下载

2010-04-26 16:08:39

LDPC码是近年来发展较快且日趋成熟的一种信道编码方案,因其具有的优越性能和实用价值而被人们认知,但由于随机结构的LDPC码编译码器硬件实现较为复杂,具有的准循环特性QC_LDPC码已成为IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等众多标准的信道编码方案。

2019-09-30 07:19:45

SCL语言是什么?SCL语言有何优势?如何使用SCL语言去编写控制算法?

2021-09-22 06:45:08

由于卷积码具有较好的纠错性能,因而在通信系统中被广泛使用。采用硬件描述语言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——现场可编程门阵列)进行数字通信系统设计,可在集成度、可靠性和灵活性等方面达到比较满意的效果。

2019-10-14 06:02:23

一种在FPGA中实现的基于软判决的Viterbi译码算法,并以一个(2,1,2)、回溯深度为10的软判决Viterbi译码算法为例验证该算法,在Xilinx的XC3S500E芯片上实现了该译码器,最后对其性能做了分析。 关键词: OFDM;Viterbi译码;软判决;FPGA

2009-09-19 09:41:24

应用于LTE_OFDM系统的Viterbi译码在FPGA中的实现在 系 统 中 为 了 获 得 正 确 无 误 的 数 据 传 输 要 采 用 差 错 控 制 编 码 技 术 中 采 用和 加 速

2012-08-11 15:27:24

本文通过对长BCH码优化方法的研究与讨论,针对标准中二进制BCH码的特性,设计了实现该译码器的FPGA硬件结构。

2021-06-15 09:23:27

BCH码是目前最为常用的纠错码之一,我国的数字电视广播地面传输标准DTMB也使用了缩短的BCH码作为前向纠错编码的外码。针对该BCH码的特点,采用BM译码算法,设计了一种实时译码器。与其它设计方案

2021-05-25 07:04:32

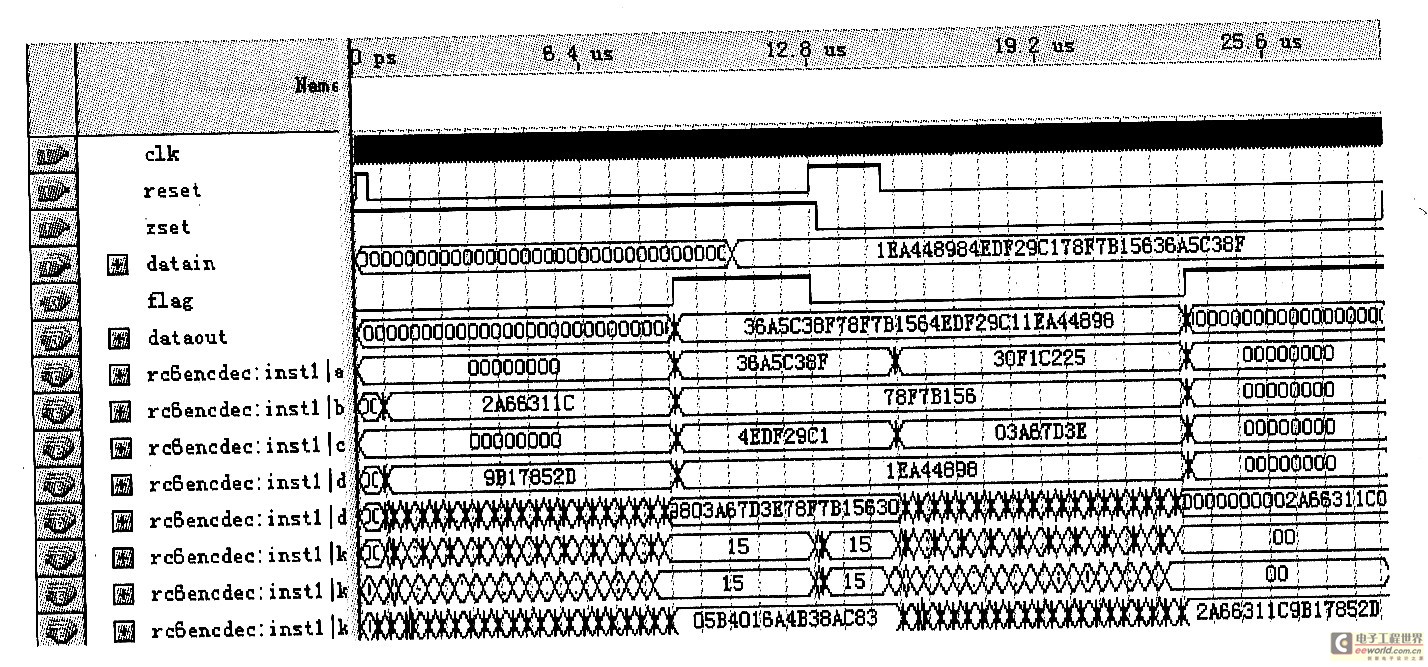

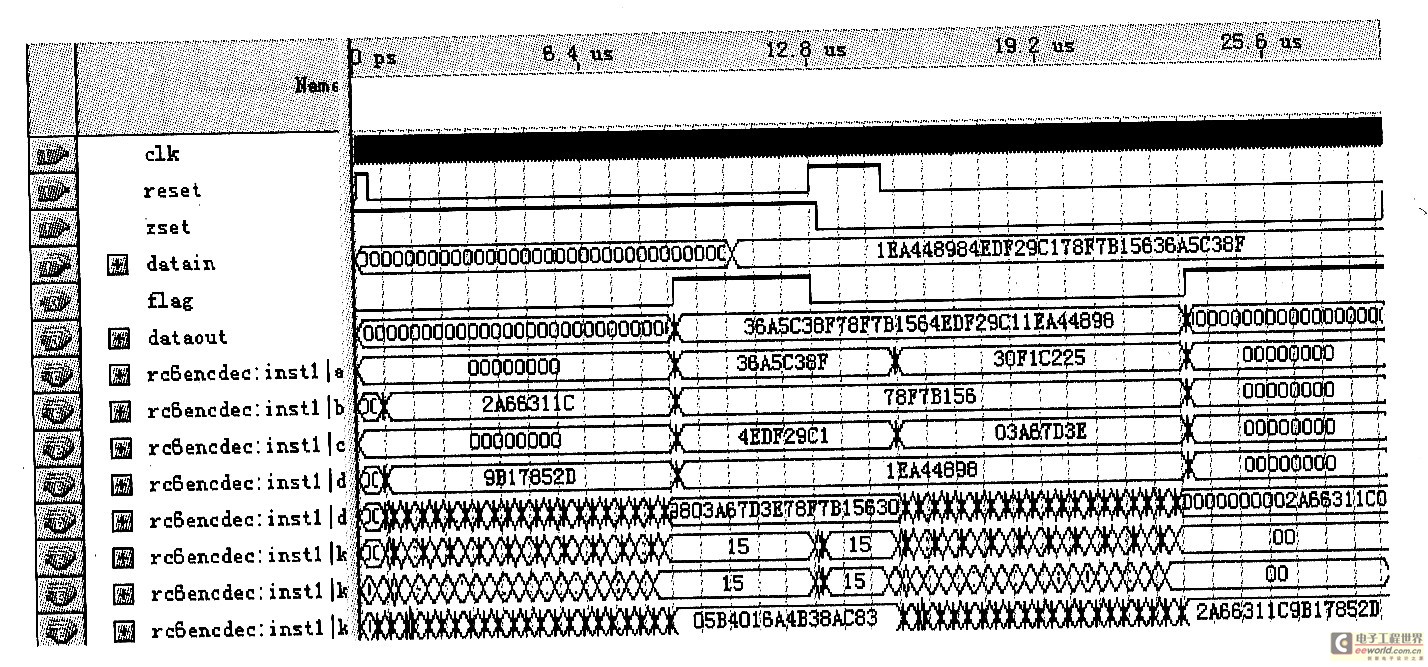

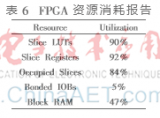

本文研究了RS码的实现方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS编译码器的设计,同时对其进行了仿真和在线调试,并给出了功能仿真图和测试结果。时序仿真结果表明,该编译码器能实现预期功能。

2021-06-21 06:23:53

Turbo码自1993年提出以来[1],由于其接近香农极限的优异译码性能,一直成为编码界研究的热点。近年来,用户对通信质量的要求越来越高,学者们已将研究重点从理论分析转移到Turbo码的实用化上来

2019-08-22 07:28:46

基于FPGA的Turbo码编译码器各模块实现的 VHDL或verilog HDL程序。急求啊谢谢大神啦!!

2015-06-08 22:45:24

截短Reed-Solomon码译码器的FPGA实现提出了一种改进的BM算法,并在此基础上提出了一种大量采用并行结构的截短RS码译码器的实现方式。验证表明,该算法能显著提高基于FPGA的RS译码

2009-09-19 09:39:43

截短Reed_Solomon码译码器的FPGA实现提 出 了 一 种 改 进 的 算 法 并 在 此 基 础 上 提 出 了 一 种 大 量 采 用 并 行 结 构 的 截 短 码译 码 器 的 实

2012-08-11 15:50:06

本帖最后由 eehome 于 2013-1-5 10:04 编辑

指纹识别算法的研究及基于FPGA的硬件实现

2012-05-23 20:14:46

标准中LDPC码的构造、编码及解码算法原理,结合MAT-LAB仿真对其算法有效性进行了分析比较。【关键词】:数字电视传输系统;;低密度奇偶校验码;;DMB-TH;;编译码器【DOI】:CNKI:SUN

2010-04-23 11:36:52

的编码译码电路,并给出了基于EDA仿真软件平台下的电路设计。 关键词:光纤通信 EDA CMI码 目 录 1 绪论 1 1.1 论文选题的理论意义 1 1.2 国内外有关本选题研究

2009-03-25 13:19:20

求一种基于FPGA滑动相关法伪码捕获的研究与实现

2021-04-30 06:52:27

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

编译码的原理是什么?如何对编译码算法进行仿真测试?

2021-04-28 06:54:22

在做HDB3码编译码器的实验,查到资料说FPGA只能处理单极性码,而HDB3码是双极性码。想请教下是所有的FPGA的芯片都只能处理单极性码么?如果是的,那么想处理双极性码的话要加什么样的辅助电路才能用FPGA处理双极性码?

2016-09-14 16:31:36

Reed_Solomon码译码器的FPGA实现快速浮_定点PID控制器FPGA的研究与实现一种密钥可配置的DES加密算法的FPGA实现应用于LTE_OFDM系统的Viterbi译码在FPGA中的实现[hide][/hide]

2012-02-02 17:26:14

不规则重复累计码BP译码算法具有接近Shannon限优越性能,但具有较高的复杂度。为了降低复杂度,提出了IRA码最小和算法和曲线折线化算法。最小和算法具有简单、容易实现的特

2008-11-20 12:12:20 9

9 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架构,实现了码率为1/2,帧长为1008bits的规则(3,6)LDPC码译码器。所采用的最小-和算法相对于传统的和-积算法在不损失译码性能的前提下,

2009-06-06 14:12:20 31

31 基于可靠性更新的低复杂度B译码算法:基于部分符号更新策略的BP (Belief Propagation)译码算法减少了LDPC (Low-Density Parity-Check)码的译码运算量,提高了译码效率。然而在其译码过程中,由

2009-10-29 13:09:21 16

16 该文从译码速率、硬件实现的复杂度和误码率3 个方面对比研究了两种典型的高速译码算法:Turbo 型和积算法与并行加权比特翻转算法。以准循环LDPC 码为对象,给出了Turbo 型和积算

2009-11-25 15:26:58 9

9 文章分析了Turbo 码的MAP 类译码算法后,针对传统Log—MAP 译码算法的特性,提出了一种改进的Log—MAP 译码算法。仿真结果表明,新的算法在降低译码复杂度的同时较好地保持了译

2010-01-15 11:51:47 13

13 针对分组Turbo 码自适应Chase 译码算法存在的缺陷,该文提出自适应量化测试序列数的分组Turbo 码译码算法。该方法以测试序列数C 为研究对象,依出错概率大小选择错误图样,并利用

2010-02-10 12:15:52 3

3 IRA码的译码通常是利用BP译码算法来实现的,但是BP译码算法的硬件电路复杂。为了让译码算法在复杂度和译码性能之间取得较好的折衷,提出一种改进型IRA译码算法,该算法采用偏

2010-07-05 16:23:56 21

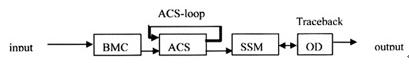

21 Viterbi译码原理

Viterbi译码算法(简称VA算法)是由Viterbi在1967年首先提出的,它是一种针对卷积码的最大似然译码算法。他不是在网格

2009-11-13 18:50:34 7391

7391

利用FPGA来实现RC6算法的设计与研究

引 言

RC6是作为AES(Advanced Encryption Standard)的候选算法提交给NIST(美国国家标准局)的一种新的分组密码。它是在RC5的基础上

2009-12-28 09:20:15 1022

1022

在很多情况下,DTMF译码器输出的数据仍需送入单片机进行相应的运算及处理,进而控制其它各种设备的动作。因此,如果能找到一种基于单片机的DTMF信号的译码算法,再辅之以

2010-07-02 09:55:56 663

663

针对低密度奇偶校验(LDPC)译码算法性能低的问题,提出一种基于最小和的高效译码算法。该算法从概率的角度分析消息的传递过程中校验节点的更新过程,得到近似的最小和算法等式,

2011-05-18 18:54:20 0

0 该文介绍了两种Viterbi 译码器回溯译码算法,通过对这两种算法硬件实现结构上的优化,给出了这两种算法的FPGA 实现方法,比较了两种实现方法的优缺点。最后将其应用在实际的Viter

2011-05-28 15:18:48 33

33 提出了一种新的动态补偿最小和译码算法,并将本算法和修正最小和译码算法进行了性能比较。仿真结果显示,动态补偿最小和译码虽然算法迭代的收敛速度有所减慢,但具有比修正最

2011-10-08 15:05:33 27

27 针对Turbo乘积码(TPC)译码复杂度高、运算量大的缺点,分析了一种改进的TPC译码算法。该算法以Chase迭代算法为基础,通过对错误图样重新排序产生新的测试序列,其伴随式可从前次伴

2011-12-05 14:07:55 20

20 利用ME算法实现结构设计了一种低资源占用率、低成本的高速RS译码器。逻辑综合及仿真结果表明,基于Altera公司CycloneII系列FPGA的RS(255,239)译码器,工作时钟达210 MHz,可满足数据速率1.68 Gb

2011-12-15 17:23:28 28

28 在描述置信传播(BP)译码算法基础上, 研究和分析了两种降低复杂度的译码算法。Min.Sum 算法主要讨论了简化校验节点的消息更新运算,并应用密度进化方法对此算法进行极限性能分析

2012-03-31 15:22:03 7

7 本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68 低密度奇偶校验码(LDPC码)译码主要包括基于硬判决和基于软判决的译码。文章对这两种译码方法中的典型算法(BF算法和BP算法)和一种改进的对数域算法(APP-LLR算法)进行了仿真研究;比较并分析

2016-01-04 17:13:49 13

13 基于FPGA的JPEG解码算法的研究与实现,很好的资料,快来学习吧

2016-02-18 13:53:55 0

0 基于FPGA的RS码电路设计,编码译码原理。

2016-03-30 16:32:42 2

2 基于FPGA的模糊PID控制算法的研究及实现-2009。

2016-04-05 10:39:29 20

20 截短Reed_Solomon码译码器的FPGA实现

2016-05-11 11:30:19 11

11 应用于LTE_OFDM系统的Viterbi译码在FPGA中的实现

2016-05-11 11:30:19 11

11 CCD图像的颜色插值算法研究及其FPGA实现

2016-08-29 15:02:03 12

12 基于FPGA的JPEG解码算法的研究与实现

2016-08-29 16:05:01 11

11 基于FPGA的数字信号处理算法研究与高效实现

2016-08-29 23:20:56 39

39 一种基于改进线性规划的LDPC码混合译码算法_陈紫强

2017-01-07 16:52:06 0

0 基于FPGA的ECC快速算法研究及设计_陈俊杰

2017-01-07 19:08:43 2

2 基于FPGA的3B4B编译码电路

2017-02-07 14:58:18 11

11 电解极化渗流传感器极化特性研究_秦孙巍

2017-03-19 19:03:46 0

0 改进的MIMO系统球译码检测算法_仵丹

2017-03-19 19:04:23 2

2 在二进制离散无记忆信道中极化码可以达到其信道极限容量,并且实现的复杂度较低,这在通信领域无疑是一个重大突破,因此在FPGA中实现极化码的译码有着非常重要的研究意义。首先介绍了SC

2017-11-15 16:50:25 4340

4340

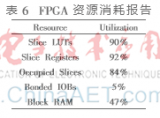

采用易于FPGA实现的归一化最小和算法,通过选取合适的归一化因子,将乘法转化成移位和加法运算。在高斯白噪声信道下,仿真该译码算法得出最佳的译码迭代次数,并结合Xilinx XC7VX485T资源确定

2017-11-16 12:59:01 2766

2766

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

中小长度的数据报文业务为主,所以突发通信中的Turbo码的码长也是中等长度以下的。本文面向突发数据通信中的信道编码应用,研究了短帧长Turbo码编译码算法的FPGA实现。实现中采用了优化的编译码算法,以降低译码复杂度和译码延时。最后仿真和测试了Turbo译码器的纠错性能和吞吐量。

2018-07-12 08:15:00 3247

3247

不规则重复累积码(IRA)的译码通常采用置信传播(BP)译码算法,然而BP译码算法需进行双曲正切函数计算,复杂度高,不利于硬件实现。为此,提出一种基于分段函数修正和预检测机制结合的译码算法,通过对折

2018-01-08 15:52:39 0

0 卷积码是广泛应用于卫星通信、无线通信等各种通信系统的信道编码方式。Viterbi算法是一种最大似然译码算法。在码的约束度较小时,它比其它概率译码算法效率更高、速度更快,译码器的硬件结构比较简单。随着

2019-04-24 08:29:00 2635

2635

信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

2019-07-11 08:01:00 2822

2822

欧几里德算法,它不需要进行多项式次数的判断,能够降低译码的复杂度,减少硬件电路的复杂性,提高译码速度.在VCS软件中进行FPGA仿真,结果表明:当误码个数不同时该算法可以达到预期的效果.

2021-02-01 14:25:00 10

10 针对一类规则(r,c)-LDPC(low-density parity check)码,提出了一种基于Turbo译码算法的高吞吐量存储器效率译码器。与传统的和积译码算法相比,Turbo译码算法对多个

2021-02-03 14:46:00 9

9 给出了跳频系统中 Turbo码译码器的FPGA( field programmable gate array)实现方案。译码器采用了MaxLog-map译码算法和模块化的设计方法,可以

2021-04-01 11:21:46 5

5 基于FPGA的800Mbps准循环LDPC码译码器

2021-06-08 10:31:31 26

26 关于Actel 的FPGA的译码器的VHDL源代码(通信电源威廉希尔官方网站

期刊2020年第14期)-关于Actel 的FPGA的译码器的VHDL源代码。适合感兴趣的学习者学习,可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 10

10 一听到三八译码器这个东西可能会感觉有点熟悉,其实在STC89C51系列单片机中,里面就有一个三八译码器,就是一开始的流水灯程序,LED0-7这八个LED!但是怎么在FPGA中实现三八译码器呢?其实很简单。

2023-04-26 15:38:21 1787

1787

均为LLR,其中S代表计算层数,i代表相应码字标号。

均为LLR,其中S代表计算层数,i代表相应码字标号。

电子发烧友App

电子发烧友App

评论