1 引言

电子系统功能实现的模式不外硬件和软件两种。基于冯。诺依曼或者哈佛体系结构的通用微处理器(MPU、MCU、DSP等)系统是软件实现模式,其硬件电路结构固定,通过串行执行指令实现功能。软件设计灵活、易升级,但执行速度慢、效率低;而专用集成电路(ASIC)采用硬件模式,通过固化的特定运算和单元电路完成功能。指令并行执行,执行速度快、效率高,但开发周期长、缺乏灵活性。在一些实时性和灵活性要求都比较高的场合,采用通用微处理器或者ASIC效果都欠佳。

大规模的电子系统是各种逻辑功能模块的组合。从时间轴上来看,系统中的各个功能模块并不是任何时刻都在工作,而是根据系统外部的整体要求,轮流或循环地激活或工作。随着系统规模的扩大,各功能模块电路的资源利用率反而下降。因此,系统设计要从传统的追求大规模、高密度的方向,转向如何提高资源利用率上来,充分利用有限的资源去实现更大规模的逻辑设计。

基于大规模可编程器件FPGA的可重构系统(Reconfigurable System),就是利用FPGA可以多次重复编程配置的特点,实现实时电路重构(Reconfiguration of circuitry at runtime,简称RCR),即在电子系统的工作状态下,动态改变电路的结构,其实质是实现FPGA内部全部或部分逻辑资源的时分复用,使在时间上离散的逻辑电路功能能在同一FPGA中顺序实现。

虽然可重构系统的概念早在1960年就已经提出来,但由于没有理想的可重构器件等原因,这方面的研究一直没有很大突破。1990年以来,随着大规模集成电路的迅速发展,尤其是大规模可编程器件FPGA的出现,研制可重构电子系统的硬件条件已基本具备,实时电路重构的思想逐渐引起了学术界的注意,从而引发了对可重构系统的研究热潮。自从2000年以来,基于FPGA的重构在国际上得到了越来越多的关注和研究。

2 FPGA可重构设计的基础

2.1 FPGA可重构设计的结构基础

可重构设计是指利用可重用的软、硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。FPGA器件可多次重复配置逻辑的特性使可重构系统成为可能,使系统兼具灵活、便捷、硬件资源可复用等性能。

FPGA器件的结构主要有两种:一是基于反熔丝威廉希尔官方网站 ,二是基于SRAM或FLASH编程。用反熔丝开关作基本元件,具有非易失性,编程完成后,FPGA的配置数据不再变化,无法重构。而基于SRAM或FLASH编程的FPGA通过阵列中的SRAM或FLASH单元对FPGA进行编程。SRAM单元由一个RAM和一个PIP晶体管组成,RAM中储存着PIP晶体管的通断信息,系统上电时,这些信息码由外部电路写入到FPGA内部的RAM中,电源断开后,RAM中的数据将丢失。因此SRAM或FLASH编程型FPGA是易失性的,每次重新加电,FPGA都要重新加载数据。这样,运行中的FPGA功能系统在掉电后可以重新下载新的配置数据,以实现不同的功能。这一特点成为FPGA在许多新领域获得广泛应用的关键,尤其成为可重构系统发展的持续驱动力。

2.2 FPGA的重构方式

根据重构的方法不同,FPGA的重构可分为静态重构和动态重构两种,前者是指在系统空闲期间进行在线编程,即断开先前的电路功能后,重新下载存贮器中不同的目标数据来改变目标系统逻辑功能。常规SRAM FPGA都可实现静态重构。后者则是指在系统实时运行中对FPGA芯片进行动态配置(即在改变电路功能的同时仍然保持电路的工作状态),使其全部或部分逻辑资源实现在系统的高速的功能变换和时分复用。动态重构威廉希尔官方网站 需要特定的基于SRAM或FLASH结构的新型FPGA的支持。随着其产品和威廉希尔官方网站 的相对成熟,动态重构FPGA的设计理论和设计方法已经逐渐成为新的研究热点。

根据实现重构的面积不同,可重构FPGA又可以分为全局重构和局部重构。

(1)全局重构:对FPGA器件或系统能且只能进行全部的重新配置,在配置过程中,计算的中间结果必须取出存放在额外的存储区,直到新的配置功能全部下载完为止。重构前后电路相互独立,没有关联。通常,可以给FPGA串连一个EPROM来存储配置数据,实现前后功能的转化。常规基于SRAM的FPGA的静态重构均为全局重构。

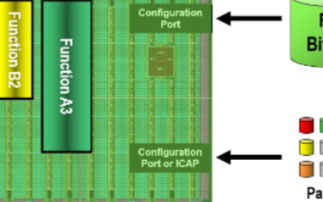

(2)局部重构:对重构器件或系统的一部分进行重新配置,重构过程中,其余部分的工作状态不受影响。这种重构方式减小了重构范围和单元数目,FPGA的重构时间大大缩短,占有相当的速度优势。应用FPGA动态部分重构功能使硬件设计更加灵活,可用于硬件的远程升级、系统容错和演化硬件以及通信平台设计等。动态部分重构可以通过两种方法实现:基于模块化的设计方法(Module-Based Partial Reconfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration)。

显然,动态重构比静态重构优越,因为静态重构将整个内部的逻辑单元都重新配置,此时FPGA被挂起不能执行正常操作,重构完成后才能恢复工作,影响系统实时性。动态重构在系统运行中能实时全部或部分重构,且不中断正常逻辑输出,因而更有灵活性和高速度。

大多数FPGA都是基于LUT查找表结构,它们只适用于静态重构,通过向LUT一次下载全部配置数据而设定FPGA的逻辑功能。根据FPGA的容量不同、配置方式不同,全部重构时间为几ms到几秒不等。

对于常规FPGA来说,重载方式多种多样。在系统调试阶段,一般是通过JTAG电缆从主机下载配置数据,调试结束后正式运行时一般是将配置数据放在串行PROM中,上电时向FPGA加载逻辑。但对于系统实际运行还有一些更快更灵活的配置方式,可以缩短FPGA的重构时间,实现灵活重构。如ALTERA公司的FPGA可采用串行被动(PS)方式配置,对于2万逻辑门规模的EP1K10配置数据为20KB,在30MHz的配置时钟下只要5ms即可全部重构。这个速度虽然比不上动态配置的FPGA,但也比JTAG下载、串行PROM配置方式快多了,姑且称之为准动态重构(bogus dynamic restructuring)。而且在许多系统中FPGA并不时刻都在工作,而是以一定的重复频率执行任务,只要在FPGA的空闲时间来得及对其进行重新配置,那么在系统宏观的角度就可以认为是动态配置的,即实时重构。

2.3 支持重构的FPGA器件

近年来,随着FPGA威廉希尔官方网站 的发展,支持重构的FPGA器件新品迭现。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表结构。Xilinx支持模块化动态部分重构的器件族有XC6200系列,90nm工艺Spartan-3和Virtex-4 、Virtex-II-E和Virtex-II Pro [7]。Acmel公司的AT6000系列同样基于SRAM结构,只是SRAM的各单元能够单独访问配置,即支持部分重构。Lattice公司的基于Flash的FPGA通过在Flash上存储多种逻辑功能的配置数据流,经过配置实现不同逻辑功能,严格意义上讲属于静态可重构威廉希尔官方网站 。Altera公司的Flex系列、ACEX、APEX、Cyclone系列也是基于SRAM的可重构逻辑。支持重构的FPGA器件有数量逐渐增加的趋势。但目前价格相对偏高。

3 基于FPGA的可重构系统结构分析

由于可重构系统的研究历史很短,目前尚未形成标准的结构形式,在此仅根据已有的应用做初步分析。

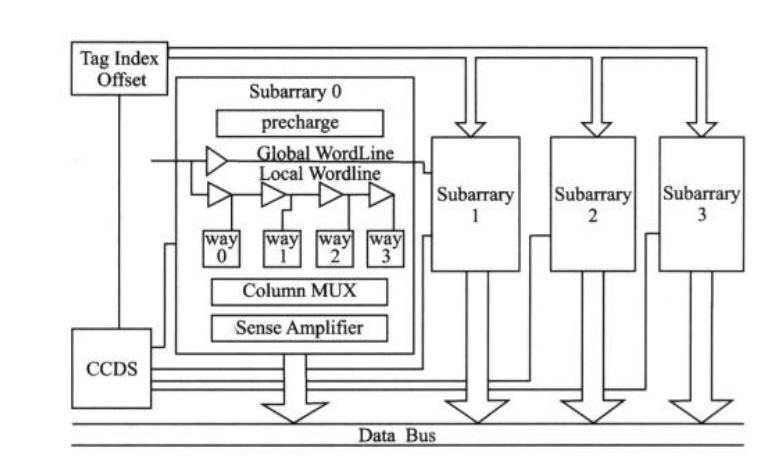

按重构的粒度和方式,可重构系统可以粗略地分为两种。一种是粗粒度重构单元的模块级重构,即重构时改变某一个或若干个子模块的结构。此时不仅电路逻辑改变,连线资源也重新分配。重构所需的电路输出配置信息事先由编译软件生成。通常重构时系统需要暂停工作,待重构完成后再继续。这种重构系统设计简单,但灵活性不足,且有时不能完全发挥出硬件运算的效率。较适合应用于嵌入式系统中。

另一种细粒度的重构单元的元件级重构,即重构时仅改变若干元件的逻辑功能。通常情况下重构时连线资源的分配状况不作修改,重构所需的电路配置信息在系统运行过程中动态产生。重构时系统可以边重构边工作。这种重构系统设计复杂,但灵活性大,能充分发挥出硬件运算的效率,较适合高速数字滤波器、演化计算、定制计算等方面的应用。

从现有的可重构系统组织结构看,可以根据应用类型加以区分,在中低端应用中,主要采用通用微处理器MPU(MCU/DSP)+FPGA形式;在高端应用中,主要采用处理器集成型,即将处理器、存储器、I/O口、LVDS、CDR等系统设计需要的资源集成到一个FPGA芯片上,构建成一个可编程的片上系统SoPC(System on Programmable Chip)。

3.1 MPU+FPGA结构的可重构系统的结构特点

通用微处理器具有良好的接口功能,便于构建可重构系统。按照MPU与FPGA之间的相互关系以及在系统中所起的作用,主要可以分为两类:MPU控制FPGA工作的可重构系统和MPU协同FPGA工作的可重构系统。

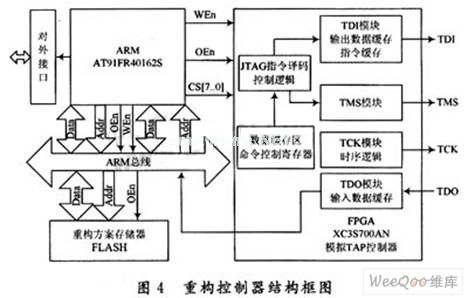

3.1.1 MPU控制FPGA工作的可重构系统

这类系统采用MPU作为系统的控制核心,在FPGA中实现控制器的外设电路功能。实质上,这是传统MPU控制系统的继承与发展,根据系统需要,在FPGA中定制实现各分立的外部设备与接口,如SRAM、键盘与显示接口以及总线的扩展等应用。

例如在某多通道超声信号高速采集处理系统中,所需处理的数据流庞大,对它的处理是计算密集型任务。采用DSP+FPGA结构模式,以FPGA作为DSP的协处理器,能够以硬件的速度进行并行计算,同时利用其在线可重构特性,灵活地改变内部逻辑配置来完成多种不同算法的任务。

由于主要控制任务在MPU上实现,系统逻辑实现的重点在编制MPU程序上,而FPGA则更多地使用IP (Intellectual Property)核实现基本功能模块,软件开发在整个系统设计过程中所占比重较大。

3.1.2 MPU协同FPGA工作的可重构系统

这类系统通常以可编程逻辑器件为核心,在其内部实现面向应用的逻辑控制功能(通常以状态机FSM实现),而MPU则占据次要地位(充当FPGA控制器的外设)。应该说,这类系统充分利用了可编程逻辑器件和MCU的特点,实现了优势互补。它主要应用在面向实时性应用、并行处理以及高速等环境中。例如,使用高密度FPGA进行多路A/D高速采样,经内部处理模块处理后,并行输出结果,整个过程的时序控制在FPGA内部实现;而MPU只负责对FPGA各功能模块的参数装载、启动命令发送及FPGA工作状态监控等外围任务。

这类系统的开发重点主要在FPGA逻辑功能的硬件实现上,而MPU的控制软件比较简单。

在实际应用中,系统的特点并不像以上两种类型这么明显,普遍存在的是兼具以上特点的系统,只是所占比重不同而已。

3.2 单片FPGA上的SoC—SoPC

将片上系统SOC和FPGA各自的优点相结合,实现现场可编程、可重构的新型SoC就是片上系统SoPC。

以Altera Stratix FPGA器件为例,Stratix体系把硬件、软件和IP功能从威廉希尔官方网站 上融合到基于模块的设计中。这个新的体系结构采用CPU软核Nios和DirectDriveTM的MultiTrackTM互联布线结构。Nios II系列32位嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛的嵌入式应用。可编程的NiosII核含有许多可配置的接口模块,用户可根据设计要求,利用Altera的Quartus II软件以及SoPC Builder工具,允许设计者轻松地将Nios II处理器嵌入到他们的系统中。用户还可通过Matlab和DSP Builder,或直接用VHDL等硬件描述语言,为NiosII嵌入式处理器设计各类硬件模块,并以指令的形式加入到NiosII的指令系统中,使其成为NiosII系统的一个接口设备,与整个片内嵌入式系统融为一体,而不是直接下载到FPGA中生成庞大的硬件系统。正是NiosII所具有的这些重要特点,使得可重构SoPC的设计成为可能。市场上流行的SoPC器件厂商Xilinx和Altera都提供功能强大的SoPC设计平台,并提供大量的IP核和参考设计,这是SoPC的一大优势。

当然,可重构系统的形式并没有完全定型,各类型间的分界是非常模糊的,甚至是交叉重合的。可以预见,随着可重构威廉希尔官方网站 的发展,还会有新的系统结构出现。

4 基于FPGA的可重构系统的应用简析

基于FPGA的可重构系统优越的应用性能主要体现在:①能以硬件的速度执行算法,同时又具有灵活的可配置性;②当作缓存逻辑,在不同的时间段向FPGA加载不同的逻辑配置,实现硬件复用,提高资源利用率,减小系统规模功耗;③可构造主动式数字容错系统,在系统发生故障时重新配置FPGA达到自修复;④实现可进化的硬件,对不断变化的环境能迅速适配;⑤可使设计者用更为简单的硬件和更短的设计周期来实现更多的功能,降低系统的成本。因此,基于FPGA的可重构系统在军事目标匹配、声纳波束合成、基因组匹配、图像纹理填充、遗传学方面基因组分析、集成电路的计算机辅助设计、网络安全、光互连、高速数字滤波器、图像压缩、嵌入式系统等方面,都有着广泛的应用前景。相信随着FPGA威廉希尔官方网站 的发展,该威廉希尔官方网站 将进入更多应用领域,为人类带来更多的便利。

电子发烧友App

电子发烧友App

评论