时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。

2016-05-29 23:25:10 1064

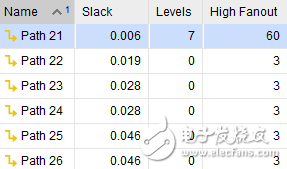

1064 时序不满足约束,会导致以下问题: 编译时间长的令人绝望 运行结果靠运气时对时错 导致时序问题的成因及其发生的概率如下表: 由上表可见,造成时序问题的主要原因除了约束不完整,就是路径问题,本文就时序

2020-11-29 10:34:00 7410

7410 时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

/ 1555.4 IP的属性与状态 / 1565.5 IP的约束 / 1595.6 封装IP / 1645.6.1 通过Vivado工程封装用户代码 / 1645.6.2 通过指定目录封装用户代码

2020-10-21 18:24:48

,而ISE需要综合的时候才能发现。5、添加约束——点评:由于ISE添加MMCM时没有加入自动生成的约束,需要重新添加时钟约束。而Vivado自动将IP核添加到工程内,是包含时钟约束的。为了更好的ISE

2021-01-08 17:07:20

出于某种原因,Vivado忽略了我的约束文件,当我尝试在tcl控制台中逐个输入约束时,我尝试分配的每个端口都会出现以下错误:set_property PACKAGE_PIN T19

2018-11-06 11:36:22

使用Vivado 2015.4我生成了两个FIFO和一个Aurora Core。我收到与Vivado自动生成的时序约束相关的严重警告。由于我的FIFO在整个设计中被多次使用,我需要一种让Vivado

2018-11-02 11:30:10

(约束指令介绍)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

那位高人指点一下啊,怎么给差分时钟添加时序约束啊

2013-08-08 20:58:34

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

怎么进时序约束的,时序约束是自己输进去的

2014-01-17 15:10:43

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

vivado默认计算所有时钟之间的路径,通过set_clock_groups命令可禁止在所标识的时钟组之间以及一个时钟组内的时钟进行时序分析。 1.异步时钟组约束声明两时钟组之间为异步关系,之间不进行时序

2018-09-21 12:40:56

、Vivado基本操作流程2、时序基本概念3、时序基本约束和流程4、Baselining时序约束5、CDC时序约束6、I/O时序7、例外时序约束8、时序收敛优化威廉希尔官方网站

2018-08-01 16:45:40

小弟刚学习FPGA不久,仅仅学习了一个普通工作流,但对于时序约束什么的几乎一无所知最近在编一个模块时,VIVADO综合实现出来Timing那里是红色,WNS TNS为负值,只知道似乎是当前布线延迟

2015-09-06 20:08:42

。

时序约束可以让VIvado和Quartus等FPGA开发软件,在布线时检测综合出来的逻辑电路是否满足这个时序要求,并生成时序报告。

一、建立/保持时间

1、基本概念

设定时序约束的目的就是为了满足

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

通过对设计施加精准的控制来获得可靠的时序收敛结果。对设计中的每一个寄存器手工进行布局位置约束并保证时序收敛是一项浩大的工程,这标志着设计者能够完全控制设计的物理实现。这是一个理想目标,是不可能

2017-12-27 09:15:17

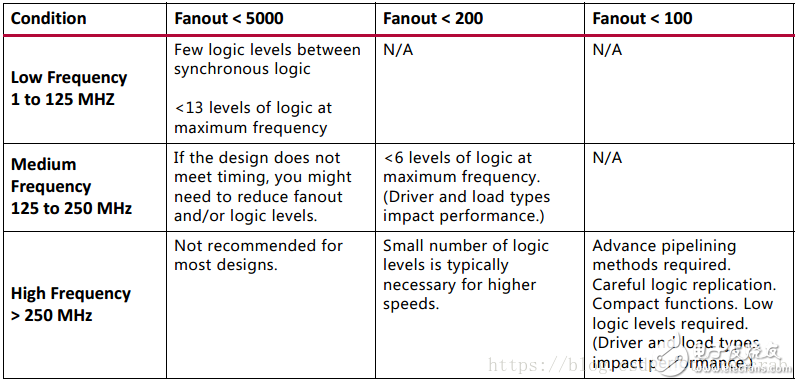

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名为“Clocking Wizard v5.3”的IP来配置为我的项目输出系统时钟的MMCM。自定义此IP后,将自动为IP生成约束

2019-08-02 09:54:40

本手册通过一个示例工程,讲解了使用 TD 和 Vivado 下时序约束的对比,详细对比了时序约束的命令、时序约束结果的展示以及部分时序路径。

2022-10-27 06:21:47

明德扬时序约束视频简介FPGA时序约束是FPGA设计中的一个重点,也是难点。很多人面对各种时序概念、时序计算公式、时序场景是一头乱麻,望而生畏。现有的教材大部分是介绍概念、时序分析工具和计算公式

2017-06-14 15:42:26

是精确到寄存器或LE一级的细粒度布局约束。设计者通过对设计施加精准的控制来获得可靠的时序收敛结果。对设计中的每一个寄存器手工进行布局位置约束并保证时序收敛是一项浩大的工程,这标志着设计者能够完全控制

2017-10-20 13:26:35

1,创建工程打开Vivado软件,点击新建工程。根据向导创建工程,以下以Xilin 7020开发板为例,进行介绍。注意:I,设置工程的名称,在这个步骤中可以勾选“Create project

2023-04-05 23:21:24

关于静态分析和时序约束的文章

2014-07-17 12:12:35

刚刚开始学习Altera FPGA的时序约束,照着特权同学的一个例子做的 但是出现了下面的问题工程代码:modulequest_test(clk,rst, led);input clk,rst

2014-03-20 12:51:21

使用xdc文件进行管脚、位置、时序和属性等约束的时候,经常会使用各种get命令。Vivado提供了很丰富的匹配表达式,比如等于==、不等于!=、匹配=~、不匹配!~、《、》、《=、》=等等,这些

2021-01-26 07:03:16

一直对时序约束没有什么概念,向各位大神求教经验及可以拜读的资料

2017-04-11 21:42:03

时,老是范糊涂,因为Quartus II和ISE对IO端口的约束方式和计算公式略有不同,容易混淆。而老掉牙的ISE中也只是光秃秃的没有任何提示,Vivado可好了,出现了标好了具体约束值的时序图

2016-01-11 16:55:48

网上找到一个介绍,偏移约束也是一类基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,只能用于端口信号,不能应用于内部信号我现在将一个输入时钟clk0经过一个DCM产生clk1 ,然后

2017-04-27 16:12:30

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

时序约束文件SDC支持哪些约束?

2023-08-11 09:27:15

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 时序约束的概念 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(STA, IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 By Adam Taylor 在之前的博客中介绍了Vivado的基本时序约束,时序约束定义了系统频率或自己所定义的时钟频率。为建立良好的时序约束,下一步是需要建立时钟路径之间关系的定义。这样

2017-02-08 03:46:35 194

194 偏移约束。 这里先说一下周期约束:周期约束是为了达到同步组件的时序要求。如果相邻同步原件相位相反,那么延迟就会是时钟约束值的一半,一般不要同时使用上升沿和下降沿。注意:在实际工程中,附加的约束时间为期望值的

2017-02-09 02:56:06 605

605 最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到 VIVADO 的 XDC 约束,不仅浪费时间,而且容易出错,这里介绍一种方法可以实现两种约束的切换。

2017-03-24 13:54:36 8529

8529

的关系。工程师利用这类约束确定是否有必要对路径进行分析,或者在时钟路径之间不存在有效的时序关系时忽视路径。

2017-11-17 05:23:01 2417

2417

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

过程必须以满足XDC中的约束为目标来进行。那么: 如何验证实现后的设计有没有满足时序要求? 如何在开始布局布线前判断某些约束有没有成功设置? 如何验证约束的优先级? 这些都需要用到Vivado中的静态时序分析工具。

2017-11-17 18:03:55 34003

34003

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

。 在添加全局时序约束时,需要根据时钟频率划分不同的时钟域,添加各自的周期约束;然后对输入输出端口信号添加偏移约束,对片内逻辑添加附加约束。

2017-11-25 09:14:46 2347

2347 详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 14208

14208

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 6374

6374 来维持吗? 1、Vivado基本操作流程 2、时序基本概念 3、时序基本约束和流程 4、Baselining时序约束 5、CDC时序约束 6、I/O时序 7、例外时序约束 8、时序收敛优化威廉希尔官方网站

2018-08-06 15:08:02 400

400 时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 5787

5787

了解时序约束向导如何用于“完全”约束您的设计。

该向导遵循UltraFast设计方法,定义您的时钟,时钟交互,最后是您的输入和输出约束。

2018-11-29 06:47:00 2702

2702

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 3077

3077

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 4315

4315 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

2021-01-11 17:44:44 8

8 时序冲突的概率变大以及电路的稳定性降低,为此必须进行时序、面积和负载等多方面的约束。

2021-06-15 11:24:05 2874

2874

A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 4401

4401 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-10-11 10:23:09 4861

4861

很对人在使用Vivado时喜欢使用多个约束文件对整个工程进行约束,同时Vivado允许设计者使用一个或多个约束文件。虽然使用一个约束文件对于一个完整的编译流程来说看似更方便,但是在一些情况下,这会

2021-10-13 16:56:54 6309

6309 Vivado下set_multicycle_path的使用说明 vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3462

3462

XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

2848 很多读者对于怎么进行约束,约束的步骤过程有哪些等,不是很清楚。明德扬根据以往项目的经验,把时序约束的步骤,概括分成四大步

2022-07-02 10:56:45 4974

4974

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2922

2922

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建

2022-08-02 09:54:20 1797

1797

提到位置约束,我们会想到手工布局的方式,即画Pblock,将指定模块放入相应Pblock内,这既是面积约束又是位置约束,但显然这种约束是较为具体的位置约束。这种方式需要工程师有一定的经验,有时还需要

2022-11-17 11:47:46 1381

1381 在描述时序约束时,一个重要的原则是确保约束简洁高效。简洁高效意味着约束只针对指定的对象,即约束对应的对象的个数

2023-02-23 09:03:38 855

855 本章节主要介绍一些简单的时序约束的概念。

2023-03-31 16:37:57 928

928

对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20:31 2368

2368

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 372

372

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 829

829

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 694

694 本小节对时序约束做最终的总结

2023-07-11 17:18:57 351

351

本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17:37 417

417

时序约束出现时序违例(Slack为负数),如何处理?

2023-07-10 15:47:06 3099

3099 电子发烧友网站提供《Vivado Design Suite用户指南:使用约束.pdf》资料免费下载

2023-09-13 15:48:39 0

0 有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291

电子发烧友App

电子发烧友App

评论