to my logic My question is: In my .UCF timing constraints for clocking, I have ONLY specified

2019-02-28 06:24:28

:FTM0_Ch0_Ch1_IrqHandler 第 287 行: 如果 (chan0IntFlag && g_ftmChannelRunning[0][0]) { TIMING_Ftm_IrqHandler(0U, 0U

2023-03-29 08:20:52

见 AD5700 DatsSheet Page9,Carrier Detect Off Timing:请问图中红圈标记的RXD波形是如何来的呢?在示波器上也观察到了此现象,这个波形对于UART

2018-12-14 09:22:48

如果没有 Bluetooth SIG 分配的Company Identifiers , 那么,在广播数据中使用Manufacturer Specific Data(0xFF)会不会违规呢?

2023-10-24 15:50:21

and/or timing constraints on the callback for receiving vendor commands.I added some debug

2019-06-11 11:03:02

suitable topology and Determine IO choices? Timing margin calculation? Setup constraints? Other

2009-11-19 09:59:04

ISE Timing Anlayzer report 是看post-map 还是 post-place&route我现在有个工程 post-map 有错post-place&route 通过这该以哪个为准

2017-08-24 14:15:26

本帖最后由 beHancock 于 2020-3-8 16:14 编辑

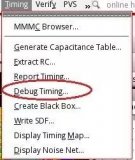

如题。补充几个图//-----------------------------------------这个目录上Static Timing的图标都和其它的不一样了。。。

2020-03-07 22:43:51

seem to be lost. For example, if I click on "Edit timing constraints", no constraints

2018-11-06 11:34:53

最近用到sopc,设计片外ram,故整理“SOPC中SDRAM controller 的Timing配置”一文以备忘。Timing选项:CAS latency cycles(CAS等待时间):即为

2012-03-01 10:20:50

在使用库函数(3.5版本),将通用定时器选用TIM_OCMode_Timing模式,同时使能4个通道中断,可是进不了定时器的中断函数。当选择TIM_OCMode_Toggle模式时,就能进入到中断

2019-09-19 17:42:20

smartxplorer on a design to get an implementation that meets timing constraints on a Virtex 6 FPGA and I

2018-10-22 10:59:44

Vivado toolchain in batch mode for the same project (everything is identical: scripts, constraints

2018-10-25 15:26:07

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合威廉希尔官方网站

是数字IC设计师必须掌握的一项核心威廉希尔官方网站

。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:52:39

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合威廉希尔官方网站

是数字IC设计师必须掌握的一项核心威廉希尔官方网站

。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:55:20

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:12:57

fpga_timing威廉希尔官方网站

文档 xilinx官方

2016-08-17 09:02:16

niScope Configure Horizontal Timing 的说明中,参数number of records,根据我的测试,应该是设置获取信号的通道数。但min record

2018-01-09 15:44:28

38-35] Done setting XDC timing constraints.INFO: [Timing 38-2] Deriving generated clocks

2018-11-08 11:38:17

However, after "keep hierarchy = yes" was setted, the timing constraints can not be meeted. Any ways can solve this? Thanks!Best Regardsyhm

2019-03-28 13:38:35

因为Spartan 6不是PVT压缩甚至使用了相位检测。以上来自于谷歌翻译以下为原文Assuming that there are no timing/coding mistakes =>How

2019-07-17 14:24:02

to!! ---------------+---------+---------+---------+---------+ Timing summary: --------------- Timing errors: 0Score: 0(Setup/Max: 0, Hold: 0) Constraints

2019-02-26 10:15:03

一步了,下面就可以在Constraints里面修改你自己需要的间距了(根据你们的制版工艺水平)。这样就只影响铺铜的间距,不影响各层布线的间距了。

2019-07-08 07:54:19

。以上来自于谷歌翻译以下为原文Hi, I'm using Virtex II Pro and ISE 8.2.03i. My design don't meet timing constraints

2018-09-28 16:56:30

我想知道你们是如何学习计时教师的,你有没有推荐的书或博客或教程?感谢帮助。以上来自于谷歌翻译以下为原文How to write an advanced Timing constraint? I use

2019-03-27 09:58:42

FPGA开发板,工程编译后,Timequest timing analyzer 显示红色,是否是错误,需要改正?编译结果中,messages框中,并没有错误,只是有一些警告,这样看来,是不是那个timequest并不需要改正,也不会影响工程烧录和运行?(见下图)求指点

2019-04-22 15:37:41

View specific resources regardless if they are used or not, For example I want to see how many

2018-10-30 18:02:58

喜我在Windows XP上安装了xilinx ISE 10.1。我在地图中遇到了一些时间问题,所以我在ISE的tcl窗口中将xil_timing_allow_impossible设置为1。地图经历

2019-03-05 07:48:54

run place: ERROR: [Place 30-467] Based on the user constraints, this design needs to place 17 BUFG

2018-10-30 18:02:31

the issue, but to no avail. Are there other timing constraints that I am missing that would have

2019-03-01 11:36:19

shows the failing constraints (preceded with an Asterisk (*)). Please use the Timing Analyzer (GUI

2019-02-21 10:15:31

;Edit Timing Constraints" for Synthesis flow and that runs perfectly (I see the defined

2018-10-29 11:50:01

求一种MCU Specific Package单片机的具体解决方案

2021-12-10 07:46:15

玩转Vivado之Timing Constraints特权同学,版权所有最近在熟悉Xilinx已经推出好几年的Vivado,虽然特权同学之前已经着手玩过这个新开发工具,但只是简单的玩玩,没有深入

2016-01-11 16:55:48

MIPI CS2 input timing和CX3 mipi interface configuration 的关系是什么?

CX3 mipi interface configuration中的值设置成什么是合理的?

2024-02-29 07:25:02

在quartus的仿真里面有两种选项,functional simulation和timing simulation,请问他们的区别是什么?

2019-07-29 05:52:59

在TMS320C6748 DSP Technical Reference Manual中看到某一外设的描写,然后看到想要查看更多关于此外设的介绍,see your device-specific

2020-05-25 07:36:18

请问主机如何获取广播中 GAP_ADTYPE_MANUFACTURER_SPECIFIC后面的数据?

2022-08-10 06:06:38

timing and (maybe) area constraints.I am at the feasibility stage of the whole project and I’m looking

2018-09-30 11:09:49

design it says that the timing constraints cant be matched "There are 2 failing constraints

2019-05-08 13:07:02

本手册主要描述高云半导体时序约束的相关内容,包含时序约束编辑器(Timing Constraints Editor)的使用、约束语法规范以及静态时序分析报告(以下简称时序报告)说明。旨在帮助用户快速

2022-09-29 08:09:58

to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-13 13:33:25 13

13 to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-13 14:16:13 21

21 to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-15 13:50:49 8

8 timing and jitter measurements have become crucial

in the design, verification, characterization, and application of electron

2009-07-21 10:21:09 0

0 ISE时序约束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 Without Timing Constraints• This design had no timingconstraints or pin assignments– Note

2010-01-11 08:54:44 6

6 Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

2010-01-11 08:55:47 4

4 Achieving Timing Closure:Timing Reports• Timing reports enable you to determine how and why

2010-01-11 08:56:19 0

0 Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

2010-01-11 08:56:50 10

10 IntroductionUntil now, verifying that timing in 33 MHz 64-bit PCI designs met thesetup and hold

2010-07-13 09:39:34 4

4 Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs

Abstract

2009-04-07 23:43:36 666

666

microcontroller when used with external program memory. Due to the high speed of this device, critical memory interface timing constraints are examined.

2009-04-23 15:38:08 1087

1087

Timing Con

2009-04-24 09:12:31 740

740

The DS31415 is a flexible, high-performance timing IC for diverse frequency conversion

2011-08-01 16:27:04 25

25 本内容介绍了逻辑分析仪中Timing-State存储方式的应用

2011-09-22 14:26:50 14

14 ofPERIOD constraints and the specific paths that arecovered by PERIOD constraints. Additionally, examplesof timing reports are included with t

2012-02-17 14:41:54 0

0 TimeQuest_Timing_Analyzer快速入门教程

2015-12-14 14:21:13 22

22 TMS320FC240 DSP Controllers Peripheral Library and Specific Devices Reference

2016-01-19 14:25:12 10

10 Timing,PCB学习好资料,欢迎下载学习。

2016-03-23 10:06:24 0

0 通常情况下,HoldTiming是由工具自动去检查并满足的,人为可以干预的地方很少。如果你的设计在布局布线后,出现了hold timing违例的情况,那么你可以参考下本文提出的3点建议,看看能否改善

2017-02-08 05:22:12 4871

4871

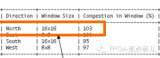

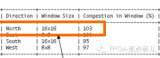

随着FPGA规模越来越大,设计本身的复杂度也同样增加。Xilinx UFDM中也经常提到了Design Complexity这样一个概念。Timing/Complexity/congestion

2017-02-08 05:46:09 3042

3042

Perfect Timing II Book

2017-10-27 09:23:52 6

6 ” • “Synthesis Constraints” • “Timing Constraints” • “Configuration Constraints”

2017-11-24 19:59:29 2671

2671

” • “Synthesis Constraints” • “Timing Constraints” • “Configuration Constraints”

2017-11-25 01:27:02 4716

4716

时序分析基本概念介绍——Timing Arc

2018-01-02 09:29:04 23487

23487

Timing.zip 5天前 上传 下载次数: 6 下载积分: 积分 -1 7.75 MB, 下载次数: 6, 下载积分: 积

2018-08-06 15:08:02 400

400 上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

然后会出现如下窗口, 使用GTD前, 需要有一个machine readable格式的timing report文件, 该文件可以通过report_timing -machine_readable

2020-05-19 16:14:47 7022

7022

AD9928:双通道、14位CCD信号处理器,内置垂直驱动器和Precision Timing发生器

2021-03-19 01:16:56 7

7 AD9923A: CCD 信号处理器,内置垂直驱动器和Precision Timing发生器 数据手册

2021-03-19 06:53:40 0

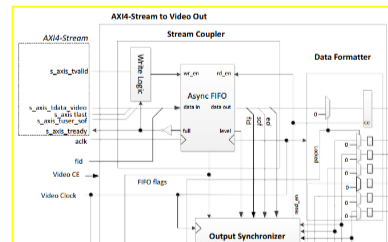

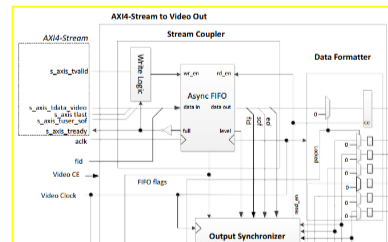

0 本文对Video out IP和Video Timing Controller IP进行简要介绍,为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2021-05-08 10:03:16 5452

5452

随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

2022-09-15 10:24:37 972

972 Timing Commander 硬件 Interfaces 用户指南

2023-03-15 19:24:19 1

1 9FGV1005 PhiClock PCIe Timing Commander 软件 用户指南

2023-03-21 19:28:49 2

2 9FGV1006 Timing Commander 用户指南

2023-03-21 19:29:17 1

1 9FGV100x Timing Commander 用户指南

2023-03-21 19:29:27 0

0 Timing Commander 软件 for VersaClock 3S - 5P3502x

2023-03-23 19:42:47 1

1 VersaClock 6 Timing Commander 用户指南

2023-03-29 19:02:31 1

1 默认report_timing中会出现换行的情况,如下图所示,如何避免换行呢?

2023-04-15 10:20:33 2089

2089 Timing Commander 软件 for Programmable Buffers

2023-05-15 19:16:04 0

0 有些情况下,constraint不能简单用一行来表达,而是需要复杂的计算,如果都写到constraint block内部就比较复杂,而且很乱,这时候可以调用functions来约束随机变量。在constraint内调用function就称为”function in constraints”。

2023-06-21 17:31:28 635

635 今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1397

1397

Timing Commander 硬件 Interfaces 用户指南

2023-07-06 18:35:05 0

0 9FGV1005 PhiClock PCIe Timing Commander 软件 用户指南

2023-07-07 19:27:28 0

0 9FGV1006 Timing Commander 用户指南

2023-07-07 19:28:06 0

0 9FGV100x Timing Commander 用户指南

2023-07-07 19:28:21 0

0 Timing Commander 软件 for VersaClock 3S - 5P3502x

2023-07-10 19:34:18 0

0 VersaClock 6 Timing Commander 用户指南

2023-07-11 19:27:17 1

1 Timing Commander 软件 for Programmable Buffers

2023-07-11 20:27:38 0

0 今天想来聊一聊timing model。Top层在做STA的时候,为了速度的考量,有的时候不会把所有block都做flatten(展平化)处理

2023-12-06 14:03:13 270

270

电子发烧友App

电子发烧友App

评论