AMBA AXI协议支持支持高性能、高频率系统设计。

适合高带宽低延时设计

无需复杂的桥就能实现高频操作

能满足大部分器件的接口要求

适合高初始延时的存储控制器

提供互联架构的灵活性与独立性

向下兼容已有的AHB和APB接口

2017-09-19 10:55:46 42415

42415

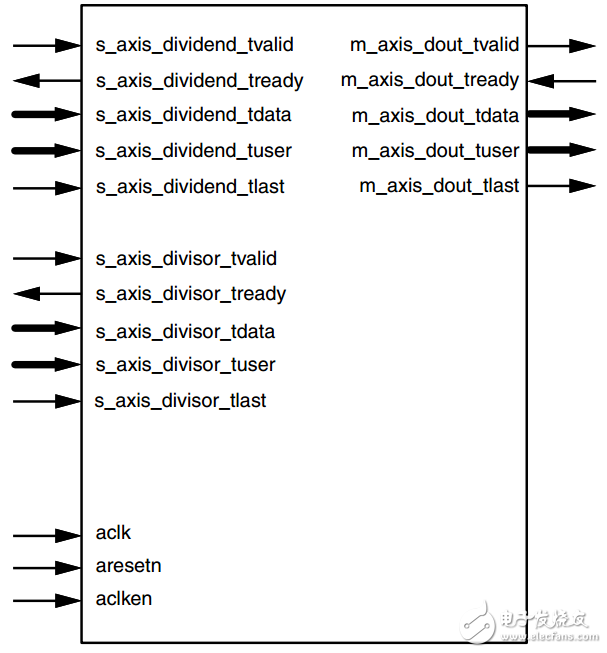

除法运算。很多人觉得不就是除法嘛,直接打上/即可,但是,FPGA是不能正确综合这个除法器的,综合的结果只是一个固定数值,而不像其他微处理器。可以这么说,用FPGA实现除法运算是比较麻烦的。

2020-06-17 10:17:27 6533

6533

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议

2020-12-23 15:32:37 2169

2169 FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门

2020-12-25 14:07:02 2957

2957

代替,比如可以先用除法运算获得整数部分,然后用求余运算获得余数,再对余数进行运算。2、本例实现一个除法运算,所得上的整数部分送P1口显示,小数部分送P0口显示。3、实现方法,本例计算101除以2的结果

2012-03-22 10:47:30

各位大侠, 谁有AXI总线的手册呀?如果有中文学习记录+手册就更完美了。谢谢先

2014-08-05 12:28:25

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且

2018-08-13 09:27:32

请问一下大家有没有用Xilinx的除法器IP核的,版本是V3.0的!我们在做有符号数除法的过程中运算结果经常出错!原先做的产品,Divider的工作频率是40M,后来工作频率变为62M时就经常出错

2015-03-06 19:42:16

,占用的资源就越多。虽然有IP可以直接调用,但我们还是要了解FPGA中除法的原理,手动来写一个除法器。FPGA中除法原理两个32的无符号整数除法,被除数a除以除数b,他们的商和余数都不会超过32位

2020-12-24 16:06:22

一文读懂DS18B20温度传感器及编程对于新手而言,DS18B20基本概念仅做了解,最重要的是利用单片机对DS18B20进行编程,读取温度信息,并把读取到的温度信息利用数码管,LCD1602或者上位

2021-07-06 07:10:47

一文读懂中断方式和轮询操作有什么区别吗?

2021-12-10 06:00:50

一文读懂什么是NEC协议?

2021-10-15 09:22:14

一文读懂传感器传感器在原理与结构上千差万别,如何根据具体的测量目的、测量对象以及测量环境合理地选用传感器,是在进行某个量的测量时首先要解决的问题。当传感器确定之后,与之相配套的测量方法和测量设备也就

2022-01-13 07:08:26

一文读懂如何去优化AC耦合电容?

2021-06-08 07:04:12

一文读懂接口模块的组合应用有哪些?

2021-05-17 07:15:49

产品设计的成败关键之一。本节,我们就将主要介绍PS和PL的连接,让用户了解PS和PL之间连接的威廉希尔官方网站

。 其实,在具体设计中我们往往不需要在连接这个地方做太多工作,我们加入IP核以后,系统会自动使用AXI接口

2021-01-07 17:11:26

AD539做除法运算电路,有谁做过,请大神指导,现在想做一个除法运算电路,电路搭出来有问题

2017-07-05 22:18:53

AMBA_AXI总线详解

2014-04-18 11:48:28

使用c6678进行浮点除法运算的时间测试的时候(使用clock),发现(使用c6678evm板)运行时间很长,运算时间达到七百多个时钟周期。请问是什么原因?c6678本身的浮点除法能达到什么样的运算速度呢?

2018-06-21 13:49:31

中,以便在 ARM 内核执行加载或存储时,它不使用 AXI64 总线?这段时间IP总线和AXI64总线会被DMA用来写OCRAM中的sample吗?是否有另一种内存配置可以帮助我们实现我们想要做的事情?有没有办法优先处理 DMA 传输?

2023-04-04 07:09:50

,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构。功能定义:在上一篇ZYNQ入门实例博文讲解

2020-04-23 11:16:13

VARON是一款AXI性能分析工具。VARON帮助对AXI总线进行性能分析,该总线用于FPGA/ASIC设计的各个阶段,如架构、RTL设计、原型滤波网络等。 VARON捕获AXI总线信号和可视化

2020-11-02 16:54:39

为什么MCU中的除法运算要比乘法运算的效率低

2023-10-09 07:45:11

标志实现不可恢复的加-减除法运算,运行的结果存在R3中。如果要做有符号除法,首先应执行DIVS一次,从而得到商的符号位。然后多次执行DIVQ得到商。【 指令周期 】 2 + RW (DIVS) / 3

2009-09-21 09:26:57

请问在开源的E203的AXI总线支持burst传输吗?在sirv_gnrl_icb2axi.v模块中看到了

请问如何使用呢?相应的在NucleiStudio中的代码中需要做什么修改呢?有大佬指点一下想要使用AXI做burst传输具体需要做那些步骤呢?

2023-08-12 06:13:08

国外的融合威廉希尔官方网站

专家展示了一项基于FPGA的数据采集系统,用于合成孔径成像威廉希尔官方网站

。采用了Xilinx ISE设计软件,支持ARM AMBA AXI4接口。文风犀利,观点新颖,FPGA中使用ARM及AMBA总线中不可多得的资料在赛灵思FPGA中使用ARM及AMBA总线[hide][/hide]

2012-03-01 15:48:17

运算(/和%)执行起来比较慢,所以应尽量避免使用。但是,除数是常数的除法运算和用同一个除数的重复除法,执行效率会比较高。在ARM中,可以利用单条MUL指令实现乘法操作。本文将阐述如何用乘法运算代替除法

2011-07-14 14:48:47

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

我有一个simpleregister读/写/重置测试接口代码(在VHDL中),我想与我的顶级处理系统7wrapper代码链接。我想使用AXI总线协议对寄存器进行读/写/复位。实际上,我的测试接口

2019-09-09 10:03:44

现在我要用block design搭建SOC,需要将总线转为AXI。按照论坛中的帖子,将e203_subsys_mems模块中的sirv_gnrl_icb2axi模块放到system层中,然后声明

2023-08-12 06:12:28

`1、在开发zynq工程时遇到多个axi_hp总线读写ddr时,总线锁死。现象就是axi_hp的wready信号一直为低。架构图: 2、应用write1、wrtie2、read1同时并行读写ddr3

2020-04-15 21:57:28

实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示实现两个二进制除法运算,并在八个七段数码管上进行显示

2013-11-01 20:34:01

zstar_zynq_ps_wrapper.v,可以看到有很多AXI_GP0打头的信号增加到了系统中,这些信号就是Zynq系统作为主机连接到PL的AXI GP总线接口。接下来我们要做的事就是设计一个

2019-11-12 10:23:42

axi_hp0_rd.v模块发起一次读DDR3的操作,i_data_*信号送到axi_hp0_wr.v模块发起一次DDR3写的操作。在ILA在线逻辑分析仪中,由于每秒都有AXI HP0总线的读操作和写操作,因此我们可以很

2019-11-26 09:47:20

问题想必是每一个初次使用AXI HP总线的开发者希望评估到的。那么,本实例就搭了一个很基本的架构出来,使用100MHz的AXI HP总线时钟频率(可更改),任意开关每个独立的AXI HP读或写通道,以评估

2019-11-28 10:11:38

eXtensibleInterface)协议是一种面向高性能、高带宽系统设计的总线协议,能够满足各种高速系统的总线互联。AXI协议的主要特点有:●独立的地址、控制和数据接口●支持使用字节选通的不对齐数据的传输

2019-05-06 16:55:32

,ar)共用一组信号的接口(arw,w,b,r)。关于总线互联的设计凡是设计中用到Axi4总线的设计总离不开总线互联。在Xilinx FPGA使用中,VIvado针对Axi4总线提供了丰富的IP,对于

2022-08-02 14:28:46

最近做的东西涉及到将原有的DSP+FPGA架构的程序移植到ZYNQ-7系列FPGA上,请问如何将原DSP程序移植到ZYNQ-7的ARM上,可不可以做一个EMIF总线和AXI总线转换的模块呢?

2014-05-12 21:51:09

小弟最近在用STM32F030C6T6芯片完成电机的SVPWM控制。现在发现算法中,运行速度很慢。打算将所有的除法运算改成移位运算。一般的,无符号数的右移几位和除以2的几次幂是等效的。但是,在STM32里面,有符号数的右移也和除法运算等效吗?

2019-01-22 08:14:26

microblaze通过串口读写FPGA内部axi4总线上的寄存器

2020-12-23 06:16:11

在FPGA中实现高精度快速除法

2010-07-17 16:33:18 25

25 高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37

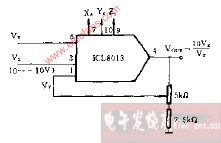

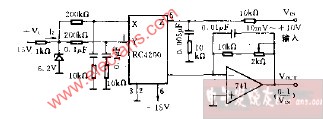

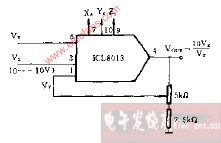

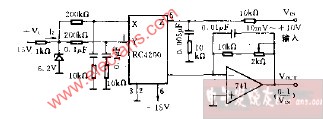

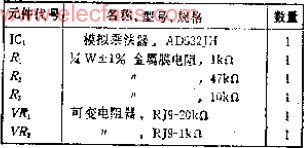

采用ICL8013的除法运算电路图

2009-07-17 11:23:30 874

874

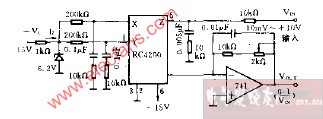

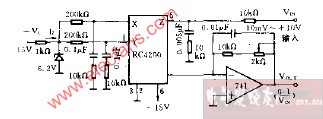

除法运算电路图

2009-07-17 11:26:48 4079

4079

采用ICL8013的除法运算电路图

2009-07-20 12:02:08 636

636

采用ICL8013的除法运算电路图

2009-07-20 12:02:30 700

700

除法运算电路图

2009-07-20 12:10:07 734

734

原码除法运算原理是什么? 两个原码表示的数相除时,商的符号由两数的符号按位相加求得,商的数值部分由两数的数值部分相除求得。 设有n位定

2010-04-13 11:15:45 11598

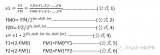

11598 除法器对数运算电路的应用

由对数电路实现除法运算的数学原理是:

2010-04-24 16:07:27 2520

2520

用于比率计算的除法运算电路

电路的功能

本电路是用X除输入信号Z

2010-05-08 15:29:01 1619

1619

FPGA实现铁轨检测算法设计_本文将阐述如何用乘法运算代替除法运算,以及如何使除法的次数最少化。

2011-10-05 16:37:19 10787

10787

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核实现基于AXI总线的双核嵌入式系统设计以及共享实现LED灯的时控.

2012-03-09 14:17:01 91

91 AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 详细介绍AXI总线

2017-02-28 21:03:54 1

1 14.2 除法运算 因为ARM体系结构本身并不包含除法运算硬件,所以在ARM上实现除法是十分耗时的。ARM指令集中没有直接提供除法汇编指令,当代码中出现除法运算时,ARM编译器会调用C库函数(有符合

2017-10-17 17:22:29 5

5 AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司

2017-11-17 08:58:01 4189

4189 1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 9601

9601

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 3953

3953

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2021-02-04 06:00:15 10

10 在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2021-02-23 06:57:00 45

45 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 、数据和控制信号转换为AXI总线协议中的相应信号,从而实现两种总线协议之间的通信。从模块级和FPGA系统级两个方面对PLB2AⅪI总线桥的功能进行验证,结果表明,该方案设让的总线桥能够正确转换协议,且耗时仅为传统总线桥的54.41%,具有更高的转换传输效率

2021-03-30 15:21:33 8

8 AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 4970

4970

本文介绍了AMBA 3.0 AXI的结构和特点,分析了新的AMBA 3.0 AXI协议相对于AMBA 2. 0的优点。它将革新未来高性能SOC总线互连威廉希尔官方网站

,其特点使它更加适合未来的高性能、低延迟

2021-04-12 15:47:39 28

28 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 AXI——Advanced eXtensible Interface,直译过来就是先进的可扩展接口,是由ARM公司提出的,是一种高性能、高带宽、低延迟的片内总线。FPGA工程师会发现其大量运用于FPGA设计中,Vivado中的接口类IP全部都配有AXI接口,可见其重要性。

2022-03-14 14:13:01 4700

4700 FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。

2022-04-27 09:16:03 6098

6098 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能、高主频的系统设计的。AXI协议是被优化

2022-10-10 09:22:22 8632

8632 NI Multisim 10经典教程分享--除法与开平方运算电路

2023-02-08 09:18:28 1113

1113 本文是本系列的第四篇,本文主要介绍FPGA常用运算模块-除法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:20:45 1840

1840

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

2023-05-24 15:06:41 669

669

在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

2023-05-25 11:22:54 570

570

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想打打拍改善下时序都不知从何下手。

2023-07-04 10:03:39 599

599

FPGA实现加法和减法运算非常简单,实现乘法和除法可以用IP,那实现对数和指数运算该用什么呢?

2023-08-05 09:37:05 810

810

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2357

2357

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1896

1896

LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484 LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

在介绍AXI之前,先简单说一下总线、 接口 以及协议的含义 总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般

2023-12-16 15:55:01 248

248

电子发烧友App

电子发烧友App

评论