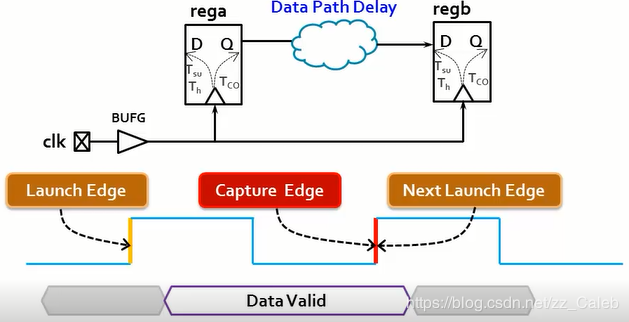

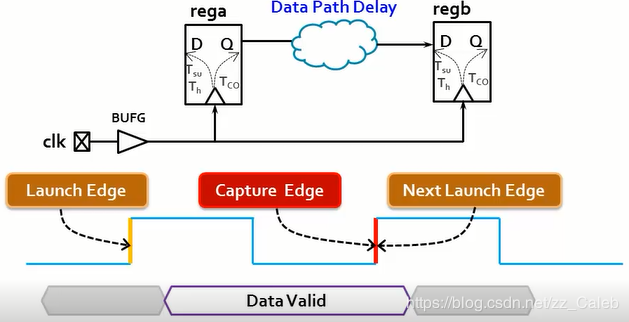

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2768

2768

。静态时序分析工具很好地解决了这两个问题。它不需要激励向量,可以报出芯片中所有的时序违例,并且速度很快。 通过静态时序分析,可以检查设计中的关键路径分布;检查电路中的路径延时是否会导致setup违例;检查电路中是否由

2020-11-25 11:03:09 8918

8918

边沿。 ④ 通常情况下这两个边沿会有一个时钟周期的差别。 2、时序路径 (Timing path典型时序路径有四种) ① ② 第一类时序路径(红色) - 从device A的时钟到FPGA的第一

2020-11-25 15:27:21 8566

8566

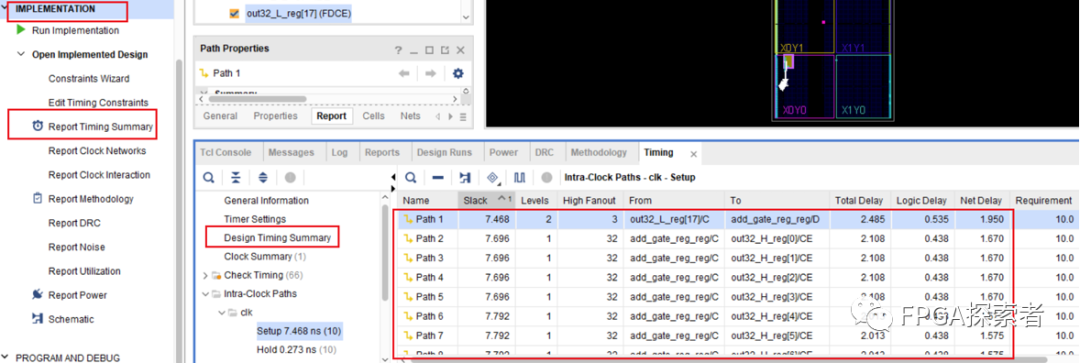

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1284

1284 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的路径。

2023-06-26 14:28:01 604

604

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

可能无法满足时序要求。 跨时钟域信号的约束写法 问题一: 没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将这三类约束

2023-08-01 09:18:34 1041

1041

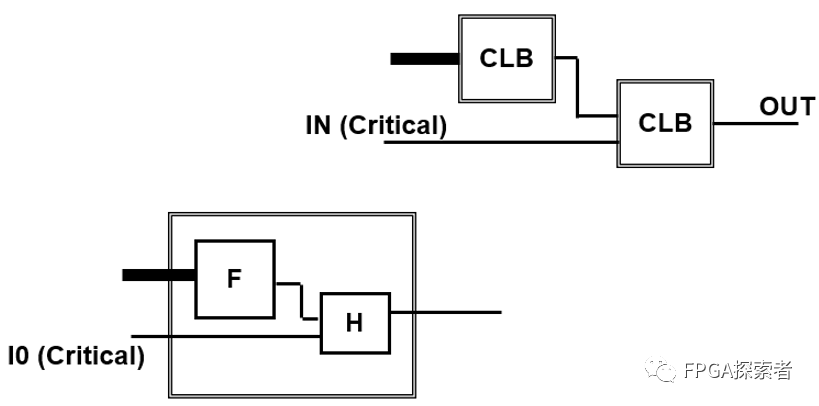

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

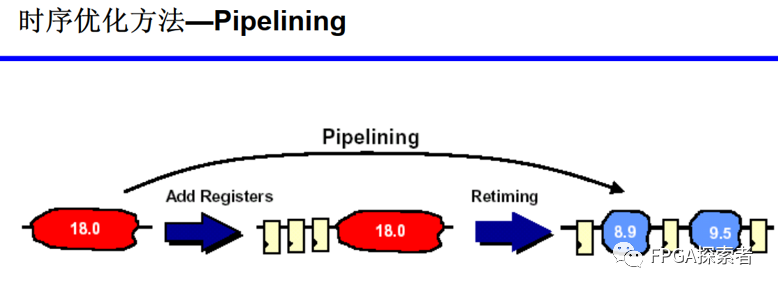

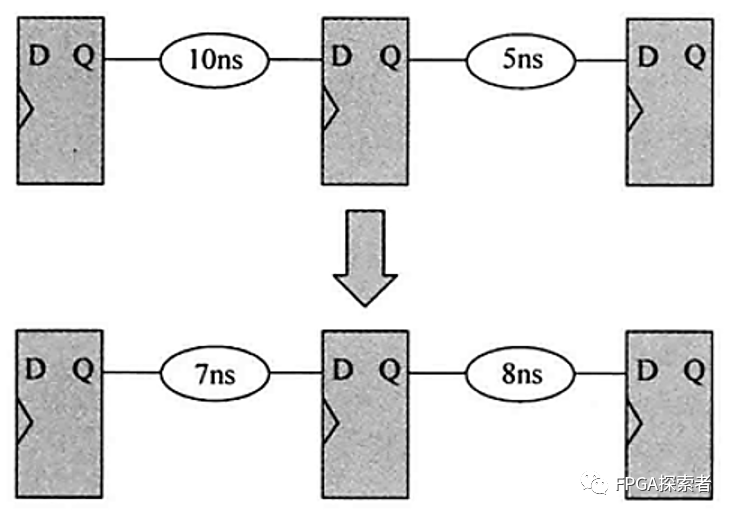

FPGA系统设计实质上是一个同步时序系统的设计,理解时序概念,掌握代码优化与综合威廉希尔官方网站

,正确完整地进行时序约束和分析是实现高性能系统的重要保证。很多同学在设计中都会碰到时序方面的问题,如何解决时序难题

2018-06-07 15:52:07

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

和时钟偏差组成的。

二、时序路径

时序路径是指从FPGA输入到输出的所有逻辑路径组成的路径。当存在时序路径时,需要考虑时序约束以确保正确的逻辑功能和时序性能。

时序路径中的关键元素包括:

(1) 路径

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

由于缺乏布局优先级信息而盲目优化非关键路径。由于模块在每一次编译中的布局位置变化被限定在了最优的固定范围内,时序收敛结果的可重现性也就更高。由于其粗粒度特性,LogicLock的约束信息并不很多,可以

2017-12-27 09:15:17

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

减少关键路径的逻辑等级本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面要列举的代码示例是一些能够起到

2015-07-02 22:17:18

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

的路径延时如下:din1 = 7ns, din2 = 4ns, din3 = 18ns, din4 = 13ns。显然,FPGA内部的时序全部都能够满足要求。(特权同学,版权所有)图8.6 时序分析实例2

2015-07-14 11:06:10

,他们共用一个时钟(当然也有不共用一个时钟的reg2reg路径,这种路径的分析会复杂一些,这里不做深入讨论)。对于reg2reg路径,我们只要告诉FPGA的时序设计工具他们的时钟频率(或时钟周期),那么

2015-07-20 14:52:19

reg2reg路径的时序分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 我们可以先重点研究一下

2015-07-24 12:03:37

接口时序的分析来分析reg2pin路径。(特权同学,版权所有)我们可以先回顾一下第三章中给出的VGA驱动实例的硬件接口框图。如图8.22所示,在这个框图中,我们主要分析FPGA器件和ADV7123芯片

2015-07-26 21:56:45

VGA驱动接口时序设计之3时钟约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 如图8.26所示

2015-07-30 22:07:42

VGA驱动接口时序设计之4建立和保持时间分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt下面我们可以简单

2015-08-02 19:26:19

VGA驱动接口时序设计之6建立和保持时间约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 接着,我们可以

2015-08-06 21:49:33

VGA驱动接口时序设计之7优化本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt最后,再次编译系统,查看时序

2015-08-10 15:03:08

的时序路径分析。(特权同学,版权所有)CMOS Sensor接口相对于FPGA来说是不折不扣的pin2reg所覆盖的约束类型。在开始这个CMOS Sensor的时序约束前,我们先来进一步认识一下

2015-08-12 12:42:14

Sensor和FPGA接口的寄存器路径模型。在这个路径分析中,我们不去考虑CMOS Sensor内部的时序关系,我们只关心它的输出引脚上的信号。先看时钟PCLK的路径延时,在PCB上的走线延时为Tcpcb,在

2015-08-14 11:24:01

专门找一条路径出来,看看它的具体时序路径的分析。如图8.59所示,vd[0]这条数据线的建立时间报告中,66ns的input max delay出现在了Data Arrival Path中。(特权同学

2015-08-19 21:58:55

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

。 在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新

2017-09-01 10:28:10

FPGA设计技巧_关键路径FPGA软件无线电开发(全阶视频教程+开发板+实例)详情链接:http://url.elecfans.com/u/5e4a12f2ba

2014-04-22 13:11:41

FPGA设计验证关键要点不同于ASIC设计,FPGA设计中的标准元件或客制化实作,一般欠缺大量的资源及准备措施可用于设计验证。由于可以重新程式化元件,更多时候验证只是事后的想法。本文将探讨在FPGA

2010-05-21 20:32:24

FPGA静态时序分析——IO口时序(Input Delay /output Delay)1.1概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能

2012-04-25 15:42:03

fpga关键路径 一份很好的资料

2013-07-12 17:33:36

如题:fpga时序分析一般都做哪些分析我自己研究时序分析也有一段时间了 ,从理论到altera的timequest,差不多都了解了 ,但就是不知道一个具体的项目都要做哪些约束。求大神知道,或者有没有这方面的资料(网上资料基本都看过了,没有说明具体项目的)。

2012-10-22 22:20:32

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

各位大侠,能否分享一下找到影响时序的关键路径的一些经验

2014-02-27 11:17:52

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

2015-01-04 15:17:16

和关键路径调整为了获得更好的时序,我们建议使用特定的代码风格来描述有限状态机、RAM、数学/DSP功能、时钟树和移位寄存器。结果会提高时序QoR,因为综合工具能够推断一个实现使用了FPGA原语的构件

2019-08-11 08:30:00

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。会有来自不同角度的挑战,包括:?更好

2021-05-18 15:55:00

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合

2018-04-03 11:19:08

FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner可以提取相关信息和利用图表更新。在这

2009-04-14 17:03:52

特权同学FPGA公开课第四讲--时序分析之pin2reg-PPT下载

2013-07-26 19:30:47

design内部,都是同步时序电路,各处的延时等都能够估计出来,但是FPGA内部并不知道外部的设备的时序关系。所以,TIming constraints包括输入路径(Input paths )寄存器

2019-07-09 09:14:48

给我们的FPGA做内部时钟,在输出到外部做SDRAM的工作时钟,所以上图中,晶振到外部器件的时钟路径,应该是PLL的输出到SDRAM的输出路径还有,我们之前做的静态时序分析,是基于在FPGA内部的,所以数据

2015-03-31 10:20:00

静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 基于时序路径的FPGA时序分析威廉希尔官方网站

研究_周珊

2017-01-03 17:41:58 2

2 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2417

2417

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4150

4150

静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

2019-09-01 10:45:27 2942

2942

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37:00 2460

2460

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中

2021-01-11 17:44:43 8

8 任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

2021-01-12 17:48:08 19

19 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 电子发烧友网为你提供时序分析是FPGA如何设计?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-15 08:51:20 12

12 方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

什么是关键路径? 关键路径分为两类:一类是时序违例的路径,主要是建立时间违例; 另一类是时序没有违例,但逻辑级数较高的路径。当然,第一类路径中可能会包含第二类路径。 对于第一类路径,其违例的原因

2021-07-06 17:22:48 5126

5126 Paper”的殊荣。 此外,在今天下午举行的各个威廉希尔官方网站

分论坛上,燧原科技分别在“数字设计与Signoff”和“PCB、封装和系统分析”会议上发表了演讲。 Tempus-PI 仿真和实测关键时序路径的一致性

2021-10-19 14:17:23 1387

1387 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

2022-05-04 17:13:00 1827

1827 要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。

2022-08-02 08:57:26 517

517 在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25:06 425

425

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45:13 1809

1809 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30:43 247

247

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

2023-08-08 10:31:44 525

525

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型的特征:数据多个周期翻转一次,如下图所示。因此,我们把这种路径称为多周期路径(FPGA设计中更多的是单周期路径,每个周期数据均翻转)。

2023-09-14 09:05:02 466

466

电子发烧友App

电子发烧友App

评论