在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;

2023-02-20 10:18:27 3783

3783

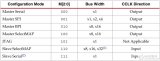

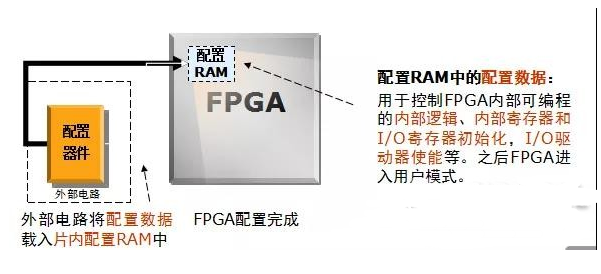

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA、然后是测试FPGA,配置FPGA是指将FPGA通过将配

2011-10-12 15:16:25 1414

1414

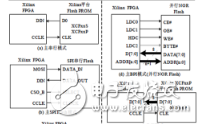

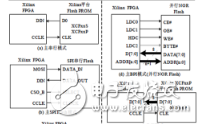

随着FPGA 成为系统级解决方案的核心,大型、复杂设备常需要多片大规模的 FPGA。如果使用 PROM 进行配置,需要很大的 PCB 面积和高昂的成本.

2015-02-04 11:42:27 7817

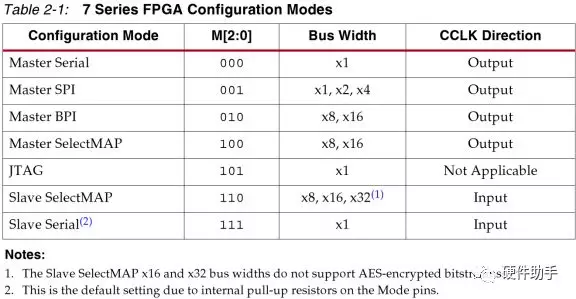

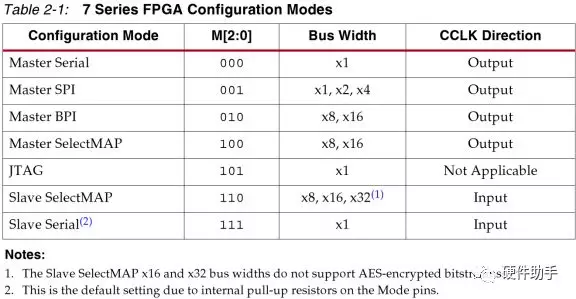

7817 本文主要介绍Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21577

21577

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2022-09-22 09:13:59 3375

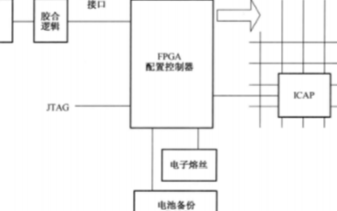

3375 我们所说的FPGA配置电路,一方面要完成从PC上把bit文件下载到FPGA或存储器的任务,另一方面则要完成FPGA上电启动时加载配置数据的任务。

2023-06-10 10:09:52 317

317

32 FPGA 配置电路主模式 从模式 JTAG模式

2019-07-04 11:37:31

FPGA配置模式

2012-08-17 22:24:05

,但是FPGA并没有相应的反应,就是FPGA并没有工作。又尝试了一下AS模式配置FPGA,同样,配置文件也可以烧写进去,FPGA同样不工作。而且重新上电之后FPGA也同样不能正常工作,只有当烧写器连在

2014-08-21 15:44:32

直接把所有电路做在一个工程中,这样使用的FPGA芯片容量太庞大,非常昂贵,而且电路胶合控制太复杂,这时候我们可以对每种FPGA模型进行分别生成配置文件,当根据实时状态现场更新FPGA电路。这样就可以采用

2012-04-26 14:27:03

使用的是SPARTAN-3E的开发板,在fpga配置文件时,.bit文件的下载时,程序可以在线正常运行。但使用.mcs文件配置时,ISE上显示program success,但板子上的FPGA并没有

2015-03-16 17:05:25

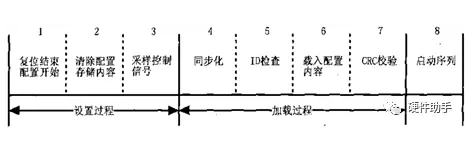

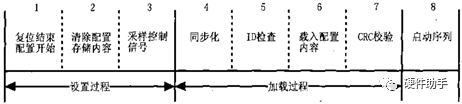

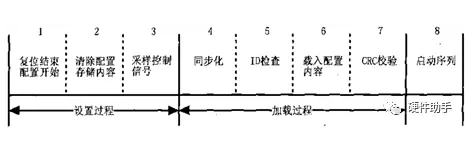

发出低脉冲 后,FPGA芯片经过一个初始化序列清空内部FPGA配置存储器。此序列开始时,DONE和INIT_B引脚均转为低。初始化完成后,INIT_B引脚转 为高,并采样芯片的配置模式及变量选择引脚

2012-08-12 11:56:42

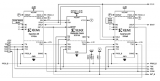

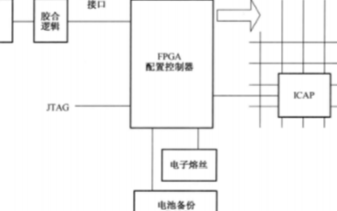

模块会配合写命令和对应的操作地址,将缓冲区中一帧配置码流分多次送往Flash控制器。2.2 FPGA器件配置模块设计Virtex系列FPGA器件的配置模式共有4种:串行主模式、串行从模式、并行从模式

2019-06-10 05:00:08

XST的11个技巧 515.4 大规模设计带来的综合和布线问题 525.5 FPGA相关电路设计知识 545.5.1 配置电路 545.5.2 主串模式——最常用的FPGA配置模式 565.5.3 SPI

2009-04-09 18:28:46

的设置以及时序分析455.3.4综合高手揭秘XST的11个技巧515.4 大规模设计带来的综合和布线问题525.5 FPGA相关电路设计知识545.5.1 配置电路545.5.2 主串模式——最常

2012-02-27 15:44:02

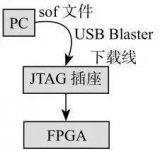

使用Flash+CPLD的方式去配置FPGA。在把程序固化到配置芯片之前,一般先使用JTAG模式去调试程序,也就是把程序下载到FPGA芯片上运行。虽然这种方式在断电以后程序会丢失,但是充分利用了FPGA

2019-06-11 05:00:07

进行编程。用户可以根据不同的配置模式,采用不同的编程方式。FPGA 的使用非常灵活。目前,大部分的 FPGA 在使用时都需要外接一个 EPROM 保存其程序,加电时,FPGA 芯片将 EPROM 中

2018-09-06 09:11:58

的可靠性,最好的方法是对电路进行筛选,其中老化试验就是筛选过程中最为重要的环节之一。 考虑到FPGA 电路的工作模式比较复杂,外部需要存储器或者FLASH 对其进行配置,FPGA 才能动态工作,因此

2011-09-13 09:22:08

FPGA的AS编程模式下的配置文件的大小与所写的程序有关吗?配置文件的大小怎么看啊?

2012-03-31 11:03:06

,以便在上电后立即启动配置过程。又或者,SPI存储器可在x1模式下退出通电状态,从而允许主机系统(FPGA)查询存储器中的串行闪存可发现参数(SFDP)表中的特性。这一x1模式已成为多家存储器厂商支持

2021-09-03 07:00:00

请教大家一个问题,板子上有两个FPGA,想用一个PROM配置,将PROM和两个FPGA用边界扫描下载方式连起来可以吗? 就是下图这种模式,可不可以再多串一个FPGA呢?

2014-03-24 15:53:09

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

开始之前,请阅读 UG290,Gowin FPGA 产品编程配置手册 SSPI 部分。SSPI(Slave SPI)配置模式,即 FPGA 作为从器件,由外部 Host 通过SPI 接口对 Gowin FPGA 产品进行配置。

2022-09-30 06:07:09

Cortex-M3硬核处理器2. FPGA 配置模式 JTAG 3. 时钟资源27MHz时钟晶振4. 按键2 个按键开关5. LED 1 个电源指示灯(绿)2 个 用户指示灯(绿)6. 存储

2021-04-08 16:00:30

我想要对FPGA实现脱离仿真器在线升级的功能,要能防掉电,不知道大家有做过的没? 我现在的想法是通过外部cpu来对FPGA进行配置和升级,FPGA采用从模式,比如用一个DSP来配置FPGA,上电

2017-01-17 20:00:09

FPGA是xc2v3000,PROM用的是xcf16p。配置文件是mcs格式的,用jtag模式烧写进入prom的。我在完成主串模式成功配置的基础上,将两者d1-d7数据接口分别相连,同时也将FPGA

2017-06-14 08:26:54

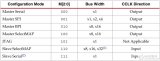

模式。XCF08P版本包括32兆位,16 - Mbit的,和8兆位串行PROM,支持主,从串行SelectMAP和SelectMAP FPGA配置模式。

2010-04-07 13:37:44

20,736(54,720) LUT4 资源 多种模式、容量丰富的 B-SRAM2. FPGA 配置模式 JTAG、MSPI3. 时钟资源 50MHz 时钟晶振 27MHz 时钟晶振4. 10

2022-06-05 16:14:08

亲爱的先生,我们使用了2个Vertex 5& spartan 6 FPGA,用于使用菊花链配置模式对这些FPGA进行编程。1.我们正在使用xilinx Blaster“平台电缆USB

2019-11-07 08:25:38

。AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列:如EPCS1,EPCS4配置器件专供AS模式,目前只支持 Cyclone系列。使用Altera串行配置器件来完成

2023-04-24 15:34:27

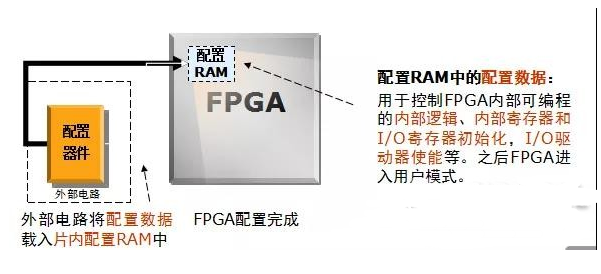

系统集成度、可靠性的最佳选择之一。 FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。 加电时,FPGA芯片

2014-12-04 15:43:38

实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中FPGA配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。JTAG模式

2016-08-10 17:03:57

我用的是Spartan-3E系列的芯片。我想有两种下载方式,方式一是通过JTAG直接给FPGA下载程序,方便调试。方式二是将程序烧到PROM里面,在上电时FPGA自动从PROM进行配置。现在的问题是

2013-10-18 10:06:47

/s/1i5LMUUD AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1、EPCS4配置器件专供AS模式。使用Altera串行配置器件来完成

2018-03-05 16:30:35

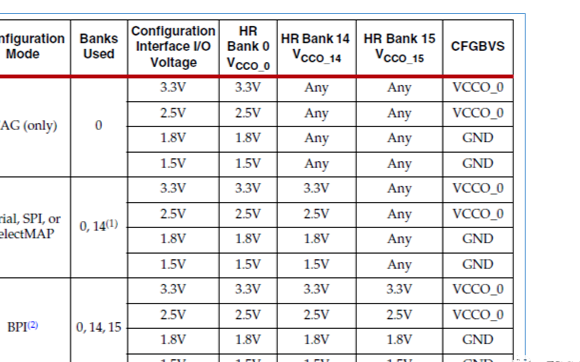

我使用外部配置emcclk时钟和闪存PC28F00AP30EFA在BPI-Fast模式下配置了Kintex7 FPGA。我遵循Xilinx AR#44636并定义了Config_Voltage

2020-06-04 12:45:32

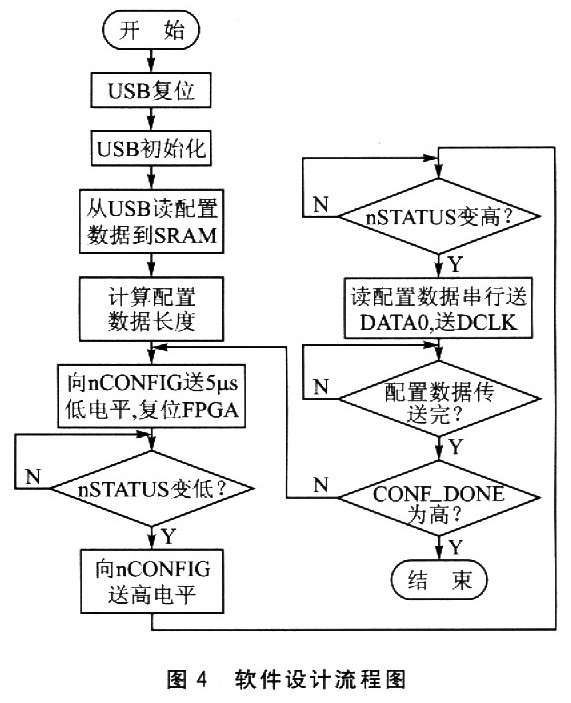

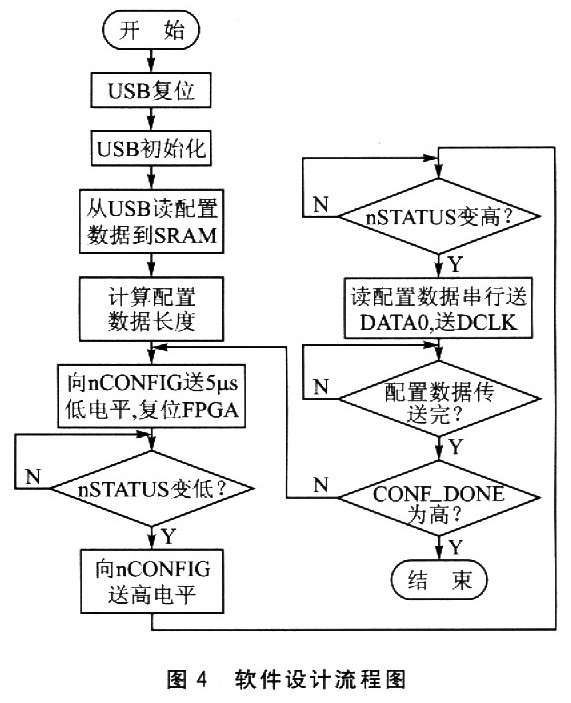

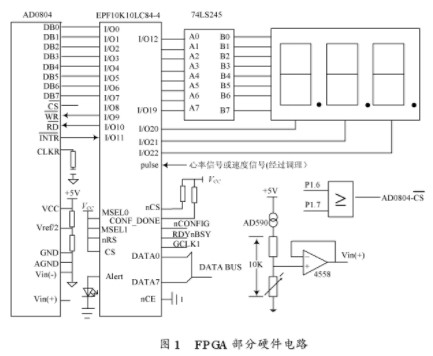

管脚模拟FPGA 的某种配置模式的时序,将配置文件写入到FPGA 的配置 RAM 中。Virtex 系列FPGA 有几种不同的配置模式,每种配置模式使用到的管脚以及配置 信号的时序都是不同的, 因此

2015-03-05 15:31:07

P89C61X2的功能特点是什么?如何用单片机通过PS模式配置FPGA?

2021-05-07 06:15:41

你好我想用FPGA(lx50t)通过JTAG模式配置另一个FPGA。有什么建议吗?或者一些参考?非常期待您的回复!

2020-06-11 10:00:20

关于FX3配置FPGA的8868问题1)在AN848 68中,如果FPGA已经由FX3配置,它将切换到从FIFO模式。这是否意味着原来的代码只能配置FPGA一次?是否有可能拆分通道,一个通道只用

2018-09-03 15:53:24

455.3.4 综合高手揭秘XST的11个技巧 515.4 大规模设计带来的综合和布线问题 525.5 FPGA相关电路设计知识 545.5.1 配置电路 545.5.2 主串模式——最常用的FPGA

2014-11-21 15:08:56

你好,我想使用两个PROM(XCF32P)来配置我的XC4VLX200。我知道我可以使用M [2:0]引脚确定FPGA配置模式。但我不知道PROM如何从FPGA获得当前的配置模式。你能告诉我哪些引脚用于通知PROM当前的配置模式吗?谢谢。

2020-05-27 10:13:34

不管Xilinx还是Altera,FPGA的配置模式或者方法多样,尤其是Altera器件,什么AS模式、PS模式、FPP模式、AP模式等等。一般逻辑设计者可能不会关心到硬件的设计,但是FPGA的硬件

2015-01-28 10:27:03

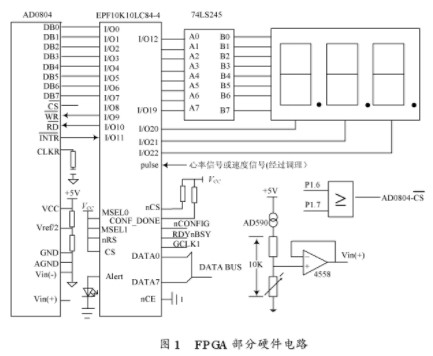

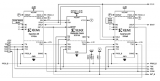

介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx 的Virtex-II 系列)的配置;给出进行FPGA 配置所需的详细时序图和原理图。本配置基本原理对其它FPGA 的配置也适用。

2009-04-16 14:11:36 18

18 基于单片机的CPLD/FPGA被动串行下载配置的实现:介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行模式的下载配置,阐述了其原理及软硬件设计。 &nb

2009-10-29 21:57:22 19

19 摘要:本应用指南提供了一种方法可从3.3V接口对Spartan™-3和Spartan-3L FPGA进行配置。它针对每种配置模式都提供了一组经验证的连接框图。这些框图是完整且可直接使用的解决方案

2010-10-24 23:02:08 68

68 什么是FPGA?FPGA是什么意思,本内容详加描述了FPGA的相关知识包括FPGA配置模式,PPGA特点及应用

2011-12-07 13:39:00 79099

79099 摘要:介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx的Virtex-II系列)的配置;给出进行FPGA配置所需的详细时序图和原理图。本配置基本原理对其它FPGA的配置也适用。

2009-06-20 11:02:38 942

942

FPGA 重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括

2009-09-03 11:17:08 528

528

基于U盘和单片机的FPGA配置

引 言FPGA广泛应用在电子通信领域,其安全性引起了注意,本文针对安全配置提出了解决方案。

现场可编程门阵列FPGA(F

2010-01-14 09:27:24 1175

1175

FPGA重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA

2010-01-26 09:39:56 544

544

本文首先介绍了如何用A rca G T 2000 实现对C yclone 系列FPG A 的PS 配置模式,然后对PS 模式的配置文件进行了说明。本实例已在具体工程项目中得以实际应用。

2011-06-27 15:46:29 36

36 FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理

2011-09-08 17:50:27 1734

1734 基于SD卡的FPGA配置,本文给出了对Virtex FPGA 进行配置的情 况,该方案也可以适用于Spartan 系列FPGA。

2011-12-13 10:02:42 6095

6095

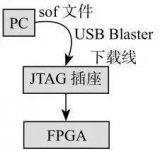

FPGA 有两种运行模式,即下载模式和烧写模式。下载模式是在上电的情况下通过 JTAG 接口直接把程序( Altera 平台下是.sof文件,SRAM Object File)下载到FPGA中。因为FPGA是基于SRAM结构的,因

2012-05-12 13:17:29 2341

2341 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2013-03-14 15:18:22 64

64 Spartan6系列FPGA通过把应用程序数据导入芯片内部存储器完成芯片的配置。Spart-6 FPGA可以自己从外部非易失性存储器导入编程数据,或者通过外界的微处理器、DSP等对其进行编程。对以上

2018-07-14 06:58:00 16361

16361

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程

2017-02-11 16:36:09 1446

1446

常用的有如下三种 配置文件:

Sof: SRAM Object File ; JTAG模式下,直接下载到FPGA中,

jic: JTAG Indirect Configuration

2017-09-19 16:49:06 12

12 ,即Slave SelectMAP模式,该模式下总线宽度分8,16,32bit三种,本文按照32bit模式配置和回读。配置的过程就是将mcs文件中的配置字序列通过SelectMAP接口写入FPGA。

2017-11-17 10:16:01 8730

8730 FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失(断电不丢数据)性存储器中的配置比特流,配置所需的时钟信号(称为

2017-11-22 09:24:02 6452

6452 从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA、然后是测试FPGA,配置FPGA是指将FPGA通过

2017-11-24 20:55:53 5922

5922

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2017-11-26 08:12:51 7889

7889

在FPGA中实现在应用编程(In Application Programming,IAP)有两种方法:一种是,在电路板上加外电路。例如用MCU或CPLD来接收配置数据,在被动串行(PS)模式

2017-12-13 13:58:10 24009

24009

Spartan6系列FPGA常见的配置模式有5种,该5种模式可分为3大类,1. JTAG模式(可归为从模式);2. 主模式;3. 从模式。主模式又划分为master serial模式、master parallel模式,从模式分为slave serial模式、slave parallel模式两种。

2018-03-21 11:43:00 4853

4853 本文档内容介绍了基于Spartan-6-FPGA配置讲解,供参考

2018-03-26 15:18:17 6

6 本演示介绍了 Spartan®-3A 入门套件如何让您立即获得 Spartan-3A FPGA 器件的节能模式,高速 I/O 选项,DDR2 SDRAM 存储器接口,商用闪存配置支持,以及利用 Device DNA 实现的 FPGA/IP 保护等特性。

2018-05-22 13:45:01 2484

2484 尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2018-08-01 15:32:54 4736

4736

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 17251

17251 ,FLEX10K可以使用4种配置模式,即:主动串行(AS)、被动串行(PS)、被动并行同步(PPS)、被动并行异步(PPA)。由于PPA配置模式为并行配置,其配置速度快,且配置时钟由FPGA内部产生,更有利于在线实现,本文就是采用PPA方式来实现电路系统的在线重构。PPA方式配置时应注意以下几点:

2019-08-21 08:01:00 4908

4908

单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 7298

7298 Altera FPGA支持AS,PS,JTAG等几种较常见的配置方法。 当为AS配置模式时,FPGA为主设备,加载外部FLASH中的数据至内部RAM中运行。当为PS配置模式时,FPGA为从设备,外部

2018-11-18 18:05:01 481

481 本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 17

17 今天咱们聊聊xilinx7系列FPGA配置的相关内容。总所周知FPGA上电后,其工作的逻辑代码需要从外部写入FPGA,FPGA掉电后其逻辑代码就丢失,因此FPGA可以被无限次的配置不同的逻辑代码

2019-10-20 09:02:00 2769

2769

Spartan-6 FPGA 利用CCL 支持布线线路与逻辑单元之间的可配置互联功能。Spartan-6 FPGA 是易失性器件- 电源移除时,不能保留原有配置。为了配置Spartan-6

2020-01-10 15:28:51 25

25 常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

2020-04-06 10:33:00 3828

3828

FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列

2020-07-09 10:53:09 7500

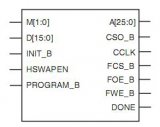

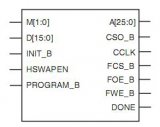

7500 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 我们知道,FPGA是易失性的。硬件配置,即把HDL代码下载到FPGA芯片中,才能进行下一步的调试。

2021-01-05 16:21:00 23

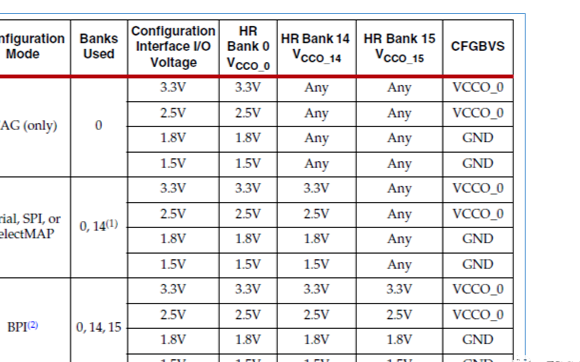

23 一、FPGA配置引脚说明 1、CFGBVS 如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。 如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND。 建议bank0

2021-01-18 13:43:10 10008

10008

方式 1、主动配置方式(AS) 2、被动配置方式(PS) 3、JTAG方式 1、AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由

2021-03-12 16:26:58 11308

11308

FPGA 主动方式:由 FPGA来主动输出控制和同步信号给 FPGA的串行配置芯片(EPCS系列) ,配置芯片收到命令后,把配置数据发给 FPGA,完成配 置过程;在 AS模式下,FPGA必须

2021-04-06 15:33:02 8

8 1. Master Modes 自动下载FPGA程序在本地的非易失性存储器,而且主模式的时钟来自内部晶振。 2. Slave Modes 外部控制下载FPGA配置模式,通常称为从模式,有串行

2021-05-11 15:22:40 3967

3967

所有现代FPGA的配置分为两类:基于SRAM的和基于非易失性的。其中,前者使用外部存储器来配置FPGA内的SRAM后者只配置一次。 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置

2021-07-02 16:01:40 2781

2781

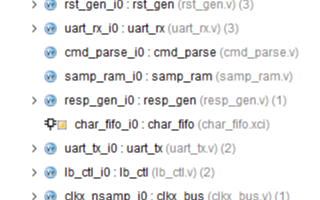

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

2021-07-05 15:28:24 3140

3140

广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器件进行编程

2021-09-06 09:41:56 6052

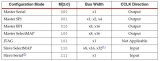

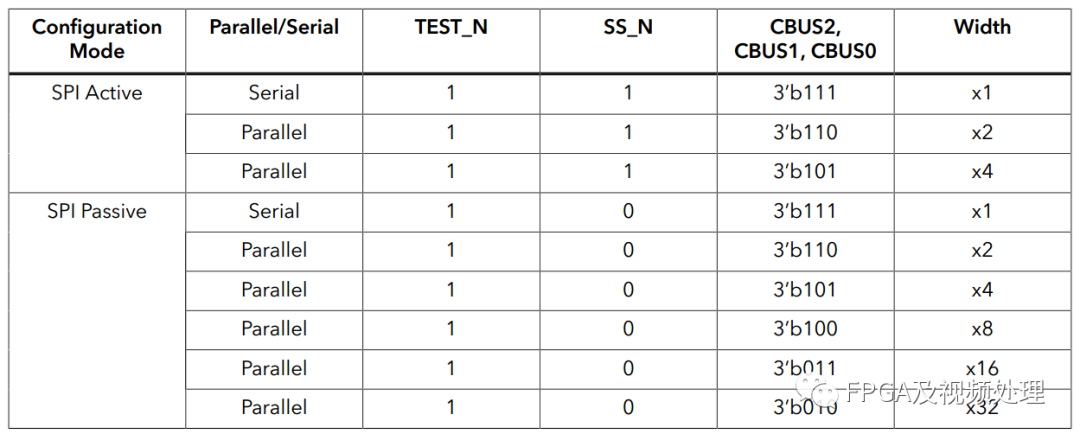

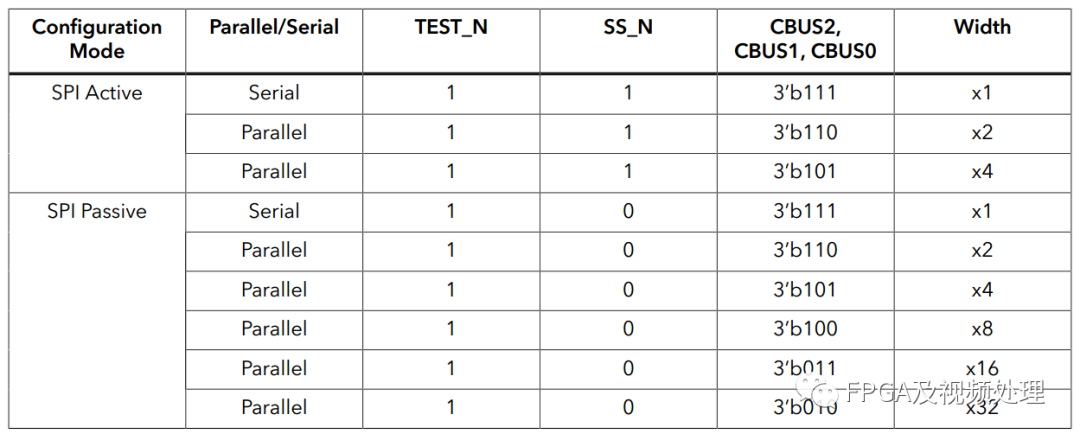

6052 易灵思Trion FPGA的配置模块主要由CBUS[2:0]、SS_N和TEST_N几个信号控制。FPGA进入用户模式前不要对这几个信号进行翻转。

2022-03-09 15:58:06 1497

1497

典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2022-03-14 14:02:50 1366

1366 中的数据送入FPGA器件内,配置完成之后将对器件I/O和 寄存器 进行初始化。初始化完成后,进入用户模式,开始正常工作。 一旦设计者选定了FPGA系统的配置方式,需要将器件上的MSEL引脚设定为固定值,以指示当前所采用的配置方式。 常用的配置方式有: PS配

2022-11-17 12:15:10 1141

1141 数据模式。 FPGA配置方式 根据FPGA配置过程控制者的不同,我们将配置方式主要分为三类: FPGA控制配置过程 第一种最常见的模式是,从片外FLASH中加载配置所需的比特流,FPGA内部产生时钟,整个过程有FPGA自主控制。FPGA 上电以后,将配置数据从FLASH中,读入到

2022-11-21 21:45:10 955

955 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置威廉希尔官方网站

,其主要优点是系统设计更加简单、不需要外部存储器和配置控制器、功耗低、成本低和FPGA配置时间更快。最大的缺点在于配置是固定的。

2022-12-01 11:08:45 862

862 ForgeFPGA 配置指南

2023-01-09 19:16:34 0

0 典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2023-02-15 09:57:24 618

618 总结Xilinx FPGA 的上电模式可以分为以下4类型: 主模式 从模式 JTAG模式(调试模式) 系统模式(多片配置模式) 1、主模式 典型的主模式都是加载片外非易失( 断电不丢数据

2023-03-29 14:50:06 535

535 ForgeFPGA 配置指南

2023-06-30 19:10:57 0

0

电子发烧友App

电子发烧友App

评论