本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 15422

15422

信号在FPGA器件中通过逻辑单元连线时,一定存在延时。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作电压、温度等有关。

2020-03-29 10:27:00 3276

3276 前边写了很多关于板上外围器件的评测文章,这篇是FPGA纯逻辑设计,是FPGA的另一部分——算法实现,上篇文章做了HDC1000传感器的使用,当时说FPGA是不支持小数的,本篇记述的是FPGA如何去做

2020-06-17 10:17:27 6533

6533

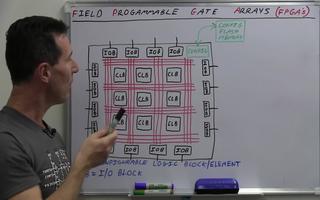

输入输出端口 从Implemented Design中可以看到FPGA中资源大致分布如下。中间蓝色是CLB可编程逻辑块、DSP或BRAM,两侧的彩色矩形块是I/O接口和收发器,划分的方块是不同的时钟域 Configurable Logic Block (CLB)可编程逻

2022-12-27 15:54:52 1788

1788 LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

2023-03-13 10:28:06 2053

2053 其中待测设计就是我们整个的逻辑设计模块,在线逻辑分析仪也同样是在FPGA设计中。通过一个或多个探针来采集希望观察的信号。然后通过JTAG接口,将捕获到的数据通过下载器回传给我们的用户界面,以便我们进行观察。

2023-07-25 09:52:58 503

503

逻辑单元在FPGA器件内部,用于完成用户逻辑的最小单元。

2023-10-31 11:12:12 541

541

`在FPGA中,实现逻辑的基本单元是查找表(LUT)而非基本门电路。目前的FPGA中,单一LE或者Cell通常能实现至少4输入查找表的逻辑功能。4输入查找表可以看成是具有4位地址1位数据的存储器

2018-07-30 18:11:19

语言中是不同的。在可综合代码中For循环可以用来拓展复制逻辑。在你完全理解复制逻辑是如何运作之前,千万不要轻易使用for循环。以下是软件语言对HDL语言的转换。[code]// 软件语言例程: For (int i=0; i

2019-08-07 05:00:00

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

请问FPGA逻辑加载方式有哪些?例如flash等

2024-01-26 10:05:13

岗位职责:简历请发邮箱:3406289213@qq.com1、负责产品 FPGA 中通信信号处理单元的开发、仿真与在线测试;2、参与产品威廉希尔官方网站

成果管理,编制FPGA设计各阶段文档,并为专利、威廉希尔官方网站

条件

2017-06-13 16:23:01

本文采用FPGA和ARM结合设计,很好地完成了多通道高精度的数据采集与处理,并且还详细介绍了FPGA逻辑的设计方法。

2021-05-06 06:21:48

图像采集系统的结构及工作原理是什么FPGA逻辑设计中的常见问题有哪些

2021-04-29 06:18:07

FPGA则应该理解为可用电脑编辑的数字逻辑电路集成芯片,其实是在描绘一个数字逻辑电路。关于两者的区别在于以下:1、速度上(两者最大的差别)因为FPGA是硬件电路,运行速度则取决于晶振速度,系统

2021-07-13 08:43:08

FPGA中等效逻辑门概念数的计算方法有两种,一是把FPGA基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA基本单元的等效门数,然后乘以

2012-08-10 14:05:35

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

1.FPGA功能设计上图所示的是FPGA图像处理基板的逻辑功能框图,图中左侧是背板接头,FPGA与背板接头相连的信号主要包括8路3.125G高速数据通道、1路1.3G高速双向数据通道、2路时钟信号

2021-11-10 08:06:26

及路线图详见报到通知)四、 课程简介本课程为期三天,旨在帮助已经掌握一定设计基础的工程师进一步了解FPGA逻辑设计的方法与优化技巧。讲述了逻辑设计的验证、高级状态机的设计、基于FPGA的DSP设计方法

2009-07-24 13:13:48

FPGA电源电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 整个系统需要三档不同的电源电压,即

2015-04-22 12:06:21

` 本帖最后由 rousong1989 于 2015-3-9 18:57 编辑

FPGA是什么(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有

2015-03-08 17:46:44

FPGA与ASIC(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-10 11:34:28

FPGA与CPLD(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-12 13:54:42

资源情况了如指掌,并在编写代码过程中结合器件结构才有可能设计出最优化的代码风格。(特权同学,版权所有)这里我们将和大家一起探讨在绝大多数FPGA设计中必定会而且可能是非常频繁的涉及到的逻辑电路的设计原则、思想或代码书写方式。(特权同学,版权所有)

2015-06-25 09:41:55

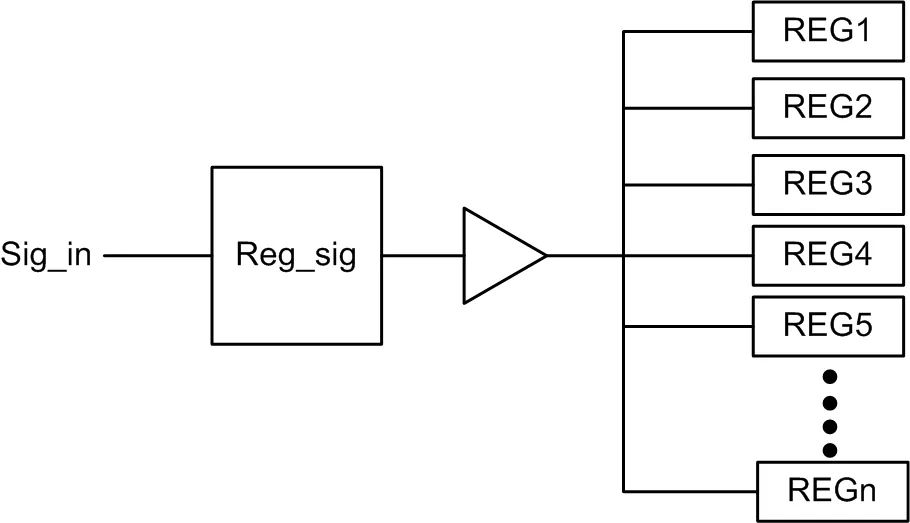

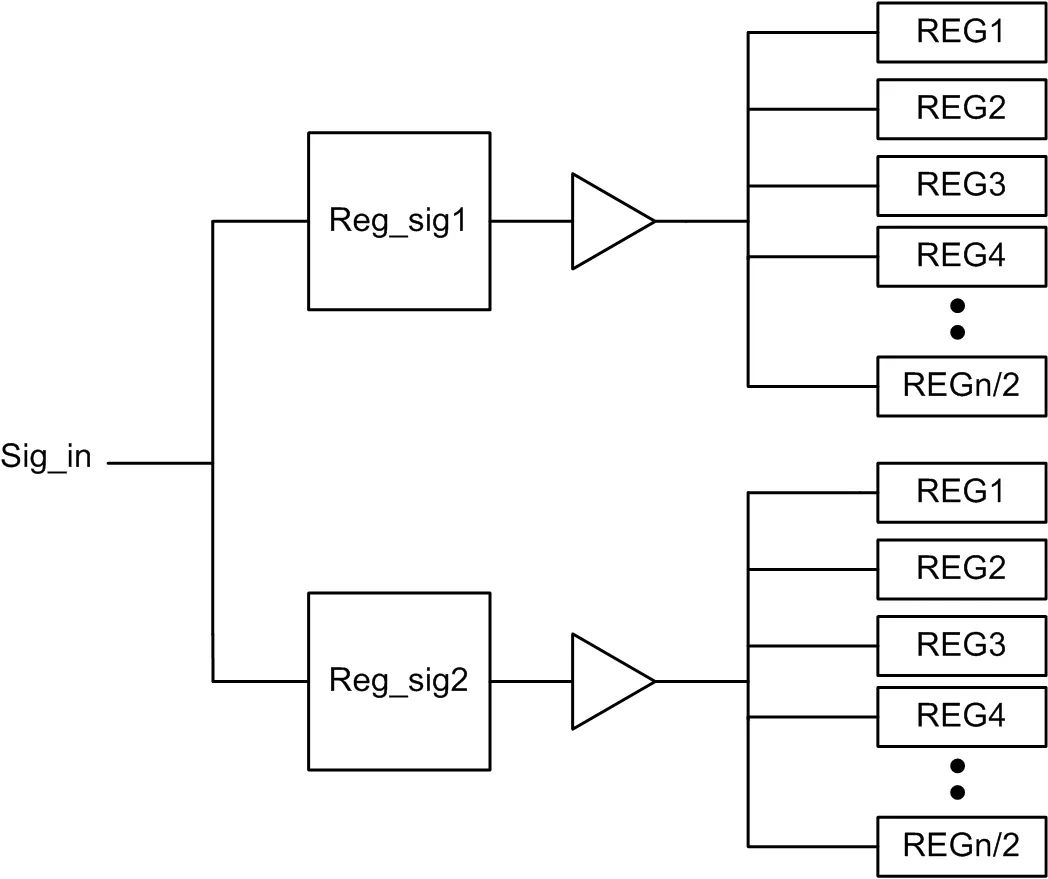

逻辑复制与资源共享本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 逻辑复制是一种通过增加面积来改善时序条件

2015-07-05 19:54:33

消除组合逻辑的毛刺本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 在章节3.2的最后部分对于组合逻辑和时序

2015-07-08 10:38:02

在线调试方式大都是通过FPGA器件引出的JTAG接口,同时使用了一些FPGA片内固有的逻辑、存储器或布线资源就能够实现的。这些调试功能通常也只需要随着用户设计所生产的配置文件一同下载到目标FPGA器件中

2015-09-02 18:39:49

`FPGA应用领域(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-24 11:09:11

FPGA的优势(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-26 11:00:19

FPGA开发流程(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

FPGA实现逻辑函数用的什么电路结构?

2017-01-01 21:49:23

实战应用,这种快乐试试你就会懂的。话不多说,上货。 数字电路中的逻辑代数基础 在数字逻辑电路中,用1位二进制数码的“0”和“1”表示一个事物的两种不同逻辑状态。例:一件事情的是和非、真和伪、有和无、好

2023-02-20 17:24:56

实战应用,这种快乐试试你就会懂的。话不多说,上货。 数字电路中的组合逻辑 根据逻辑功能的不同特点,可以将数字电路分为两大类,一类称为组合逻辑电路(简称组合电路),另一类称为时序逻辑电路(简称

2023-02-21 15:35:38

;nbsp; 同时随着FPGA在整个系统中开始扮演越来越重要的角色,FPGA的接口威廉希尔官方网站

,以及与外部处理器、功能芯片之间甚至是其他系统之间的接口威廉希尔官方网站

也成为FPGA

2010-03-10 17:52:19

;nbsp; 同时随着FPGA在整个系统中开始扮演越来越重要的角色,FPGA的接口威廉希尔官方网站

,以及与外部处理器、功能芯片之间甚至是其他系统之间的接口威廉希尔官方网站

也成为FPGA

2010-03-10 17:58:29

的if--else语句通常会生成优先级译码逻辑,这将会增加这些路径上的组合时延用来产生复杂逻辑的Case语句通常会生成不会有太多时延的并行逻辑五...组合逻辑的always块中,要注意所有的输入全部放入敏感变量表里比如:always@(a or b)beginout=(a&b&c);

2018-03-24 11:04:41

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

fpga通过什么实现逻辑功能,以超级马里奥为例子讲述FPGA有些制作。1、FPGA游戏目标没有CPU,单纯用 FPGA 的verilog硬件语言来实现一个游戏,而这个游戏还得符合老师要求,由于没有

2021-07-22 07:07:25

摘要:逻辑分析仪作为基础仪器,应该在基础数字电路教学中得到广泛应用。本文介绍了基于FPGA的液晶显示控制设计方案,通过使用OLA2032B逻辑分析仪,对控制线进行监测与分析,保证设计方案的准确性

2017-10-19 09:07:43

MPEG-2编码复用器中的FPGA逻辑设计,看完你就懂了

2021-04-29 06:13:34

;nbsp; 同时随着FPGA在整个系统中开始扮演越来越重要的角色,FPGA的接口威廉希尔官方网站

,以及与外部处理器、功能芯片之间甚至是其他系统之间的接口威廉希尔官方网站

也成为FPGA

2010-04-16 14:48:22

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。OV5640提供了一个DVP接口用来输出采集到的图像数据流,本文提供了一个将DVP接口的图像

2020-02-18 19:56:10

本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。 10路逻辑分析仪实例基于芯航线FPGA学习套件进行开发,实例使用到了芯航线FPGA学习套件的FPGA

2020-02-17 18:16:57

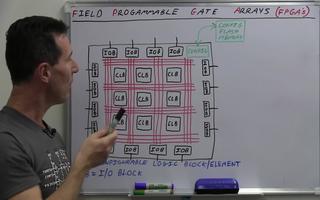

连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能

2019-08-11 04:30:00

`FPGA的逻辑单元_CLB_项目代码文件`

2021-03-31 11:18:02

FPGA设计中,如何通过编写VerilogHDL代码达到预期的设计要求。2 设计技巧5 c) l5 |% xB% v: y+ D/ _& L$ a9 m2.1 如何减少关键路径上的组合逻辑单元数

2020-08-31 18:49:10

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

1、FPGA开发板上组合逻辑电路的设计实现在之前的文章中已经介绍过了安路EG4S20 FPGA开发板以及TD工具的使用,从这篇文章开始,我们将介绍和分享一系列的基础实例,期望能帮助大家逐步

2022-07-21 15:38:45

可编程逻辑芯片 FPGA 中的CYCLONE IV系列的芯片·主要指标中的速度级数代表什么意思?

2012-09-13 21:29:48

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

FPGA设计中,如何通过编写VerilogHDL代码达到预期的设计要求。2 设计技巧5 c) l5 |% xB% v: y+ D/ _& L$ a9 m2.1 如何减少关键路径上的组合逻辑单元数

2020-09-25 11:11:30

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于FPGA的简易逻辑分析仪

2012-07-19 19:01:30

一定难度。而且要更改FPGA内部的逻辑也不是十分灵活。本文探讨一种在嵌入式系统中,灵活,方便地动态配置FPGA 的方法。 具有FPGA 设计能力的硬件工程师可以设计各种F...

2021-12-21 06:13:49

海,我们为我们的项目采购了Kintex 7(XCKU115-1FLVA1517I)。在那里,我需要模拟从FPGA到连接器的PCIe(5 Gbps)线路的SI分析,因为使用了CML逻辑,但在IBIS

2020-04-13 09:58:43

脉冲重新置于FPGA逻辑中,然后将此时钟输入PLL以生成系统时钟。这是一个学校项目,但我不确定这是否会奏效。谁能给我建议这个想法是否有效?如果没有,你能说出理由吗?

2020-08-26 15:09:45

推动FPGA调试威廉希尔官方网站

改变的原因是什么外部逻辑分析仪受到的限制是什么如何用内部逻辑分析仪调试FPGA

2021-04-30 06:44:08

我想在CF卡中存储一些图像,因此它们可以被FPGA逻辑读取,但我不知道该怎么做。有没有关于它的教程?谢谢

2019-08-26 06:42:33

逻辑门控无法映射到Vivado中的一个时钟区域时,BUFHCTRL能够复制自身并将逻辑映射到多个时钟区域吗?谢谢,雨翔

2020-07-27 14:26:34

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

2GHz)的传输速率运行。NoC为FPGA设计提供了几项重要优势,包括:提高设计的性能。减少逻辑资源闲置,在高资源占用设计中降低布局布线拥塞的风险。减小功耗。简化逻辑设计,由NoC去替代传统的逻辑去做高速

2020-05-12 08:00:00

要使用哪种方法去验证 FPGA 的逻辑设计?FPGA的优缺点是什么?

2021-04-08 06:57:32

一种基于FPGA威廉希尔官方网站

的虚拟逻辑分析仪的研究与实现:逻辑分析仪的现状" 发展趋势及研制虚拟逻辑分析仪的必要性, 论述了基于FPGA威廉希尔官方网站

的虚拟逻辑分析仪的设计方案及具体实现方法,介绍

2008-11-27 13:13:04 29

29 用VHDL 语言在FPGA 内部编程实现组播复制。本文介绍其实现方法,并给出了时序仿真波形。通过扩展,该设计可以支持多位宽、多路复制,因而具有较好的应用前景。关键词:FP

2009-08-26 08:48:25 10

10 虚拟FPGA逻辑验证分析仪的设计

随着FPGA威廉希尔官方网站

的广泛使用,越来越需要一台能够测试验证FPGA芯片中所下载电路逻辑时序是否正确的仪器。目前,虽然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

基于汉明码的纠错原理.根据对64位数据进行检纠错处理的需要,设计一个利用8位校验码,以实现该功能的算法逻辑,并通过FPGA实现。

2011-09-15 15:14:58 1382

1382

FPGA项目应用之逻辑程序和sdram程序

2016-01-21 11:24:00 18

18 特权出品的《FPGA设计实战(逻辑篇)》 是FPGA的入门经典图书,有讲解和例程,本资料仅仅为交流使用,学习的话请大家购买正版

2016-05-06 11:47:41 0

0 特权出品的《FPGA设计实战(逻辑篇)》 是FPGA的入门经典图书,有讲解和例程,本资料仅仅为交流使用,学习的话请大家购买正版

2016-05-06 11:47:41 0

0 多分辨率图像实时采集系统的FPGA逻辑设计

2016-08-29 15:02:03 6

6 可编程逻辑器件FPGA/CPLD结构与应用

2016-12-11 23:38:39 0

0 PLD可以是低逻辑密度器件,采用被称为复杂可编程逻辑器件(CPLD)的非易失元件构建;也可以是高密度器件,基于现场可编程门阵列(FPGA)的SRAM查找表(LUT)搭建。在可配置逻辑阵列中,除了

2017-09-12 17:08:30 14

14 现场可编程逻辑门阵列器件 FPGA原理及应用设计

2017-09-19 11:26:26 17

17 由于同步动态随机存储器SDRAM内部结构原因导致其控制逻辑比较复杂。现场可编程逻辑门阵列FPGA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。本文设计了一种基于FPGA的SDRAM

2017-11-18 12:42:03 2054

2054

FPGA的用量比较大,基站最适合使用FPGA,基站几乎每一块板子都需要使用FPGA芯片,而且型号比较高端,可以处理复杂的物理协议,实现逻辑控制。同时,由于基站的逻辑链路层,物理层的协议部分需要定期更新,也比较适合采用FPGA威廉希尔官方网站

。

2019-12-27 07:07:00 1710

1710

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 2191

2191

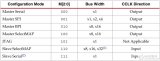

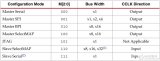

今天咱们聊聊xilinx7系列FPGA配置的相关内容。总所周知FPGA上电后,其工作的逻辑代码需要从外部写入FPGA,FPGA掉电后其逻辑代码就丢失,因此FPGA可以被无限次的配置不同的逻辑代码

2019-10-20 09:02:00 2769

2769

了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps

2020-03-04 15:59:39 1517

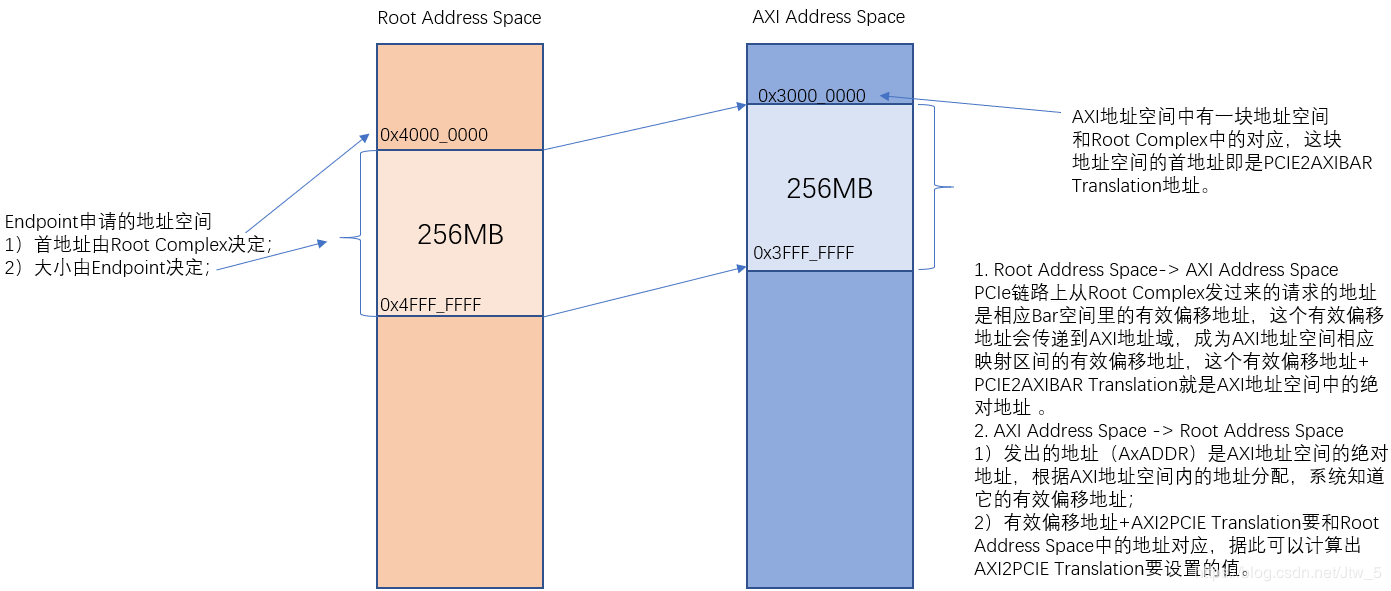

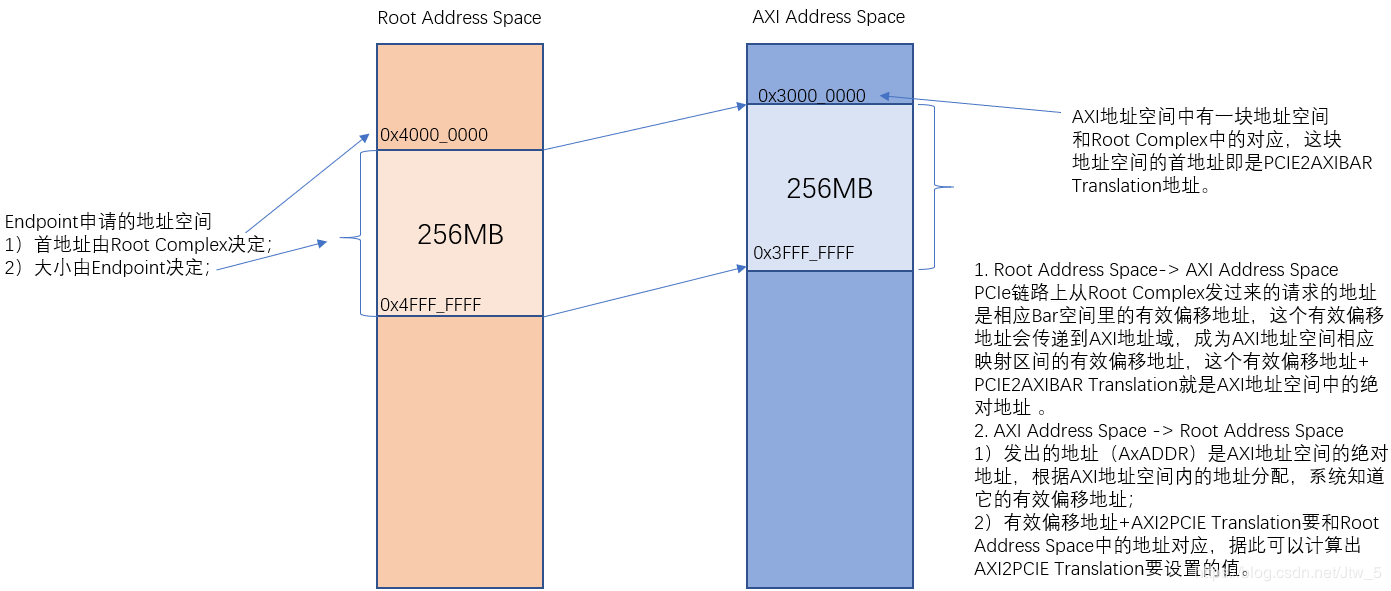

1517 背景与问题 CPU+FPGA架构,CPU做RC、FPGA做EP; FPGA逻辑(Vivado -BD - Address Editor)中如何设置PCIe to AXI Translation

2020-11-20 15:28:52 5783

5783

本文档的主要内容详细介绍的是FPGA硬件基础知识FPGA的逻辑单元工程文件免费下载。

2020-12-10 15:00:31 14

14 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA的逻辑单元的工程文件免费下载。

2020-12-10 15:00:28 19

19 可编程逻辑阵列fpga和cpld说明。

2021-03-30 09:30:05 25

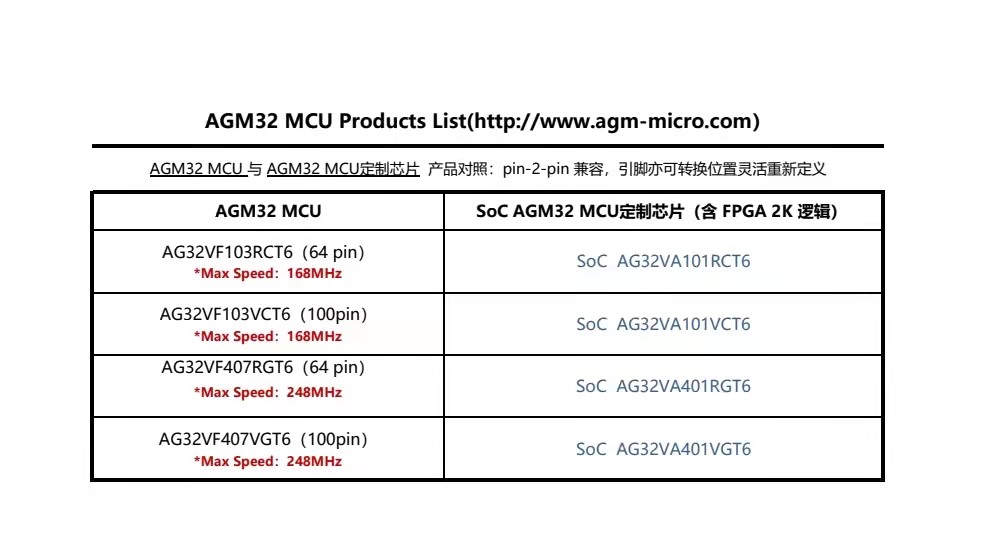

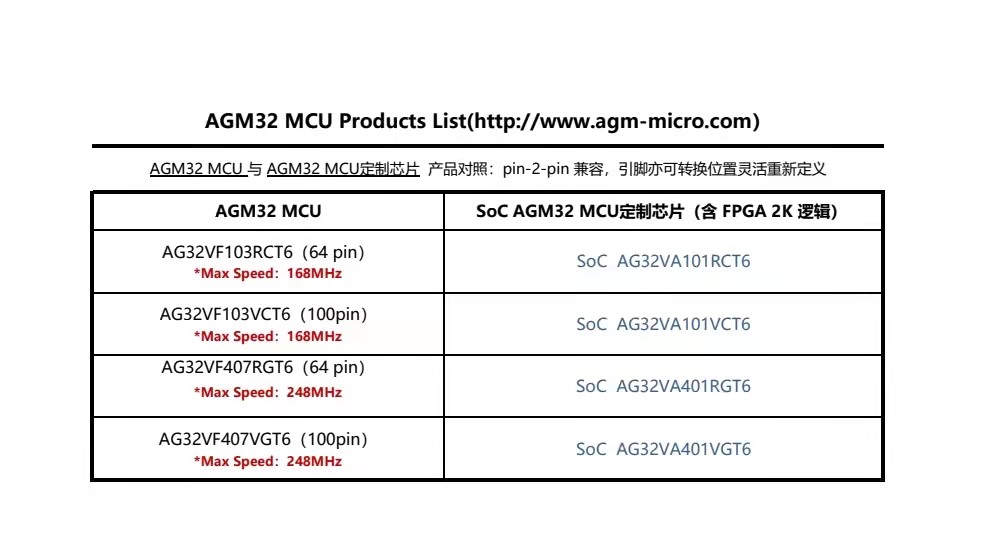

25 国产MCU中唯一内置FPGA逻辑的产品

2022-03-08 10:47:39 3537

3537

在数字化时代的今天,我们都认同数据会创造价值。为了最大化数据的价值,我们不停的建立着数据迁移的管道,从同构到异构,从关系型到非关系型,从云下到云上,从数仓到数据湖,试图在各种场景挖掘数据的价值。而在这纵横交错的数据网络中,逻辑复制扮演着极其重要的角色。

2022-09-22 10:11:43 1091

1091 XILINX是可编程逻辑芯片,由多个系列的性能可以满足一般的逻辑设计要求,如赛灵思7系列,Xilinx®7系列FPGA由四个FPGA系列组成 7A 7V 7S 7K,可满足各种系统要求,从低

2022-11-03 14:39:54 1446

1446 电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 MySQL主从复制是一种常用的数据复制威廉希尔官方网站

,可以实现数据从一个MySQL服务器(主服务器)复制到另一个MySQL服务器(从服务器)。在主从复制中,混合类型的复制是一种较为灵活的复制模式,它可以同时

2023-11-16 14:20:42 246

246 的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时

2023-12-20 13:35:01 147

147

电子发烧友App

电子发烧友App

评论