完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

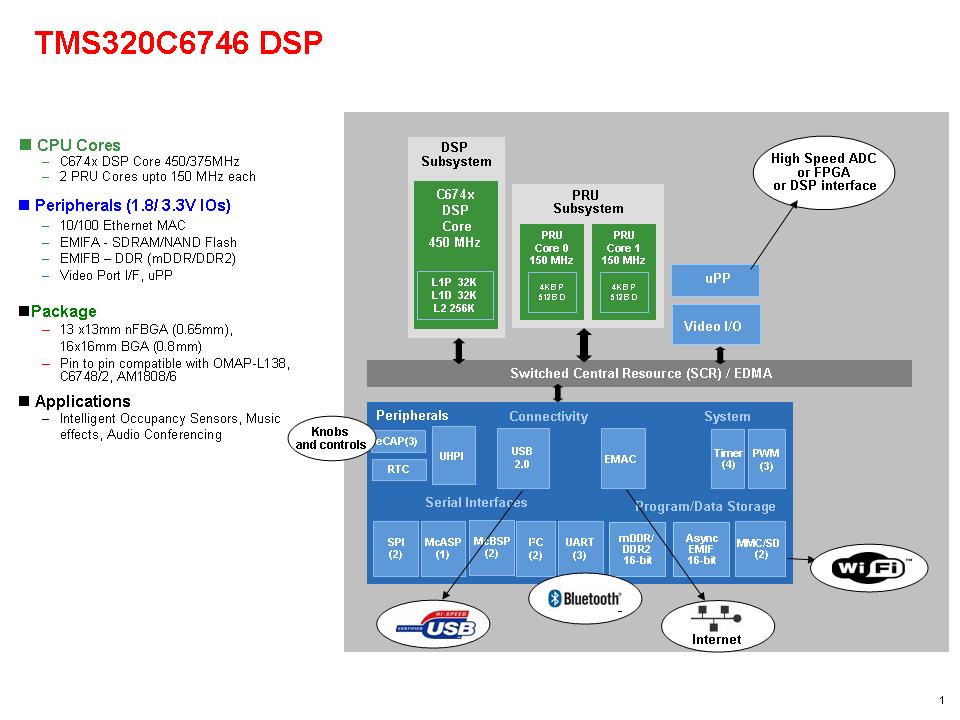

TMS320C6746定点和浮点DSP是一款低功耗应用处理器,该处理器基于C674x DSP内核。该DSP与其他TMS320C6000™平台DSP相比,功耗要小很多。

凭借这款器件,原始设备制造商(OEM)和原始设计制造商(ODM)能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼用稳健操作系统,丰富用户接口和高处理器性能的器件推向市场。

该器件的DSP内核采用基于2级缓存的架构。第1级程序缓存(L1P)是一个

32KB的直接映射缓存,第1级数据缓存(L1D)是一个32KB的2路组相连缓存。第2级程序缓存(L2P)包含256KB的存储空间,由程序空间和数据空间共享.L2存储器可配置为映射存储器,缓存或二者的组合。系统内的其他主机可以访问DSP L2。

外设集包括:1个具有管理数据输入/输出模块(MDIO)的10Mbps /100Mbps以太网介质访问控制器(EMAC); 1个USB2.0 OTG接口; 2个I 2 C总线接口; 1个具有16个串行器和FIFO缓冲器的多通道音频串行端口(McASP) ); 2个具有FIFO缓冲器的多通道缓冲串行端口(McBSP); 2个可配置的64位通用定时器(其中一个可配置)为看门狗); 1个可配置的16位主机端口接口(HPI);多达9组通用输入/输出(GPIO)引脚(每组包含16个引脚,每个引脚均支持可编程的中断和事件生成模式,并且支持与其他外设复用); 3个UART接口(均支持 RTS 和 CTS ); 2个增强型高分辨率脉宽调制器(eHRPWM)外设; 3个32位增强型捕捉(eCAP)模块外设(可配置为3个捕捉输入或3个APWM输出); 2个外部存储器接口(一个是用于慢速存储器或外设的异步SDRAM外部存储器接口(EMIFA),另一个是高速DDR2 /移动DDR控制器)。

EMAC为器件和网络之间提供了一个高效接口。无论是在半双工模式还是全双工模式下,EMAC都支持10Base-T和100Base-TX或者10Mbps和100Mbps。此外,该设备还提供了一个针对PHY配置的MDIO接口.EMAC支持MII和RMII接口。

通用并行端口( uPP)提供了一个连接至多种类型的数据转换器,FPGA或其他并行器件的高速接口.uPP的两个通道均支持可编程的数据宽度,可编程范围为8位至16位。另外,还支持单倍数据速率或双倍数据速率传输以及START,ENABLE和WAIT信号,用以控制各类数据转换器。

视频端口接口(VPIF)提供了灵活的视频I /O端口。

丰富的外设集提供了控制外设以及与外部处理器进行通信的功能。如需了解每个外设的详细信息,请参见本文档中的有关章节以及相关外设参考指南

该器件配有一套完整的DSP开发工具。这套工具包括C语言编译器,用于简化编程和调度过程的DSP汇编优化器以及用于查看源代码执行的Windows ®调试器接口。

All trademarks are the property of their respective owners.

| Operating Systems |

| DSP MHz (Max) |

| Display Options |

| DRAM |

| Operating Temperature Range (C) |

| USB |

| EMAC |

| SATA |

| SPI |

| I2C |

| UART (SCI) |

| On-Chip L2 Cache/RAM |

| Other On-Chip Memory |

| Approx. Price (US$) |

| Applications |

| DSP |

| TMS320C6746 | TMS320C6742 | TMS320C6748 |

|---|---|---|

| SYS/BIOS | SYS/BIOS | SYS/BIOS |

|

375 456 |

200 |

375 456 |

| 1 | 0 | 1 |

|

DDR2 LPDDR |

DDR2 LPDDR |

DDR2 LPDDR |

|

-40 to 105 -40 to 90 0 to 90 |

-40 to 105 0 to 90 |

-40 to 105 -40 to 90 0 to 90 |

| 1 | 0 | 2 |

| 10/100 | 10/100 | 10/100 |

| 0 | 0 | 1 |

| 2 | 1 | 2 |

| 2 | 1 | 2 |

| 3 | 1 | 3 |

| 256 KB | 64 KB | 256 KB |

| 128 KB | 0 | 128 KB |

| 9.00 | 1ku | 6.30 | 1ku | 11.50 | 1ku |

|

Communications and Telecom Industrial Machine Vision |

Communications and Telecom Industrial Machine Vision |

Communications and Telecom Industrial Machine Vision |

| 1 C674x | 1 C674x | 1 C674x |