完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

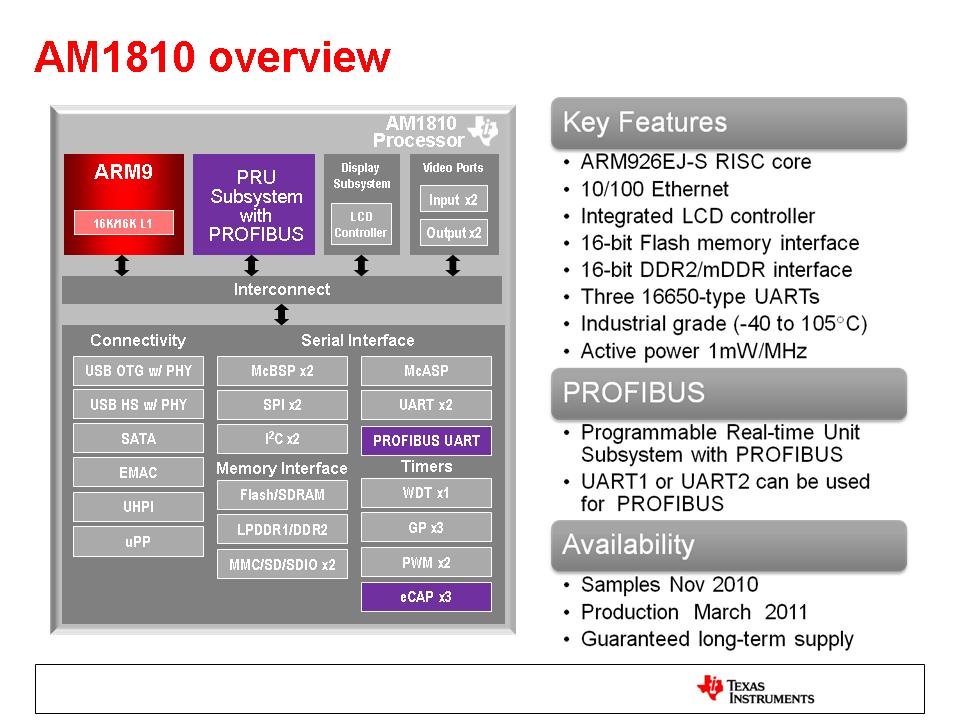

The AM1810 ARM Microprocessor for PROFIBUS is a low-power applications industrial processor based on ARM926EJ-S that is specifically targeted for PROFIBUS applications.

The device enables original-equipment manufacturers (OEMs) and original-design manufacturers (ODMs) to quickly bring to market devices featuring robust operating systems support, rich user interfaces, and high processing performance life through the maximum flexibility of a fully integrated mixed processor solution.

The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of the processor and memory system can operate continuously.

The ARM core has a coprocessor 15 (CP15), protection module, and data and program memory management units (MMUs) with table look-aside buffers. The ARM core processor has separate 16-KB instruction and 16-KB data caches. Both are four-way associative with virtual index virtual tag (VIVT). The ARM core also has 8KB of RAM (Vector Table) and 64KB of ROM.

The peripheral set includes: a 10/100 Mbps Ethernet media access controller (EMAC) with a management data input/output (MDIO) module; one USB2.0 OTG interface; one USB1.1 OHCI interface; two inter-integrated circuit (I2C Bus) interfaces; one multichannel audio serial port (McASP) with 16 serializers and FIFO buffers; two multichannel buffered serial ports (McBSPs) with FIFO buffers; two serial peripheral interfaces (SPIs) with multiple chip selects; four 64-bit general-purpose timers each configurable (one configurable as watchdog); a configurable 16-bit host-port interface (HPI); up to 9 banks of general-purpose input/output (GPIO) pins, with each bank containing 16 pins with programmable interrupt and event generation modes, multiplexed with other peripherals; three UART interfaces (each withRTSandCTS); two enhanced high-resolution pulse width modulator (eHRPWM) peripherals; three 32-bit enhanced capture (eCAP) module peripherals which can be configured as 3 capture inputs or 3 auxiliary pulse width modulator (APWM) outputs; two external memory interfaces; an asynchronous and SDRAM external memory interface (EMIFA) for slower memories or peripherals; and a higher speed DDR2/Mobile DDR controller.

The EMAC provides an efficient interface between the device and a network. The EMAC supports both 10Base-T and 100Base-TX, or 10 Mbps and 100 Mbps in either half- or full-duplex mode. Additionally, an MDIO interface is available for PHY configuration. The EMAC supports the MII and RMII interfaces.

The SATA controller provides a high-speed interface to mass data storage devices. The SATA controller supports SATA I (1.5 Gbps) and SATA II (3.0 Gbps).

The universal parallel port (uPP) provides a high-speed interface to many types of data converters, FPGAs or other parallel devices. The uPP supports programmable data widths between 8- to 16-bits on both channels. Single-data rate and double-data rate transfers are supported as well as START, ENABLE, and WAIT signals to provide control for a variety of data converters.

A video port interface (VPIF) is included providing a flexible video I/O port.

The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections in this document and the associated peripheral reference guides.

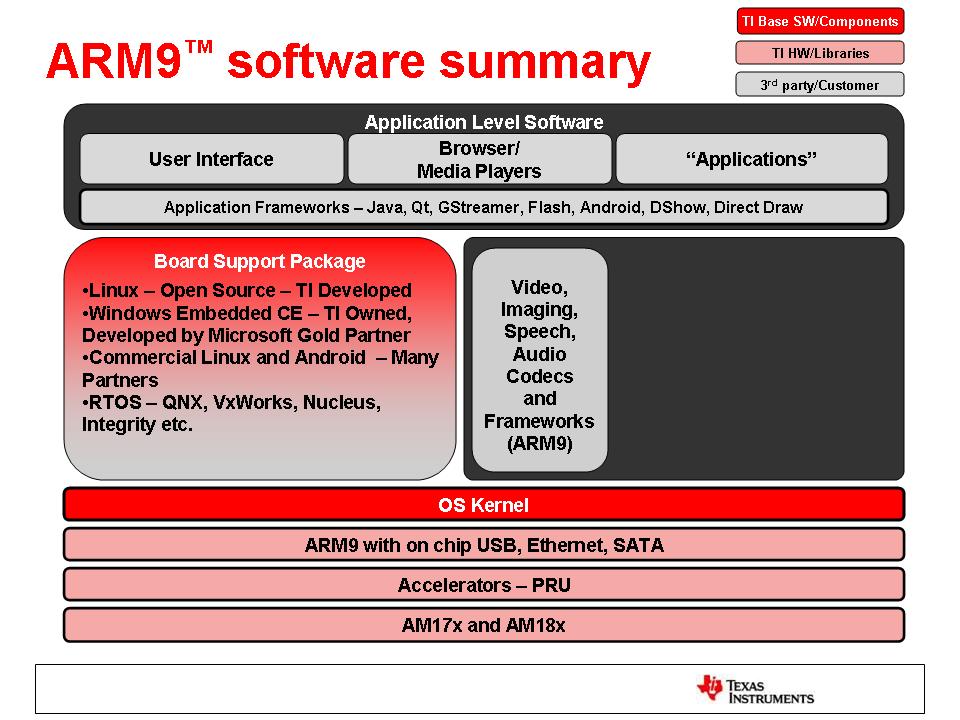

The device has a complete set of development tools for the ARM processor. These tools include C compilers, and scheduling, and a Windows debugger interface for visibility into source code execution.

| Arm MHz (Max.) |

| DRAM |

| Display |

| USB |

| EMAC |

| SPI |

| I2C |

| UART |

| Operating Temperature Range (C) |

| Approx. Price (US$) |

| AM1810 | AM1802 | AM1806 | AM1808 |

|---|---|---|---|

|

375 456 |

300 |

375 456 |

375 456 |

|

DDR2 LPDDR |

DDR2 LPDDR |

DDR2 LPDDR |

DDR2 LPDDR |

| 1 LCD | 1 LCD | 1 LCD | |

| 1 | 1 | 1 | 1 |

| 10/100 | 10/100 | 10/100 | |

| 2 | 2 | 2 | 2 |

| 2 | 1 | 2 | 2 |

| 3 | 3 | 3 | 3 |

| -40 to 105 | -40 to 90 |

-40 to 105 0 to 90 -40 to 90 |

0 to 90 -40 to 105 -40 to 90 |

| 18.53 | 1ku | 8.25 | 1ku | 8.36 | 1ku | 9.28 | 1ku |

| 无样片 |