Controlled Oscillator:VCO)。有了这三个模块的话,最基本的锁相环就可以运行了。但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)

2023-09-03 12:01:12 853

853

锁相环仿真,可以参考一下!

2012-08-13 09:11:17

问一下大家,labview的锁相环怎么设计,我不知道怎么设计NCO,计算频率控制字的时候需要系统时钟频率,但是这个不知道怎么弄,大家有知道的吗,帮一下忙,谢谢!

2017-06-20 10:36:08

要实现锁相环的基本原理及工作状态,如何编写程序呢?

2014-06-11 21:33:38

请问锁相环仿真用什么软件好,我们需要用到ADF4110VOC选择MAX2606

2016-06-27 15:57:53

请问在电子电路中锁相环和鉴相器的电路结构是什么样的?它是如何实现此电路功能的?可否详细解释一下?

2024-02-29 22:34:45

的三相电压,输出是锁住的相角,如果接对称的三相电压,那么输出的电压相角就是a相的相角,打开输出波形,可以看到,输出的相角以0.02s为周期,大小从0变到360°。2、锁相环的基本结构锁相环通常由鉴相器

2015-01-04 22:57:15

我用msp430和adf4106加一个vco 和环路滤波做了一个锁相环,但频率漂到其他地方了!请大神解决

2016-01-20 15:07:57

听说锁相环可以倍频,倍频时输入输出频率都不一样,如何锁相呢?

2023-04-24 10:14:34

锁相环控制频率的原理锁相环频率自动跟踪-------用锁相环可以确保工作在想要的频率点上如何理解以下两段话?鉴相器是相位比较装置, 它把输入信号和压控振荡器的输出信号的相位进行比较, 产生对应

2022-06-22 19:16:46

我有一个锁相环电路的pcb板和proteus仿真电路。

2023-10-04 07:58:55

对于锁相环部分一直有个疑问:1)鉴相器是根据输入信号和输出信号的相位差来输出一个电压,通过LP后,控制压控振荡器的频率输出2)假如输入鉴相器的频率不同,那么电路是如何根据相位差来判断频率之间的差值呢?也就是相位差与频率差之间的关系是怎样的? 有木有相关的资料可以参考?或是请大牛们解释下,多谢啦

2017-07-27 09:03:46

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

第十七章IP核之PLL实验PLL的英文全称是Phase Locked Loop,即锁相环,是一种反馈控制电路。PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程

2022-01-18 09:23:55

电荷泵锁相环的基本原理是什么?电荷泵锁相环的噪声模型与相位噪声特性是什么?电荷泵锁相环的相位噪声与环路带宽关系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 编辑

锁相环PLL原理与应用 第一部分:锁相环基本原理 一、锁相环基本组成 二、鉴相器(PD) 三

2011-12-21 17:35:00

那个对讲机的锁相环的程序怎么写?是基于STM32单片机的,锁相环芯片使用的是LMX2337

2014-04-09 08:18:49

本人在进在做锁相环的仿真,进行频率跟踪的用的,可是怎么做都放不出波形,可有会仿真锁相环的?

2014-06-23 11:14:38

锁相环锁定与失锁的标志是什么?

2023-04-24 10:12:07

锁相环使两个波型相位相同, 当上电时有时两个波相位相同,有时不同是什么原因?急需要答案

2016-03-16 20:57:29

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

用FPGA对AD9516进行配置,配置正常。寄存器回读也对,也能对AD9516进行控制。但是,AD9516的内部锁相环不能稳定锁相。锁相检测信号不断地高低翻转。检查0x18寄存器中表示锁相状态的标志位,该标志位也是不停的调变。这个电路是一个多次用过的电路,以前一直非常好用,从来没有遇到这种现象。

2019-02-19 09:38:47

如题,AD9957的锁相环一直失锁,不用锁相环输出点频信号时正常的,用了锁相环后,PLL_LOCK信号一直为低,sync_clk输出信号也不是稳定的周期信号,环路滤波器的值有点误差,因为现有的器件没有那么精确的电容电阻值,问下锁相环的控制除了控制CFR3之外还有别的要注意的么?

2018-12-10 09:30:24

求一ADF5355_锁相环相关资料,最好中文版,详细点

2017-03-06 23:32:13

新版AD公司锁相环仿真软件

2013-07-20 21:44:03

Actel FPGA PLL锁相环的最大能达到几倍频几分频?我在网上查了一下有人说是20倍频,10分频,但是我没有在芯片手册里面找到资料,想要确认一下。

2014-12-04 11:25:15

锁相有何意义?CD4046的工作原理是什么?CD4046锁相环有什么应用?

2021-05-27 07:07:38

求助,CD4046锁相环的参数要怎么设计呀?我设计的时候是根据datasheet设计的,可是用protues仿真的时候,在中心频率也入不了锁,引脚1输出总是一高一低,然后把输入信号的电压调大后,不管

2020-10-11 13:02:47

LabVIEW锁相环(PLL) 锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环

2022-05-31 19:58:27

在使用K60的过程中发现自己pllinit()不清楚,才发觉自己锁相环的概念还不懂,so,赶紧补补……锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制

2021-11-04 08:57:18

网上Multisim仿真锁相环的帖子很少,本人最近经过摸索仿真了2倍及4倍频。仿真基于Multisim自带的PLL虚拟元件。参数设置是倍频成功与否的关键。

2019-09-08 15:29:59

PLL(锁相环)电路原理是什么?

2022-01-21 07:03:37

`可编程锁相环(PLL)解决方案有多种尺寸和类型可供选择。 PLL以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 可以通过3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

2021-04-03 17:00:58

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF锁相环SFS10625H-LF锁相环SFS10640H-LF锁相环

2021-04-03 17:05:46

STM32L072是低功耗MCU, 但是用内部时钟,通过锁相环倍频到主频32MHz后,执行main函数,SystemClock_Config();函数后,单片机有7mA的功耗,为啥这么大?应该怎么样

2024-03-15 06:03:28

labview虚拟锁相环的跟踪锁定时间过长,请问有什么办法可以解决这个问题

2011-05-17 19:03:34

前辈们你们好,我是在校学生在做锁相环鉴频仿真实验,但是无法得到好的结果,请问前辈们可以指导一下么?谢谢!

2020-06-01 10:20:04

`编辑推荐《锁相环(PLL)电路设计与应用》内容丰富、实用性强,便于读者自学与阅读理解,可供电子、通信等领域威廉希尔官方网站

人员以及大学相关专业的本科生、研究生参考,也可供广大的电子爱好者学习参考。作者简介作者

2017-09-18 17:56:02

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

一种倍频控制单元,通过编程锁频倍数和压控振荡器延迟单元的跨导,有效扩展了锁相环的锁频范围。该电路基于Dongbu HiTek 0.18μm CMOS工艺设计,仿真结果表明,在1.8 V的工作电压

2019-07-08 07:37:37

采用后向Euler数值积分法实现二阶锁相环的一个仿真模型,对二阶锁相环进行仿真,那位大侠做过?可以参考下原代码不?

2012-05-28 17:21:05

目标:以10或40MHz的差分时钟经2~5米长的电缆传输到至少两块线路板上,倍频为200MHz的时钟;要求此两板上的200MHz时钟保持同步,或者说在每次上电的情况下保持恒定的相位关系。 锁相环

2018-09-18 11:14:35

全数字锁相环的设计及分析 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数

2010-03-16 10:56:10

=rgb(0, 66, 118) !important] 锁相环电路主要用于分频倍频,频率合成,解码… 该电路利用VOC的锁定工作,有良好的特性及抗干扰性能。 鉴相器是个相位比较装置。它把输入信号

2019-03-17 06:00:00

有没有大神有用Verilog代码写的数字锁相环程序呀,求 。谢谢

2017-07-05 22:54:56

小弟需要对正弦信号进行锁相,就是锁相环的输入输出都是正弦信号,有合适的芯片吗?最好给点资料,小弟急需!!还有芯片要可以外接倍频单元。在此谢过了!!!

2011-03-13 09:46:00

请问可以用锁相环来制作DDS吗?并且用单片机控制

2016-06-28 17:51:01

一、内容继续无霍尔的学习,根据原理及仿真,了解相关原理和实现方法。二、知识点1.基于锁相环的转子位置估计反正切函数的转子位置估算由于是根据估算的扩展反电动势进行计算的,但是由于滑模控制在滑动模态下

2021-08-27 06:54:13

随着集成电路威廉希尔官方网站

的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

锁相环是倍频电路的主要实现方式,直接决定倍频的成败。传统的锁相环各个部件都是由模拟电路实现的。

2019-10-18 08:01:28

相同的方法用lead产生一个dec信号,用lag信号产生一个inc信号。至此,整个数字锁相环已经设计完毕。步骤中提到的计数器就相当于积分,phase的作用就是完成鉴相,第10步也就是一些有关数字锁相环的书籍

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了

2018-09-06 15:11:00

fpga中的用锁相环产生时钟信号相比于用计数器进行分频有哪些优点,看fpga中锁相环的结构,其前期的输入信号和后期的输出信号不也是通过计数器进行分频实现的吗

2014-10-06 10:46:05

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

大家好,我的课题是要用FPGA做一个高精度锁相环。这个数字锁相环的工作原理为:正弦模拟信号通过低通滤波器后,经过模数转换器(ADC)转化为数字信号,与NCO(数控振荡器) 的输出信号相乘后滤波,从而

2016-08-15 11:31:56

AD9558 / PCBZ,AD9558评估板是一款低环路带宽时钟倍频器,可为许多系统提供抖动清除和同步,包括同步光纤网络(OTN / SONET / SDH)。 AD9558产生的输出时钟与最多

2019-02-27 11:17:12

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

请教一下大神锁相环是如何实现倍频的?

2023-04-24 10:15:39

如题:1. 倍频器的输入信号和输出信号的相位关系能否用相应的公式来进行表征?2. 锁相环的参考和输出信号的相位关系是否和倍频器的输入输出信号的相位关系类似?3. 分频器的输入输出信号、DDS的参考信号和输出信号的相位关系是否跟倍频器的输入输出信号相位关系类似?

2018-10-12 09:10:46

您好,我们目前在做一个调频连续波的雷达,DDS输出50~60MHz,使用ADI的锁相环ADF4108 96倍频至4.8GHz~5.8GHz,扫频周期4ms,点频测试时锁相环的相位噪声还可

2018-08-16 07:18:19

怎么设计一种用于多路输出时钟缓冲器中的锁相环?锁相环主要结构包括哪些?

2021-04-20 06:27:26

软件锁相环的基本模型软件锁相环的数学模型多速率条件下的软件锁相环软件锁相环的DSP实现

2021-04-21 07:22:49

我刚接触锁相环没多长时间,最近想使用ADF4106搭建一个双环锁相环,我阅读的资料都没有说主环路环路滤波器参数计算问题,我想咨询专家ADIsimPLL是否可以仿真计算双环锁相环,如果可以具体怎么考虑,如果可以告诉我一些主环路环路带宽的知识就更好了.

2019-03-07 10:34:03

音频锁相环相关资料集很多好资料哦! [hide]音频锁相环相关资料等.rar[/hide]

2009-12-04 11:43:03

本帖最后由 gk320830 于 2015-3-7 16:40 编辑

高速数字锁相环的原理及应用

2012-08-17 10:47:04

本文针对一款应用于大规模集成电路的CMOS高频锁相环时钟发生器,提出了一种可行的测试方案,重点讲述了锁相环的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的锁相环模块,该测试方案既可用于锁相环的性能评测,也可用于锁相环的生产测试。

2021-04-21 06:28:15

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 126

126

锁相型倍频器

2009-04-11 10:27:15 781

781

变容管/阶跃管倍频器,变容管/阶跃管倍频器是什么意思

倍频器(frequency multiplier)是使输出信号频率等于输入信号频率整数倍的电路。输

2010-03-05 10:16:08 2693

2693 本文介绍了锁相环集成电路CD4046 的内部结构功能及特点,并给出在高倍锁相倍频器中的应用。

2011-11-11 15:52:35 420

420 倍频器( frequency multiplier )使输出信号频率等于输入信号频率整数倍的电路。输入频率为f1,则输出频率为f0=nf1,系数n为任意正整数,称倍频次数。倍频器用途广泛,如发射机采用倍

2011-12-07 13:49:04 212

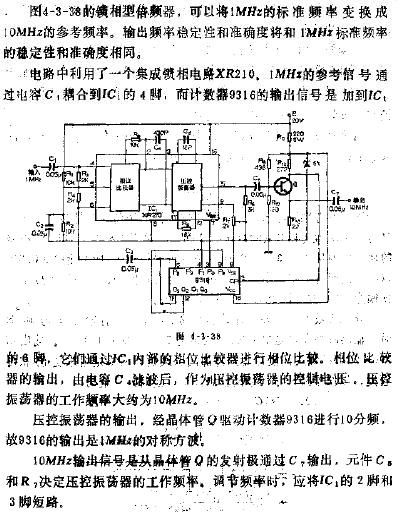

212 关键词:9316 , 倍频器 如图所示为锁相型倍频电路。该电路可以将1MHz的标准频率变换成10MHz的参考频率。输出频率稳定性和准确度将和1MHz标准频率的稳定性和准确度相同。电路中使用的锁相

2018-09-28 09:41:01 716

716 本视频主要详细介绍了倍频器分类,分别是参量倍频器、三极管倍频器、锁相倍频器、阶跃二级管倍频器。

2019-01-08 14:43:52 5777

5777 PLL锁相环倍频是一种用于改变输入信号频率的威廉希尔官方网站

,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56:35 1938

1938 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理威廉希尔官方网站

,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 1508

1508 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 1594

1594 锁相环倍频器锁在基频怎么办? 锁相环倍频器是一种基于相位锁定原理的电子设备,它能够将输入信号的频率倍增。然而,有时候锁相环倍频器会锁在基频上,导致无法达到所要求的倍频效果。这时候,我们需要采取一些

2023-09-02 15:12:31 369

369

电子发烧友App

电子发烧友App

硬声App

硬声App

853

853

126

126 2693

2693 212

212 716

716 1508

1508 1594

1594 369

369

评论