2011年泰国的洪水把机械硬盘的价格推高了不少,却给SSD固态硬盘带来了一个新的发展契机,光刻威廉希尔官方网站 与半导体威廉希尔官方网站 的快速发展,也让SSD的成本方面逐渐降低。随着SSD在消费级市场的普及,用户也开始关心SSD存储颗粒的相关威廉希尔官方网站 ,读者也渴望了解主流SSD存储颗粒的相关知识。下面我们将向读者解析目前MLC NAND颗粒所采用的威廉希尔官方网站 并深度剖析最新的20nm存储颗粒的结构设计与生产工艺,最后重点讲述下一代存储颗粒的原理与发展潜力。

相信大多数用户对SLC存储颗粒与MLC存储颗粒都有一定了解。MLC存储颗粒与SLC存储颗粒相比,以相同芯片面积上获得两倍存储容量的成本优势迅速赢取了消费级用户的青睐。SLC存储颗粒则退居追求高性能、稳定性的企业级市场。虽然所有厂商的MLC存储颗粒的原理基本相同,但因生产工艺与威廉希尔官方网站 的不同,它们之间也存在着一定的差异。最大的差异就是存储颗粒的接口标准,以英特尔、美光、海力士为主的ONFI(Open NAND Flash Interface)接口标准联盟;三星和东芝组成的Toggle DDR Model接口标准联盟。

ONFI阵营全家福。

现在ONFI接口标准已经发展到第三代,采用了DDR(Double Data Rate)信号威廉希尔官方网站 与同步时钟控制,传输带宽达到了400MB/s。同时将SSD主控芯片中的ECC纠错功能集成到了存储颗粒内部,增加了主控芯片的效率。Toggle DDR接口标准也发展到了第二代,它与前者最明显的差别在于采用了异步时钟控制。同步时钟控制是主控可以通过发送同步指令激活闪存上的同步时钟信号,使闪存与主控工作在同步模式,此时闪存的数据传输速率会大幅度提升。而Toggle DDR接口标准采用异步设计,异步时钟控制在主控发出指令以后,主控与闪存之间有一个时钟信号匹配的过程,然后再传输数据。

在理论上,异步时钟控制的时间延迟肯定是落后同步时钟控制。虽然如此,依靠三星和东芝在NAND方面的优势,Toggle DDR接口标准在各项威廉希尔官方网站 产生上并没有落后老牌的ONFI接口标准,传输带宽也达到了400MB/s。加上现在主控的威廉希尔官方网站 差异,两种接口标准的产品在实际测试体验差别不大,玩家们也不需要纠结选择何种存储颗粒,只要选择适合自己的就可以了。至于这两种接口的实际体验,可以参见《微型计算机》2012年6月下《“大”“快”人心,两款512GB固态硬盘深度体验》,两款产品分别是采用了英特尔同步颗粒的OCZ Vertex 4 512GB固态硬盘和采用东芝Toggle DDR异步闪存颗粒的浦科特PX-512M3 512GB固态硬盘。

单就原理而言,毫无疑问ONFI的优势还是要强于Toggle DDR,这两种接口标准的争斗我们可以看做是对新威廉希尔官方网站

的探索,它所带来的威廉希尔官方网站

革新的最终受益者仍然是消费者。然而接口也只是SSD存储颗粒的一小部分,最重要的仍然是存储单元,在最小的芯片面积上集成最多的存储容量才是解决SSD成本的根本原因。为了达到这一目的,厂商不断缩小MLC的制程工艺,英特尔目前已经将其工艺升级到了20nm。

英特尔20nm MLC的创新威廉希尔官方网站

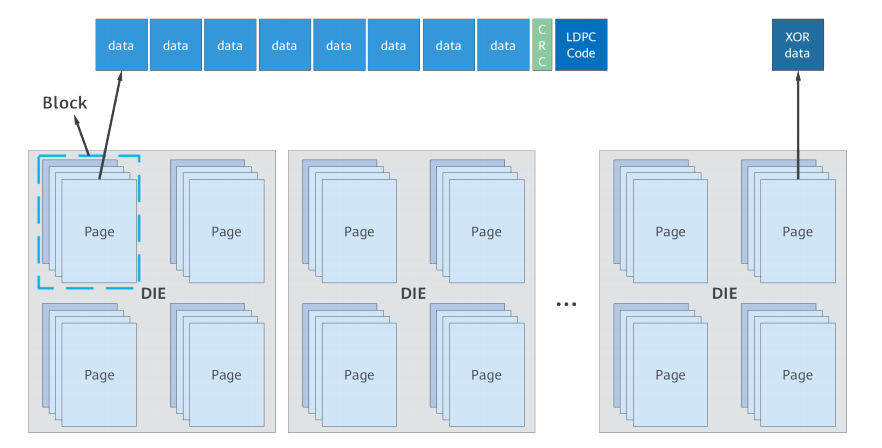

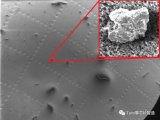

日前英特尔发布了20nm MLC存储颗粒样品,它的芯片面积也减少了不少,以64Gb颗粒为例,20nm工艺的芯片面积为117mm2,英特尔25nm工艺同容量的芯片面积为162mm2,新工艺节约了约30%的芯片面积。当然,这次升级并不只是在工艺上通过光刻来微小化存储单元,结构与材料上仍然发生一定的变化。25nm MLC存储单元的控制栅(Control Gate)和绝缘膜缠绕在浮栅(Floating Gate)上,控制栅与浮栅重合面积绝大多数在侧壁,耦合因子很大程度上也依赖于浮栅侧壁。随着存储单元之间的距离越来近,多晶硅材质的控制栅填入高深宽比的沟道已经非常困难了,单元与单元之间的干扰也越来越大。

为了解决上面的问题,英特尔20nm工艺采用了平面浮栅与控制栅结构,这种结构的浮栅与控制栅相比25m的栅结构减薄了许多。从25nm与20nm剖面图对比可以看出来,浮栅从陡峭的“高山”形状转变成了低矮的“长方形”的形状,控制栅形状也与浮栅类似了,这个结构实现了我们常见的理想化NAND结构。此时带来的问题就是控制栅与浮栅的重合面积越来越小,耦合因子也减少。但高介电常数的IGD栅间绝缘材料与金属控制栅(下简称金属栅)的引入很巧妙地解决这个问题,目前对高介电常数的IGD比常用的ONO(Oxide-Nitride-Oxide)栅间绝缘材料拥有更高的K值,增加了控制栅对浮栅的耦合率。金属控制栅相比多晶硅控制栅,电阻更低,导电能力更强,形成的电场均匀度也好。读者也许会问,如果金属栅有这么多的好处,为什么之前没有采用呢?这与半导体制造威廉希尔官方网站 有关,硅是半导体物质(金属是导体),它一旦沾附金属离子(常见的Na+,Fe2+),则芯片就会失效,半导体制造中的前段和后端作业就是以金属工艺来作为分界线。而控制栅的工艺通常都是在前段作业完成,金属栅的应用必引来金属离子污染,为整个芯片生产线带来巨大的麻烦。

总体而言英特尔20nm存储颗粒给我们还是带来了较多的惊喜,更小的工艺带来更小的芯片面积,成本也自然会下降。截止发稿为止,有关20nm MLC的产品测试显示其性能较25nm产品有所下降。这也在意料之中,小的浮栅电荷存储减少,这将需要更灵敏的控制栅的来判断浮栅中是否存储有“数据”,同时在出错率方面也会大大增加,从而需要更强的纠错功能,这为读写速度带来了一定的拖累。

英特尔25nm与20nm剖面图以及理想的NAND结构。

SSD存储颗粒的未来

客观一点看,这次英特尔发布的20nm MLC存储颗粒只是减少了芯片面积,控制了芯片成本,而没有从根本上解决目前存储颗粒的读写速度与寿命;从原理层面来看,只要是基于EEPROM原理的NAND永远也逃脱不了低寿命、低稳定性的宿命。要么彻底改变存储单元的存储原理,要么新的材料出现,这样才能彻底拯救SSD,下面我们将来看几种可能取代目前NAND Flash的下一代SSD存储颗粒威廉希尔官方网站 。

受材料束缚的FeRAM

我们知道MLC的浮栅威廉希尔官方网站 需使用高电压,迫使电荷穿过致密栅氧化层进出浮栅达到擦写目的。高写入功率和长期的写操作,电荷不停穿梭于栅氧化层,就像离子轰击一样,这对栅氧化层造成物理性伤害。栅氧化层一旦被轰击得“蓬松”,它就会失去“困住”浮栅中电子的能力,那么存储单元就失去了作用。而FeRAM采用与DRAM一样的结构,基本单元由一个MOS管与平面电容组成,平面电容强大的充放电能力带来无穷次读写能力与强悍的读写速度,看看通过软件将DRAM转变成SSD的读写能力就知道了。但DRAM断电以后就会失去数据,它的罪魁祸首是内部平面电容电介质材料无法存储电荷,在断电以后它就会迅速放电,失去存储能力。FeRAM将平面电容的电介质材料换成了具有存储功能的铁电晶体,当在平面电容中加电压时,铁电晶体在电场作用下,大量中心原子在晶体单胞中移动耦合形成铁电畴,铁电畴在电场作用下形成极化电荷。铁电畴在反向电压下所形成的极化电荷较高,铁电畴在正向电压下所形成的极化电荷较低,在断电以后也能保持各自的状态,这种铁电材料的二元稳定状态使得铁电晶体可以作为存储器。

目前这种铁电晶体主要有PZT(锆钛酸铅)、SBT(钽酸锶铋)两种材质。PZT使用最广泛,它的优点是能够在较低的温度下制备,如溅射和MOCVD,原材料便宜、晶化温度较低,工艺集成较容易;但有疲劳退化问题,而且铅会对环境造成污染。SBT最大的优点是没有疲劳退化的问题,而且不含铅;它的缺点是制作工艺温度较高,工艺集成难度很大。另外它们最致命的缺点就是在结构微小化方面有很大的问题,采用纳米级的工艺较难实现。

FeRAM现在已经广泛运用在工业控制,单片机与嵌入式系统中。它与传统的DRAM结构太相似,这在芯片面积上较MLC NAND还是有很大的劣势,从DRAM内存的容量就可以看出来。受制于材料与生产工艺问题,目前FeRAM应用于大容量存储的几率仍然不大。

两种不同结构的FeRAM,Planar结构的工艺相对简单,其隔离采用LOCOS结构,且不需要使用CMP(化学机械平坦化)。而Stacked结构的集成度较高,但是所用工艺相对先进,隔离采用STI,需要使用CMP,并可以使用铜工艺来制作导线。

寡助的PRAM

PRAM与DRAM、FeRAM在结构上还是有相似之处,它在平板电容部分做了结构型调整,采用了GST结晶体作为存储核心,并为结晶体配备了一个加热器。通过加热器对结晶体进行加热控制结晶体状态,在结晶体状态下呈现低电阻状态,加热后呈现非结晶体高电阻状态。由于是晶体结构,在断电以后也能够长时间保持晶体状态,以此表示存储“0”和“1”。这种结构的读写速度与目前DRAM相当,只是在微小化方面较DRAM有很大提高,理论上这种结晶体能够微小化到5nm,取代目前MLC NAND的可能性也较大。只是目前力挺PRAM只有三星和IBM等少数厂商,威廉希尔官方网站 发展潜力较MLC NAND还是有很大的弱势,目前它还停留在研发和试验阶段。

PRAM结构图

离我们最近的3D NAND

前面两种新存储结构在目前应用于大容量存储还不够成熟,东芝、三星与海力士决定通过新威廉希尔官方网站 将MLC NAND的寿命延长,毕竟在MLC NAND的资金投入太大。3D,无论在电影还是半导体行业都成了热门词汇,Ivy Bridge处理器让大家初步认识了3D晶体管,现在3D NAND威廉希尔官方网站 也浮出了水面。东芝、三星与海力士都提出了各自的3D结构,预计在未来三年投入市场,到时候存储颗粒将呈现“百家争鸣”的状态,现在我们以三星和东芝3D结构来先睹3D NAND的魅力。

3种3D构图

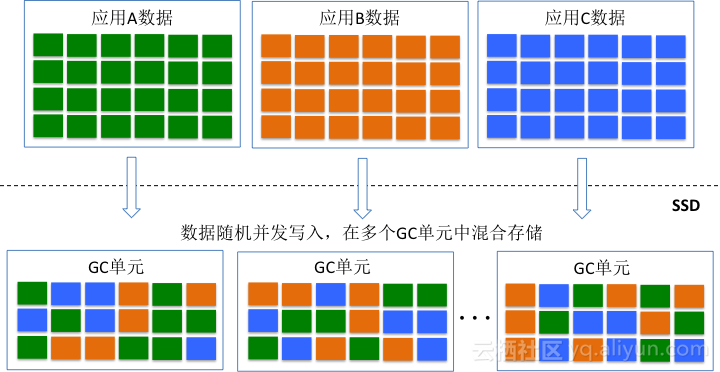

从3D构图可以看出,东芝P-BICS与三星TCAT结构看起来完全不一样,其实它们原理是一样的。首先通过交替淀积多个氧化层和氮化层的方法形成叠层,然后使用湿法蚀刻将叠层中的氮化硅(即氮化层)蚀刻掉,最后填充钨材料形成字线(Word line),位线(Bit line)及触点结构。

可能单就讲解让读者看起来较抽象,先看看结构图(制造流程图),前面我们讲过它是交替淀积多个氧化层和氮化层,图中的灰色部分就是氧化层(Oxide film),黄色就是氮化层(Nitride film),通过干法蚀刻挖出字线(Word line)。然后利用湿法蚀刻掉氮化层,在氮化层部位构建金属控制栅。那么它的存储单元在哪儿呢?就在金属栅周围,只是存储单元不再是多晶硅的浮栅,而是换成了氮化硅(SiN)。氮化硅因为结构特殊,电荷往往会自动积聚到它的晶格周围,有点像靠某种手段强制收集电荷的意思,所以三星将这种结构就命名为电荷捕获型栅级结构。从图中(三星3D结构单元图)我们可以看到在金属栅下面由Al2O3致密氧化物作为与存储单元的隔绝层,底部SiO2是电子穿越层,电子穿过SiO2进入氮化硅而积聚电荷。

制造流程图

看起来这种结构非常的完美,存储单元也很多,但实现起来却非常困难。首先是挖高深宽比的深沟槽问题,由于蚀刻问题,较难实现绝对垂直。其次是它内部结构有凹槽,问题就在于往内部生长致密氧化膜和填充金属栅,高深宽比沟槽必然造成底部与顶部的反应物质不均性,凹槽内的膜厚与表面凹槽内的膜厚肯定会不一样。而且高深宽比沟槽在填充金属栅的时候也容易出现“空洞”,这在半导体制造中绝对是个大忌。不过这种结构还有一个好处就是可以利用过时的制造工艺实现,如50nm工艺,而且生产线投入也没有20nm级工艺大。利用50nm制造出的产品在相同面积上的容量上完全可以赶上现在20nm MLC NAND容量,这样一来存储颗粒的成本也就降下来了。

三星3D结构单元图

大势所趋的ReRAM

相信PC硬件迷们都是知道,最初的机械硬盘体积很大,容量也只有几十兆。巨磁效应的发现让机械硬盘容量有了质的飞跃,而垂直记录威廉希尔官方网站 的应用让机械硬盘容量继续呈线性增长,目前消费级机械硬盘已经达到了4TB。SSD固态硬盘呢?有什么东西让它在容量上也像机械硬盘那样飞跃呢?

3D结构的ReRAM。

答案是忆阻器(Memristor)或者叫记忆式电阻。关于ReRAM的发展和应用,在《微型计算机》8月上的《记忆式电阻—颠覆PC架构的革命?》做了介绍,这里只补充一点它的基本原理、材质与相关大容量存储方案。忆阻器的结构非常简单,与二极管极为相似(只是材料为TiO2)。以TiO2为两个漂移区,一侧为正常成分的TiO2,一侧为少氧的TiO2(写为TiO2-x)。当从左侧通正电压,由于电场作用,右侧TiO2-x中的电子运动到TiO2中,然而TiO2-x中因为结构组成而缺少电子,电子向左侧运动后,右侧完全形成了耗尽区,相当于右侧成了一个断路,整个状态呈现高阻态。当右侧TiO2-x带正电,在电场的影响之下,TiO2中电子向TiO2-x运动,补充TiO2-x本来就缺少的电子,让整个状态呈现一种平衡状态,电阻也低。在断电情况下这种材料能够完全记忆各自的状态,且不需要晶格变化。通过控制电流的变化就可改变其阻值,如果把高阻值定义为“1”,低阻值定义为“0”,则这种电阻就可以实现存储数据的功能,而且电流流过就能立马实现读写,读写时间延迟很小。

研究人员利用这种材料研究出了网格交叉存储单元,就像围棋的交叉格,上下两集电路,交叉点利用忆阻器作为存储单元,每个交叉点就一个存储单元,只需要计算存储点的坐标位置就可以很快实现读写定位。存储单元没有了其他的元件,完全能够解决面积问题,而且能够微小化到10nm以下。由于这种结构简单,工艺难度也非常小,没有3D垂直的深沟槽,没有内部凹槽,但3D NAND的多层堆积也适用。所以ReRAM在芯片面积、容量方面、与工艺难度相对于3D NAND都有较大的优势,在大容量存储方面的应用前景无可限量。

电子发烧友App

电子发烧友App

评论