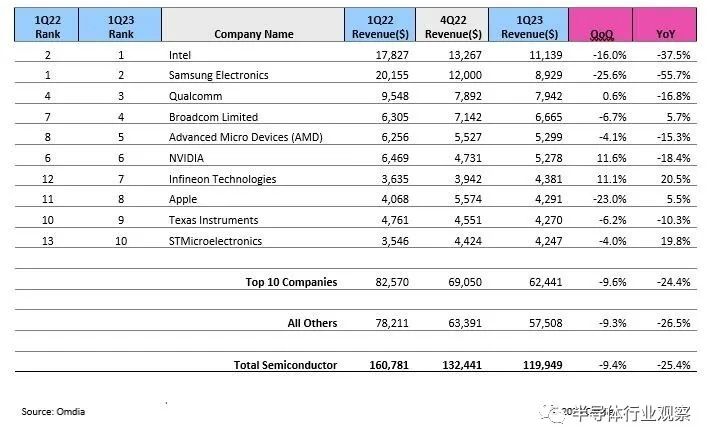

ADI公司的可编程DDS IC(3.5 GSPS AD9914和2.5 GSPS AD9915)拥有高达64-bit分辨率、直接引脚接入和快速频率调谐,适用于精密通信系统。

满足适合无线应用的直接数字频率合成(DDS)威廉希尔官方网站 的要求需要快速跳变和扫描。全球领先的高性能信号处理解决方案供应商ADI最近宣布,公司将以前的DDS集成电路(IC)时钟速度提升了三倍以上。ADI公司的AD9914集成了片内高速12-bit DAC,每秒采样速率达3.5千兆(GSPS),AD9915则可达2.5 GSPS。两种器件内核均支持能够合成频率捷变的高级数字可编程威廉希尔官方网站 ,可在频率高达1.4 GHz下模拟用于各种通信应用(如无线基站、军用和商用雷达)的输出正弦波,还可以保护通信系统。

在本周举行的IMS2012上,新款DDS器件将在ADI公司1725号展位进行演示,该器件内置一个32-bit并行端口,能够极快速改变输出信号的频率、相位和幅度,还具有可编程模数功能,可扩大DDS IC的使用范围,用于需要精确有理数关系的应用,例如信号发生器和其他实验室设备。

ADI公司线性和RF产品副总裁Peter Real表示:“将高分辨率DDS IC的时钟速度提升至3.5 GSPS后,我们的客户可以产生更高的输出频率,同时提升动态性能。ADI公司的新款DDS产品代表威廉希尔官方网站 的重大进步,与前几代产品相比,可在宽得多的频带内实现更佳的无杂散动态范围(SFDR)。AD9914和AD9915改进了SFDR,实现了快速跳频和精密调频分辨率,使设计人员可以在一个时钟周期内通过超精密调频更改频率。

AD9914和AD9915建立时间仅需几纳秒,而粒度远低于200 pHz。其他方法(包括内置嵌入式DDS功能的FPGA)很难在1 GHz以上的输出信号上匹配ADI公司DDS IC的SFDR(优于-50dBc),而且需要较高的工作功率和分立式DAC来合成正弦波。

AD9914和AD9915 DDS IC主要特性:

- 12-bit DAC分辨率、3.5 GSPS (AD9914)和2.5 GSPS (AD9915)时钟速率

- 用于产生精密频率的可编程模数模式和64-bit分辨率

- 1.5 GHz调谐范围内的出色SFDR性能

- 双累加器,用于频率、相位或幅度的线性扫描

- 32-bit并行端口,允许引脚接入,以便调谐字,实现快速精密移位键控和调频

- 全速运转时功耗约2.5 W

3.7 安森美推出针对High-Q IPD工艺的设计套件

应用于高能效电子产品的首要高性能硅方案供应商安森美半导体(ON Semiconductor)宣布提供针对公司High-Q集成无源器件(IPD)工艺的完整从前到后工序工艺设计套件(PDK)。这PDK开发是为了配合安捷伦科技的先进设计系统(ADS) 2011电子设计辅助(EDA)软件一起使用,使安森美半导体及安捷伦科技的客户能够充分利用业界最全面射频(RF)及微波设计平台的优势。

安森美半导体的High-Q IPD工艺威廉希尔官方网站

提供高电阻率硅铜(copper on high resistivity silicon)平台,非常适合用于生产无源器件,如用于便携、无线及射频应用的平衡-不平衡转换器、滤波器、耦合器、双工器及匹配网络。IPD威廉希尔官方网站

用于安森美半导体在美国俄勒冈州Gresham的世界一流200 mm晶圆制造厂制造铜电感、精密电容及精密电阻。IPD为射频系统级封装提供高性价比方案。安森美半导体还为工程原型开发提供经济合算的晶圆厂往返服务。此外,安森美半导体还提供多种应用定制规格的设计服务。

安森美半导体定制晶圆代工及IPD分部高级总监Rick Whitcomb说:“IPD工艺在射频应用极受垂青,我们看到客户极想要这工艺扩展至配合安捷伦的ADS平台。我们为客户提供包括布线和集成EM支援在内的完整ADS设计套件,他们便能利用安捷伦在射频及微波设计领域经证明的专知之优势。”

为客户提供的全功能ADS设计套件可用于布线、仿真及验证,支持电路图驱使型布线生成、布线与电路图对比检验、集成3D平面电磁及3D-FEM仿真器。

安捷伦科技EEsof EDA晶圆制造项目经理Juergen Hartung说:“ADS与IPD工艺完美匹配,ADS与安森美半导体IPD设计套件的组合使相互的客户能够获得高效的集成设计平台。ADS不仅为IPD裸片本身提供完整的从前到后工序应用平台,还直接能设计出包含IPD的完整射频模块。”

3.8 飞思卡尔推出专供智能网络用新一代QorIQ平台

由于前二代QorIQ嵌入式多重核心处理器的成功及广泛的市场接受度,飞思卡尔半导体又推出了第叁代QorIQ产品线的主力-新款的Layerscape系统架构。此一不依赖特定核心、能够认知软体的架构,在现今引进大量互连装置、资料量暴增、安全需求日益严苛、即时服务又正在酝酿、网路通讯样式更是越来越难以预期的态势下,可解决了网路基础设备代工商与日俱增的弹性及延伸性问题。

对于网路系统架构而言,Layerscape架构是一种全新的方法-把软体及可程式性置于优先。它将封包加速及转送运作模组化,不再透过高阶的路由决策处理;让层级之间的互动更为顺畅;运用同步式run-to-completion模型;并在架构中採用标準的C/C++语言,以支援一致的程式化框架。绝佳的程式化弹性与架构延展性,衍生出即时、’软性’的网路控制,保存软体投资,并协助持续进展。

飞思卡尔网路与多媒体解决方案事业群资深副总裁暨总经理Tom Deitrich表示:为了应外界对于更聪明、更富动态网路的需求,飞思卡尔在QorIQ平台上跨进了一大步,推出了崭新的软体认知型Layerscape架构。我们与竞争对手的不同之处,在于我们是将软体认知整合为新架构的一部分,而非事后再拼凑。透过像是不依赖核心的相容特质、独立而高效益的封包处理、加上即时的虚拟化能力等创举,我们等于是提升了网路的智慧」

Layerscape架构係以飞思卡尔广泛的网路智慧财产(IP)产品线为基础所打造,它延伸并拓展了QorIQ资料路径加速架构(Data Path Acceleration Architecture,DPAA)。该产品在设计时即综观了整体系统架构,具备最佳化可程式性,其封包处理效益及相关的效能增长都有突破性的进展。Layerscape架构是未来广大QorIQ多重核心处理器的基础,从可提供高达100 Gbps效能的多核心资料路径元件,到高度整合、成本与能源俱省、运作功率不足3瓦的产品,都巧妙运用了Power Architecture®与ARM®威廉希尔官方网站 。

模组化的Layerscape架构包括了叁种各自独立、可延伸的层级,让飞思卡尔在设计QorIQ元件时,可以视需要轻鬆扩充、减少、甚至抽除某一层级。这叁层分别是:

一般目的处理层(General-Purpose Processing Layer,GPPL)-提供一般目的的运算效能。这一层最适于虚拟云端服务、以及控制面应用

加速封包处理层(Accelerated Packet Processing Layer,APPL)-执行自主封包处理,并让客户以循序的、同步的、run-to-completion的模型自行撰写加值功能,将硬体微架构予以抽象化,为客户提供嵌入式、以C语言为基础的程式模型

快速封包I/O层(Express Packet I/O Layer,EPIL)-促成网路介面之间真正决定性的线速级效能(可高达100G),支援第二层以上的交换功能

Layerscape架构以充裕的开发威廉希尔官方网站 ,协助客户有效地配置、设定、调节及管理採用Layerscape架构的系统,将简单易用提升至前所未有的程度,内容包括:

支援开放标準的软体程式撰写模型及关键性的市场创举,如以软体定义的网路(SDNs)

横跨产品线各层级的单一、一致的架构及软体,从入门级、功率受限的产品,到高阶的多重核心产品

系统侧写及虚拟化工具,有助于详细分析各种场合、并让研发过程更显流畅

专供使用者程式开发、与平台无关的API,称为VortiQa平台服务套件(Platform Services Package,PSP),可用来简化应用的转移。PSP将复杂的硬体抽象化,让大家可以在熟悉的Linux®操作空间裡进行应用研发,并以标準的C语言撰写程式

广泛的研发支援,其中包括由飞思卡尔伙伴们所提供的第叁方工具,RTOSes及全功能的Linux环境。来自飞思卡尔的内部支援则有CodeWarrior整合式开发环境(IDE)、参考设计线路板、先进的编译器、CodeWarrior除错与设定工具、模型及QorIQ最佳化套件等等。此外,飞思卡尔还提供了简单易用的软体程式库、及垂直整合的VortiQa应用层软体解决方案

无与伦比的专业,对于高度先进嵌入式软体工具的投注纪录,加上合作关係,将协助客户从老旧的飞思卡尔产品及/或对手解决方案升级旧有软体,巧妙地保护客户塬有的软体投资,并让产品上市更为顺利。未来採用Layerscape架构的QorIQ处理器,将运用Power Architecture威廉希尔官方网站

。飞思卡尔会持续改良并投注在独步业界的Power Architecture e6500核心上,该核心将是新产品线中效能最佳的核心之一。首件採用Layerscape架构的产品初期样品,预计于2013年中时推出。

——电子发烧友网版权所有,转载请注明出处!

电子发烧友App

电子发烧友App

评论