FPGA原型验证平台与硬件仿真器在芯片设计和验证过程中各自发挥着独特的作用,它们之间存在明显的区别。

2024-03-15 15:07:03 125

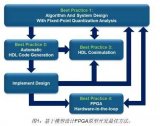

125 FPGA原型验证流程是确保FPGA(现场可编程门阵列)设计正确性和功能性的关键步骤。它涵盖了从设计实现到功能验证的整个过程,是FPGA开发流程中不可或缺的一环。

2024-03-15 15:05:33 92

92 Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 212

212 对评测图书的意见和建议,并把这些宝贵意见反馈给机械工业出版社。通过这些反馈,机械工业出版社不断优化出版品质,为广大读者带来更优质的学习资源。

后续我们将继续与机械工业出版社保持紧密合作,共同策划更多

2024-01-22 10:17:19

proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子EDA。

2024-01-22 09:21:01 546

546

关于 GreenHills Software、HighTec、Synopsys、Tasking、Windriver 的开发环境有什么好处吗?它和 AURIX 开发工作室的区域在哪里?

2024-01-19 08:22:06

FPGA原型设计是一种成熟的威廉希尔官方网站

,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 FPGA设计高级技巧 Xilinx篇

2024-01-08 22:15:53

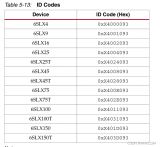

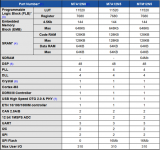

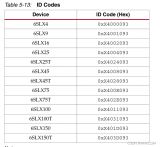

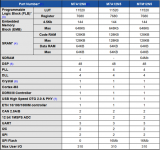

Xilinx 7系列 芯片 应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx( AMD )已延长该系列芯片的生命周期至少到2035年。 本文主要介绍Xilinx 7系列 FPGA

2023-11-28 10:20:02 390

390

xilinx的FPGA,BANK引脚VREF,VRN,VRP都是什么意思?如何使用,DATASHEET没看明白,谢谢请帮忙解答谢谢!

补充一下:Virtex II Pro,XC2VP4,谢谢

2023-11-28 07:19:03

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

电子发烧友网站提供《使用SoC FPGA,实现汽车雷达的数字化处理.pdf》资料免费下载

2023-11-10 10:52:45 0

0 罗彻斯特电子携手AMD/Xilinx,为Xilinx传统FPGA和相关配置PROM产品提供供货支持。

2023-11-07 09:04:42 250

250 一、查找表(Look-Up-Table)的原理与结构

采用这种结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX、APEX系列、Xilinx的Spartan、Virtex系列等

2023-11-03 11:18:38

关于FPGA是不是单片机的问题,很多人反复强调,但遗憾的是,把FPGA当单片机玩的人仍前赴后继。点解?琢磨着有可能是入门方法有误。

回想一下我们是咋学单片机的?买一本教材,了解一下IO口和控制字

2023-11-02 17:27:38

方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢。

2023-11-02 09:48:18 333

333

所有形式的原型都为验证硬件设计和验证软件提供了强大的方法,模型或多或少地模仿了目标环境。基于FPGA的原型设计在项目的关键后期阶段尤其有益。用户有几个原型设计选项根据他们的主要需求,可以选择各种基于软件和硬件的威廉希尔官方网站

来原型他们的设计。

2023-10-11 12:39:41 273

273

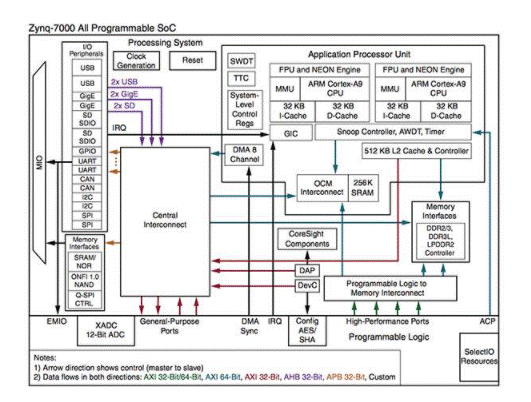

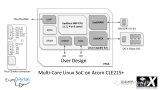

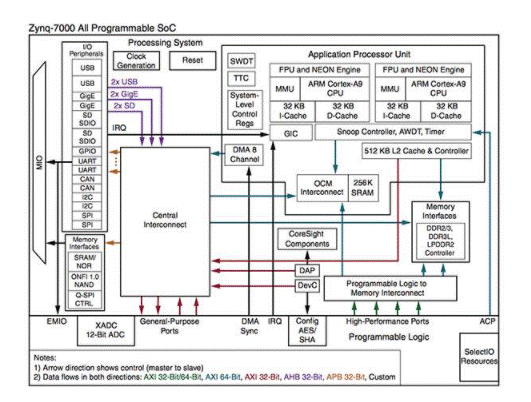

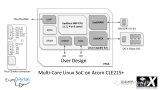

深圳市米尔科技有限公司作为xilinx全球官方合作伙伴,提供基于xilinx soc的全方位解决方案。 z-turnlite是米尔科技推出的一款z-turn精简版开发板。主板基于zynq-7000s

2023-10-09 07:12:11

简述SOC的设计流程跟方法,以及现在市场上跟SOC设计相关的解决方案;接下来我们会将眼光转到OPENCORES,这是一个以opensource的精神推广IC设计的机构,笔者会介绍在OPENCORES

2023-09-20 07:24:04

电子发烧友网站提供《如何将Arm Cortex-M处理器与Xilinx的FPGA和SoC结合使用.pdf》资料免费下载

2023-09-15 15:04:38 1

1 Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 1759

1759

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1941

1941

电子发烧友网站提供《为新时代高性能航天级Xilinx FPGA供电.pdf》资料免费下载

2023-09-14 11:24:36 0

0 电子发烧友网站提供《面向Xilinx FPGA和SoC的超快设计方法指南.pdf》资料免费下载

2023-09-14 10:02:31 1

1 电子发烧友网站提供《Xilinx FPGA和SoC的超高速设计方法指南.pdf》资料免费下载

2023-09-14 09:41:06 0

0 上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

2023-09-13 12:29:37 654

654

电子发烧友网站提供《适用于Xilinx Ultrascale+ FPGA的PMBus稳压器参考设计.pdf》资料免费下载

2023-09-13 09:34:17 0

0 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 758

758

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2347

2347

通过上一篇文章“时钟管理威廉希尔官方网站

”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

应用性能要求的不断提高,SoC FPGA 会成为更广泛应用中的挑战者,还是 MCU 会发展以更好地与 SoC FPGA 竞争?如果您正在考虑一种新设计,那么今天哪种方法最适合您——MCU 还是 SoC FPGA? 本文将快速回顾 SoC FPGA 与 MCU 相比的一些主要优势和劣势。它还将探讨

2023-08-26 10:45:02 1534

1534

/软件验证的方法。本文还讨论了在FPGA和ARM处理器之间建立接口的挑战,以及如何在SoC FPGA上实现设计、划分硬件和软件、生成接口逻辑等问题。此外,文章还提到了数字波形分析和测试覆盖率的方法。

2023-08-21 09:46:13 295

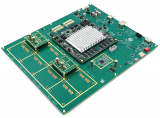

295 MPS2和MPS2+FPGA原型板是ARM Cortex-M评估和开发的开发平台。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上电和配置MPS2

2023-08-18 07:25:28

酷睿™SoC-600是ARM嵌入式调试和跟踪组件家族的成员。

CoreSight™SoC-600提供的部分功能包括:

·可用于调试和跟踪ARM SoC的组件。

这些SoC可以是简单的单处理器设计,也

2023-08-17 07:45:56

Cortex-M1 DesignStart™现场可编程门阵列-Xilinx版本包提供了一种在Xilinx Vivado设计环境中使用Cortex-M1处理器的简单方法。

Cortex-M1处理器

2023-08-16 06:10:25

Corest-M3 DesignStart Eval为开发人员提供了一种开发和模拟基于ARM Cortex-M3处理器的SoC设计的简单方法。

它允许系统设计人员在模拟器上进行设计和测试,然后使用FPGA进行硬件原型设计。

2023-08-12 07:22:43

Cortex-M3 DesignStart™现场可编程门阵列-Xilinx版封装提供了一种在Xilinx Vivado设计环境中使用Cortex-M3处理器的简单方法。

Cortex-M3处理器专为

2023-08-12 07:02:46

Arm MPS3 FPGA原型板配有SO-DIMM存储模块。该模块未在工厂安装,以减少其在运输过程中损坏的可能性。要安装内存模块,首先将其以一定角度滑入插槽(如图2所示),使模块边缘连接器中的插槽

2023-08-10 07:10:30

芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测试平台代码。验证任务在设计周期内可能会占用50%或更多的时间。尽管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以发现系统级错误,芯片设计人员正利用FPGA来加速算法创建和原型设计。

2023-08-06 10:49:09 971

971

前言 本书是针对 CoreSight SoC-400 组件的威廉希尔官方网站

参考手册 (TRM)。rnpn 标识符指示本书中描述的产品的修订状态,其中: rn pn 标识产品的主要修订。标识产品的次要修订或修改

2023-08-02 18:49:42

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

客户为AMD Xilinx SoC创建了PetaLinux工程。需要定制PetaLinux中的FSBL

2023-07-10 17:05:42 586

586 OFDM中调制使用IFFT,解调使用IFFT,在OFDM实现系统中,FFT和IFFT时必备的关键模块。在使用Xilinx的7系列FPGA(KC705)实现OFDM系统时,有以下几种选择。

2023-07-10 10:50:52 604

604

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

2023-07-10 10:43:18 626

626

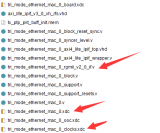

基于RGMII时序广泛应用于以太网通信中,基于Xilinx的三速以太网时序分析,不同的Xilinx系列方法不一样

2023-07-07 14:15:01 2942

2942

,这样就可以通过读取IDCODE,来进行自动区分不同的硬件,分别进行不同的处理方式。本文介绍Xilinx所有FPGA芯片型号IDCODE的获取方法,一共4种方式,总有一种适合你,这些方法同样适用于别的厂家的FPGA/MCU,比如Intel,Lattice,Microchip等等。

2023-07-03 13:01:31 1580

1580

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

2023-06-28 09:08:05 425

425

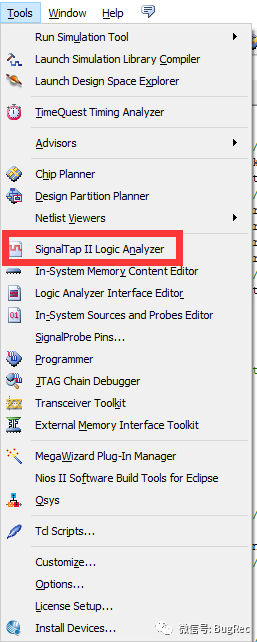

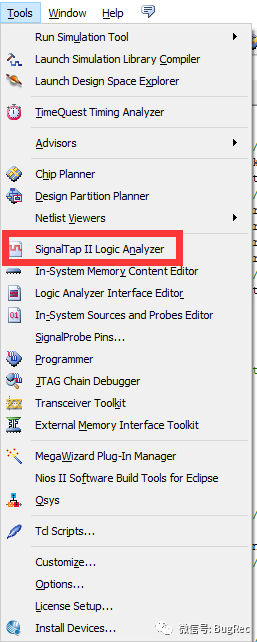

Xilinx被AMD收购的事情把我震出来了,看了看上上一篇文章讲了下仿真的文件操作,这篇隔了很久远,不知道该从何讲起,就说说FPGA的在线调试的一些简单的操作方法总结。

2023-06-19 15:52:21 1224

1224

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-06-19 15:42:08 543

543 综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

2023-06-13 09:27:06 277

277

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5513

5513

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

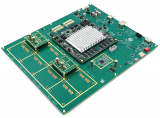

设计中的1/9)要求一个基于多个FPGA的原型开发板。 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity公司的原型开发伙伴生产的开发板——与合适

2023-06-04 16:50:01 699

699 新一代SoC FPGA凭借其强大的并行处理数据的能力和实时性的特点在AIoT领域发挥着独特的作用。随着集成电路的发展,SoC FPGA的性能不断提高,同时较为先进的控制理论和控制算法的成熟。

2023-06-03 12:38:28 610

610

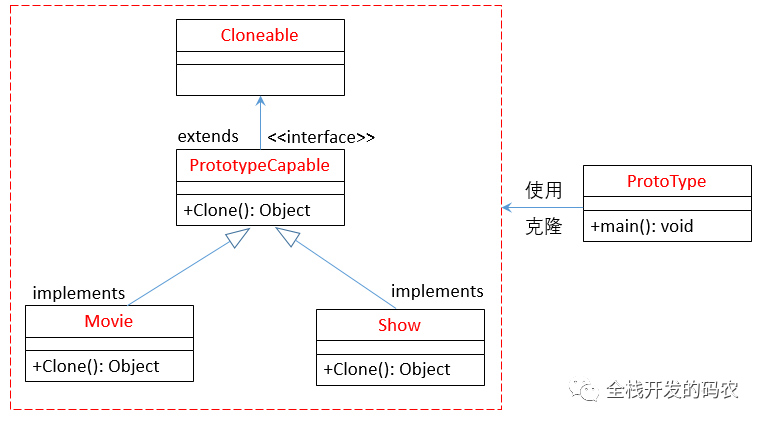

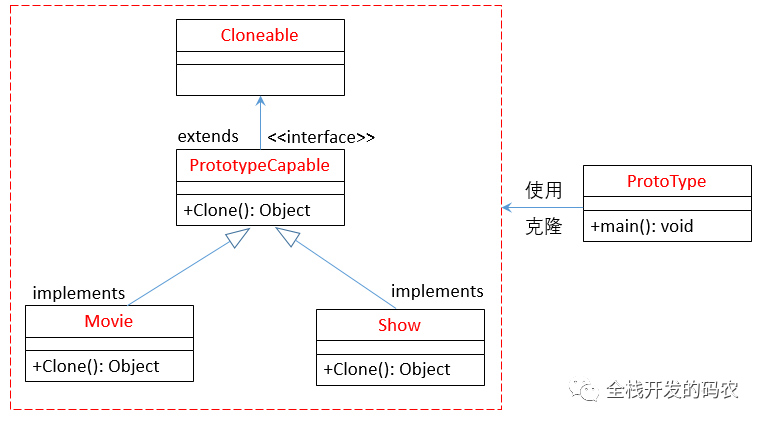

原型模式是指将类设计成可复制(克隆)类型,继承Cloneable类,在调用时就可以直接通过clone()方法克隆已有对象生成新的对象。

2023-06-01 14:18:49 379

379

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-05-30 15:04:06 905

905

我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。

2023-05-30 11:10:27 769

769

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 和大侠简单聊一聊CPU、MCU、FPGA、SoC这些芯片异同之处,话不多说,上货。

目前世界上有两种文明,一种是人类社会组成的的碳基文明,一种是各种芯片组成的硅基文明——因为几乎所有的芯片都是以单晶硅

2023-05-26 17:07:52

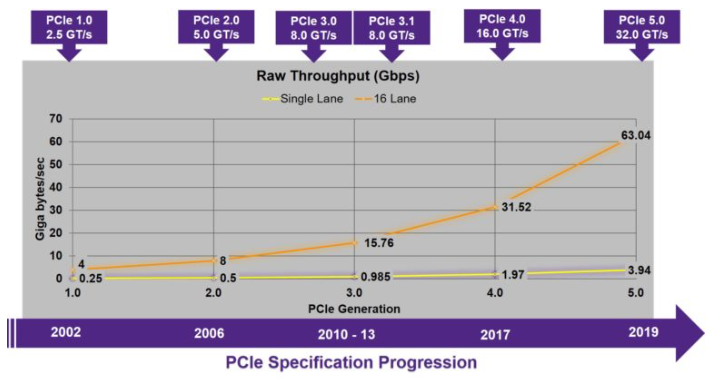

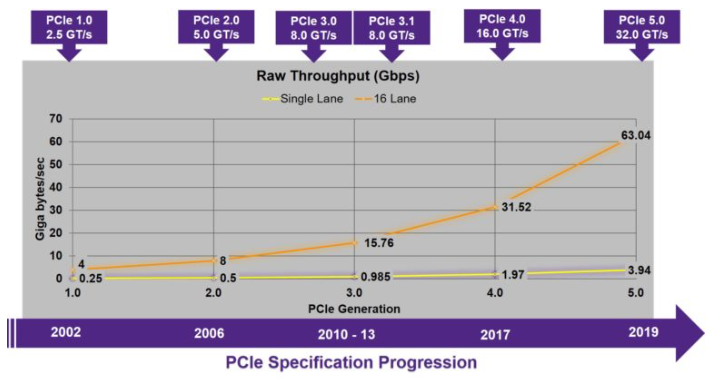

PCI Express® 5.0规范,达到32GT / s的传输速率,同时保持低功耗和与前几代威廉希尔官方网站

的向后兼容性。为此,Synopsys 还宣布与 Astera Labs 合作开发业界首款 PCIe

2023-05-26 10:41:48 955

955

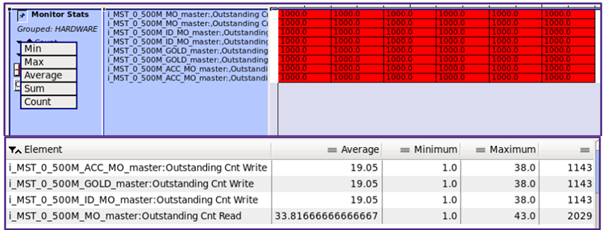

平台 - Synopsys ZeBu®仿真系统和Synopsys HAPS® FPGA原型系统 - 是运行如此大的有效载荷的必要条件。

2023-05-25 15:37:52 543

543

上篇主要是分享了Vivado编译软件远程调试的方法。杰克使用Vivado软件进行远程连接,主要是用于固化程序以及FPGA(PL端)的异常排查。而本篇主要内容是对使用Vitis软件远程调试的方法进行总结和分享。

2023-05-25 14:36:58 1685

1685

日常的FPGA开发常常会遇到“编码与上机调试使用各自的电脑”的场景,解决方法一般如下。

2023-05-25 14:36:44 1751

1751

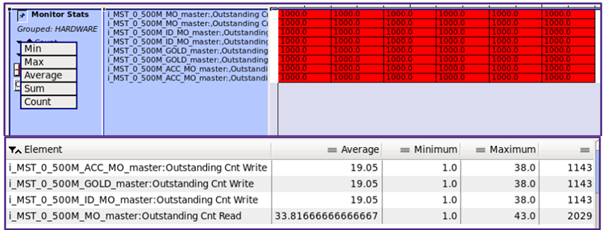

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装威廉希尔官方网站

的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 1149

1149

FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-05-23 16:50:34 381

381

如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 481

481

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-23 15:31:10 319

319 FPGA原型验证的原理是将芯片RTL代码综合到FPGA上来验证芯片的功能。对于目前主流william hill官网

而言,芯片规模通常达到上亿门甚至数十亿门,一颗FPGA的容量难以容纳下芯片的所有逻辑功能。

2023-05-18 12:52:52 381

381

FPGA、可编程SoC的领先者AMD公司一直致力于为客户提供高效、高性能的硬件解决方案,协助完成构思从原型阶段到批量生产的整个过程。

2023-05-16 11:34:47 1231

1231

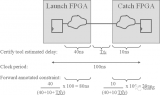

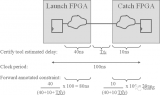

SoC的顶层的约束适用于FPGA到其各自时钟域中的各个Flip_Flop,如果定义了跨时钟域,也适用于FPGA之间。当我们可以确保每个FPGA边界都有一个IOFF,它与SoC中相应的元素对齐时,这一点对于性能而言非常重要。

2023-05-13 09:38:09 1351

1351

FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

2023-05-10 10:44:00 4775

4775

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-10 10:15:16 187

187 多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具

2023-05-08 11:51:40 326

326

在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样。

2023-05-04 16:21:34 426

426

要在业余爱好中制作电路板,有一些即时原型制作方法。我认为大多数人都在使用原型板和 PTFE 线进行性原型制作。但是PTFE线不适合作为原型板的布线材料,因为存在以下问题。

2023-04-28 10:14:37 424

424 对SoC芯片要进行FPGA原型验证,假如设计较大,要将SoC中不同功能模块或者逻辑模块分别分配到特定的FPGA,那么对SoC的分割策略尤为重要

2023-04-27 15:17:06 627

627

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 尽管对于工程师而言目标始终是以原始形式对SoC源RTL进行原型化,但在原型化工作的早期,SoC设计必须进行必要的修改,以适应FPGA原型系统。

2023-04-26 09:48:13 747

747 在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样:

2023-04-25 11:15:20 1629

1629

MIPI 接口现在非常流行,国产FPGA目前基本都带MIPI接口,而AMD-Xilinx是从U+系列开始支持MIPI电平,从国内使用情况来看,7系列FPGA是使用最广的器件,所以这次使用的FPGA是7系列FPGA使用电阻网络实现MIPI电平的例子。

2023-04-24 09:30:06 3704

3704

门控时钟是一种在系统不需要动作时,关闭特定块的时钟的方法,目前很多低功耗SoC设计都将其用作节省动态功率的有效威廉希尔官方网站

。

2023-04-20 09:15:13 764

764 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-04-19 09:08:15 848

848 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:37 442

442 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:03 626

626 FPGA原型设计是一种成熟的威廉希尔官方网站

,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 594

594 当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-04-06 11:20:48 602

602 FPGA原型平台的性能估计与应用过程的资源利用率以及FPGA性能参数密切相关,甚至FPGA的制程也是一个因素。

2023-04-04 09:49:04 1474

1474 摘要:Synopsys.ai可为芯片设计提供AI驱动型解决方案,包含数字、模拟、验证、测试和制造模块。AI引擎可显著提高设计效率和芯片质量,同时降低成本。·英伟达(NVIDIA)、台积公司(TSMC

2023-04-03 16:03:26

FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 924

924 开始SoC FPGA的学习路程还是蛮难的,不仅要熟悉整个的设计流程,而且还要掌握FPGA以及软件方面的知识,尤其大概看了一下后面的整体设计部分,操作起来还是较为繁琐的,以至于让人晕头转向。尽管如此

2023-03-30 10:13:35 6222

6222 BOARD BATTERY FOR SOC'S

2023-03-29 19:51:22

总结Xilinx FPGA 的上电模式可以分为以下4类型: 主模式 从模式 JTAG模式(调试模式) 系统模式(多片配置模式) 1、主模式 典型的主模式都是加载片外非易失( 断电不丢数据

2023-03-29 14:50:06 533

533 我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。

2023-03-28 14:11:15 768

768 Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

以emulator为中心的SoC开发流程。Synopsys 家的Zebu,Cadence家的Palladium和Mentor家的Veloce。其中Zebu就是以Xilinx的高端FPGA为基本元件搭建

2023-03-28 11:14:04

Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4750

4750 在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-03-28 09:33:16 854

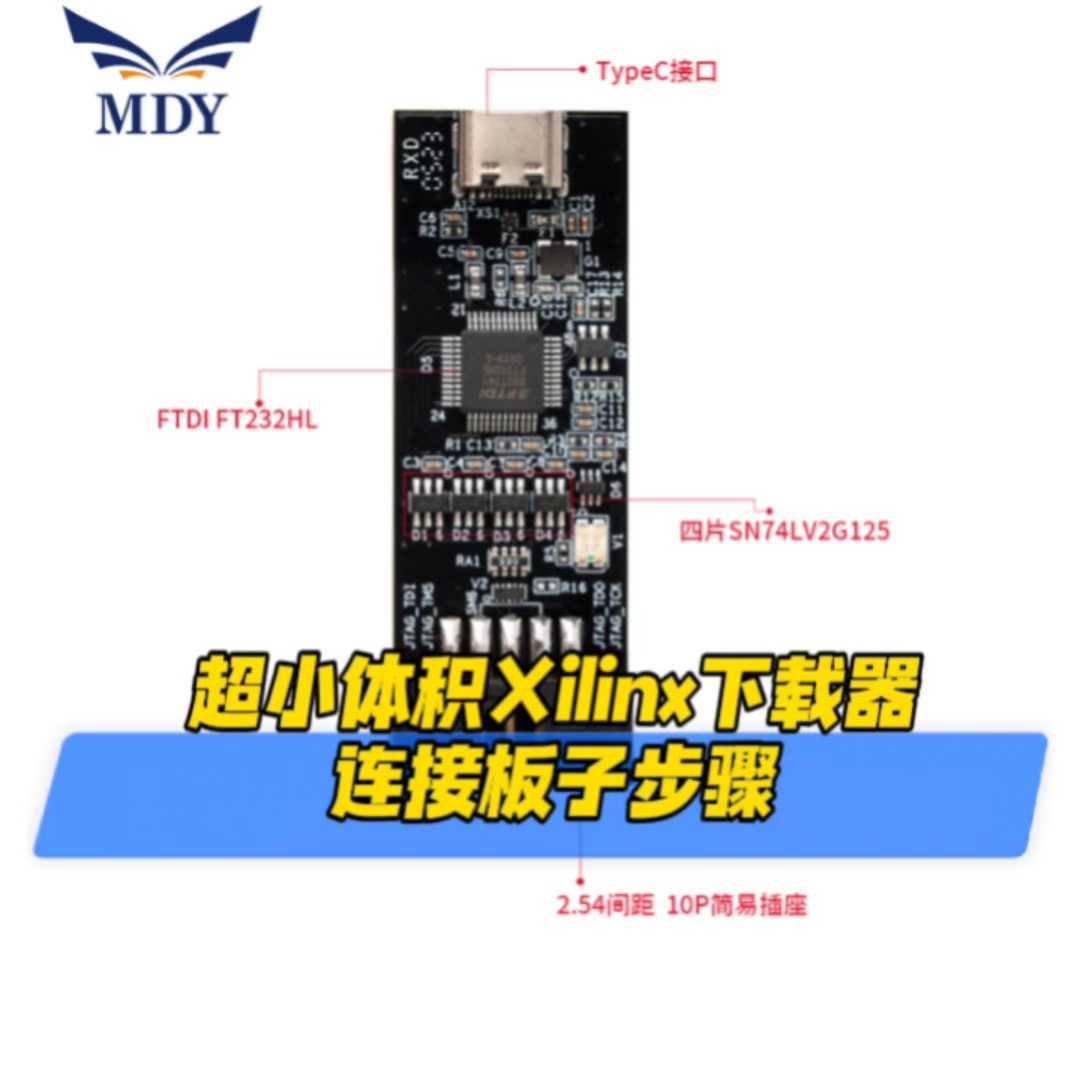

854 支持所有Xilinx器件下载 包括FPGA CPLD ISP Configuration PROM 下载接口电压:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

电子发烧友App

电子发烧友App

评论