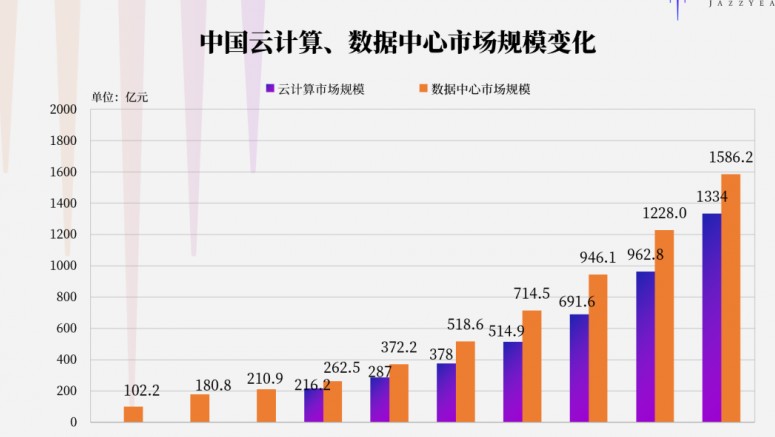

基于云的互联网服务、人工智能和加密货币的出现引发了全球数据中心处理能力的强劲增长。再加上不断上涨的电力和房地产价格,这一趋势对高效紧凑的服务器电源产生了明显的需求。

为了达到所需的更高功率密度,必须考虑以下三个主要因素:

提高效率以在给定体积内保持可接受的总功率损耗。这推动了向新拓扑和威廉希尔官方网站 的过渡。一个很好的例子是从传统的硅经典升压 PFC 过渡到氮化镓/碳化硅图腾柱 PFC。

改进的封装和散热解决方案,可以将功率从器件结消散到散热器和环境中。这在作为高密度转换器主要推动力的小型表面贴装器件 (SMD) 封装中变得更具挑战性。

优化的系统设计和开关频率可在不违反效率要求或温升限制的情况下实现最大密度。这导致开关频率增加,推动了从传统封装和散热解决方案向新封装和散热解决方案的转变。

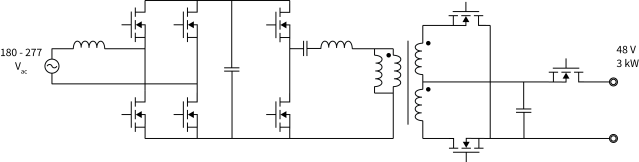

通常,最先进的高效电源由无桥 PFC 级(如图腾柱级)和谐振 DC/DC 级(如 LLC 转换器)组成(见图 1)。服务器电源的示例规格是V in = 180–277 V,V out = 48 V,P out = 3 kW。

图 1:包含图腾柱 PFC 和 LLC DC/DC 转换器的服务器电源

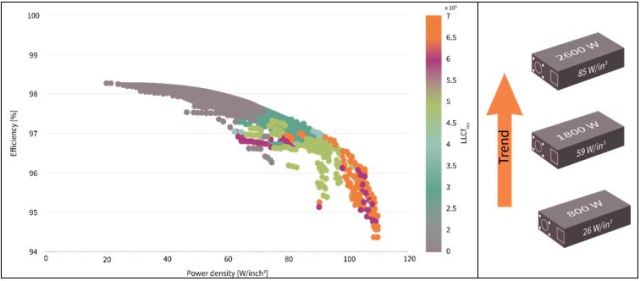

为了量化效率和功率密度之间可实现的性能折衷,应用了帕累托优化方法。该方法系统地考虑了不同转换器系统设计中的所有可用自由度。通过采用详细的系统和组件模型,它可以确定位于帕累托前沿的最佳设计。效率是针对额定输出功率的 50% 计算的,包括 PFC 和 LLC 级损耗。

计算了整个服务器供电系统的帕累托前沿,优化结果如图 2 所示。该图表明,对于中等功率密度(~40 W/ in.3 ) ,效率可以达到接近 98.2% ,而设计超过 80 瓦/英寸。3的效率低于 97.5%。该图中的另一个重要观察结果是更高密度设计所需的 LLC 级的更高开关频率。这些观察结果证实了封装以更高的频率和更高的效率运行的必要性。

图 2:显示效率与密度的整个服务器电源的优化结果,以及最佳 LLC 级频率

SMPS 拓扑中使用的 SMD 封装

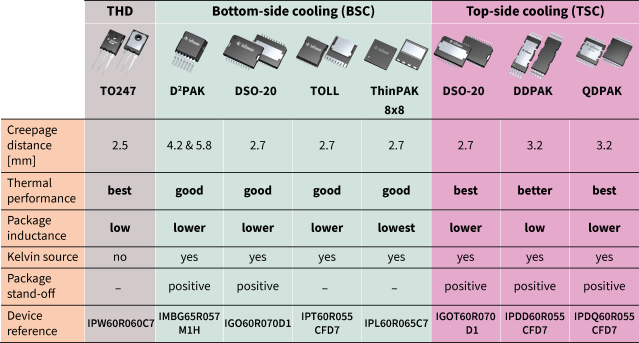

英飞凌提供更广泛的底部冷却 (BSC) 和顶部冷却 (TSC) 封装产品组合,可满足服务器开关电源 (SMPS) 应用中更高功率和更高密度的趋势。本节讨论并比较了与组装、热性能和电气寄生等主题相关的不同封装。

BSC 和 TSC 包的组装实现

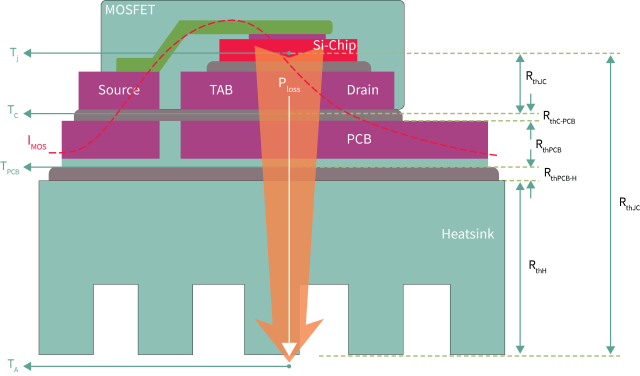

底部冷却

图 3 和图 4 显示了 BSC 和 TSC 的主要冷却概念。在这两种情况下,SMD 封装通常通过回流焊接工艺安装在 PCB 上。对于 BSC,主要热通量从封装底部的器件散热器(外露焊盘)通过 PCB 引导到安装在 PCB 另一侧的外部散热器。因此,在使用基于 FR4 的 PCB 时,需要在封装下方和穿过 PCB 的热通孔进行热传递。在 PCB 的背面,外部散热器安装在带有散热孔的区域。散热器和 PCB 通过热界面材料 (TIM) 进行电气隔离。很多时候,厚度在 100–500 μm 范围内的箔用作 TIM,在最好的情况下,它具有良好的热导纳 (λ)。理想情况下,这会导致低热阻抗(Zthja ) 用于整个系统。

图 3:使用底部冷却的示例解决方案

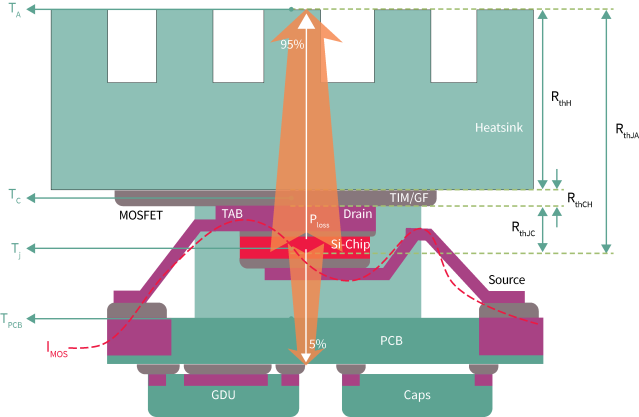

图 4:使用顶部冷却的示例解决方案

PCB 具有一定的厚度,受电路设计所需的铜层数量和热通孔密度限制的影响。因此,与器件散热器提供的热传递面积相比,通过 PCB 进行热传递的有效横截面积减小了。这是第一个瓶颈。第二个瓶颈是 TIM,其 λ 比器件散热器和外部散热器低得多。

在某些情况下,用绝缘金属基板 (IMS) 替换基于 FR4 的基板可以在不超过最大器件或 PCB 温度的情况下获得更高的热通量。特别是对于单层 PCB 设计,既不需要热通孔也不需要额外的 TIM。由于电路板的铝芯用作散热器,因此可以节省外部散热器。然而,虽然 Z thja降低了,但板上温度循环次数 (TCoB) 也减少了,特别是对于无铅 SMD 封装,如TO-leadless (TOLL)或 ThinPAK,由刚性基于 IMS 的 PCB 与更灵活的 PCB 相比引起基于 FR4 的 PCB。

顶部冷却

在 TSC 封装中,封装顶部的器件散热器通过 TIM 直接连接到外部散热器(图 4)。在这种情况下,没有热量通过 PCB 和热过孔,因此从总热阻抗中消除了它们的热阻抗。这导致增强的导热性和更高的封装最大功耗。

此外,TSC 封装的另一个优点是相对 PCB 侧的空闲区域可用于放置其他器件,例如栅极驱动器和无源元件,以及封装体正下方的信号路由空间。

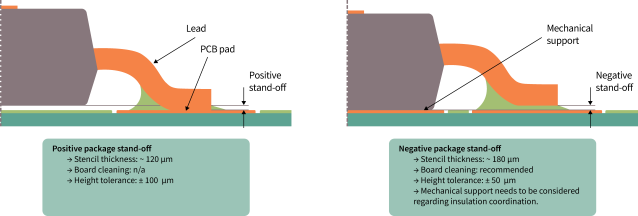

为获得良好的热界面,建议在 TSC 器件上用一定的力按压散热片。对于具有正封装支座的引线 SMD 封装(图 5,左),该力和其他温度循环引起的力被封装引线吸收,从而在 QDPAK 的情况下产生 2,000 次循环的非常好的TCoB。6

如果出现负封装间距(图 5,右图),PCB 设计需要考虑其他因素,以避免系统可靠性问题,这可能会导致系统设计和制造的额外工作量和复杂性。负封装支架具有降低 Z thja的优势,因为它降低了封装高度公差,从而导致更薄的 TIM 厚度。然而,当考虑 PCB 翘曲等其他容差时,特别是对于较大的 PCB 尺寸和使用公共散热器的多个功率器件,负封装支架的热优势变得不那么重要了。

图 5:标准正封装支架(左)和负封装支架(右)。封装体下方的铜焊盘有利于作为明确高度的机械支撑和在负支架情况下的高板级可靠性。2

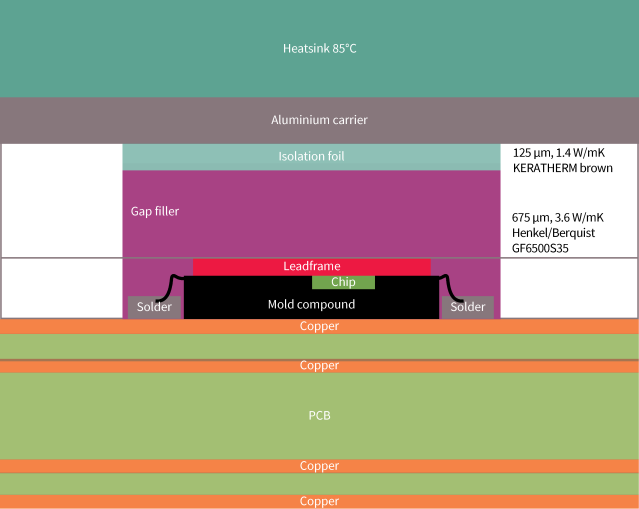

对于常见的散热器方法,图 6 示意性地显示了器件和散热器之间的 TIM 堆栈,在本示例中由绝缘箔和间隙填充物组成。间隙填充物用于补偿设备、散热器和 PCB 相关的制造公差。仅使用间隙填充物进行传热,必须确保设备和外部散热器之间的可靠绝缘。此外,间隙填充材料必须满足必要的击穿等级,并且需要防止在 PCB 组装过程中间隙填充内的封闭颗粒或气孔。一般来说,PCB 组装的清洁制造环境可以降低系统制造过程中因污染而导致系统故障的风险。

图 6:外部散热片和器件之间的电气隔离箔和填缝剂

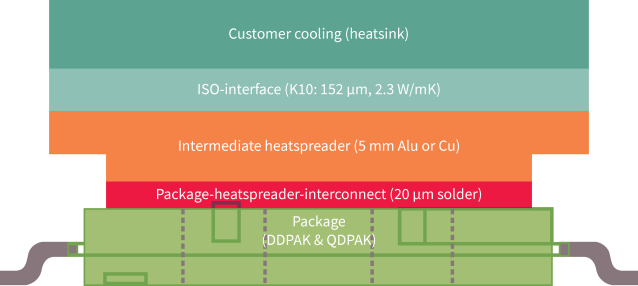

为了进一步提高 TSC 的 Z thja和动态功耗,中间散热器的实施是一个不错的选择,如图 7 所示。这个额外的散热器的热容量可以将额外的热量存储一段时间(几秒钟)并将其进一步转移到公共散热器和环境中。根据系统设计,为了改进系统 Z thja ,也可以移除公共散热器和 TIM ,其中散热器是主散热器并由风扇气流直接冷却。

图 7:单器件散热器安装6

热性能

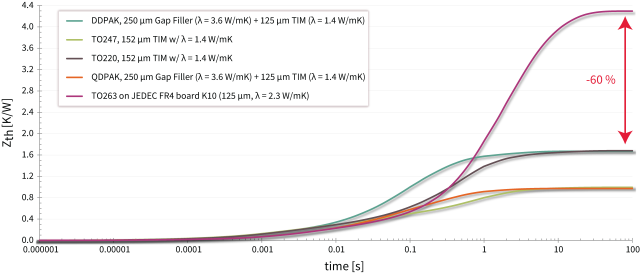

图 8 显示了考虑采用强制风冷的基于 FR4 的 PCB 设计的选定通孔器件 (THD)、BSC SMD 和 TSC SMD 封装的Z thja时间相关图。假设所有显示封装内的相同器件具有相同的功率损耗。将基于 FR4 的 PCB 上的 DDPAK(TSC 封装)与 TO263(BSC 封装)进行比较,DDPAK的 Z thja降低了 60% ,尽管这两种封装的有效冷却面积非常相似。DDPAK 绕过了瓶颈“热通孔”,如前一节所述。该图还表明,顶部封装可以实现与 THD 相当的 Z thja值。

图 8:强制对流下多个封装的典型瞬态热阻抗结环境 (Z thja )

图例表明,使用具有相当高 λ 的薄层隔离材料是实现良好 Z thja结果的关键。除此之外,使用具有更高 λ 的间隙填充物和隔离箔将导致所示的 TSC 封装提供比 THD 更低的Z thja的情况。

高频操作中的低电感寄生优势

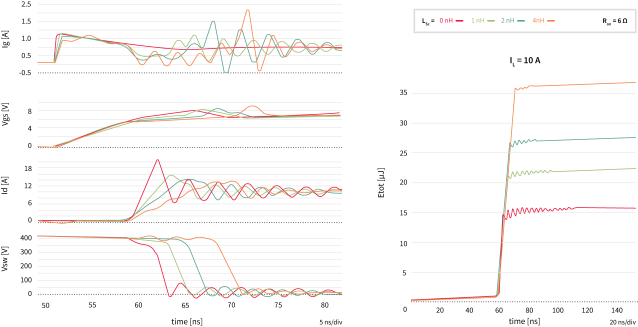

图 9 展示了封装源极电感 (L Sc ) 对开启瞬态的影响。L Sc从 0 增加到 4 nH。漏极电流 (di/dt) 的上升会导致 L Sc上的感应电压降,这会从栅极驱动电压中减去,从而降低栅极电流。因此电压瞬变需要更长的时间,并且损耗会增加。相同的机制但以相反的方式适用于关断瞬态。

图 9:封装源电感对开启的影响示例:波形细节(左)和损耗(右)

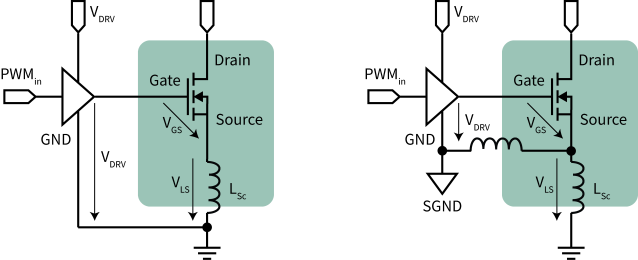

上面讨论的 L Sc的负面影响可以通过使用单独的源极检测引脚(Kelvin 源)来控制栅极(图 10,右)来消除,从而有效地降低开关损耗。通过使用源极检测连接来驱动栅极,L Sc位于栅极驱动环路之外。因此,它的感应电压峰值不会像标准配置(图 10,左)那样只有一个源极连接到MOSFET时会反馈到驱动电路中。

图 10:标准三端子封装(左)和采用开尔文源的四端子封装(右)的栅极驱动环路比较

值得一提的是,Kelvin 源封装解决了 L Sc对栅极驱动和开关速度的负面影响。然而,L Sc仍会增加总环路电感,这是导致快速开关应用(例如具有宽带隙 (WBG) 开关的服务器 SMPS)中振铃的关键参数。因此,即使使用开尔文源,封装 L Sc也最好是最低的。参考应用笔记中提供了更多详细信息。7

概括

本文讨论了功率半导体封装在满足服务器电源(特别是硅和 WBG 开关)的功率和密度要求方面的重要性。

简要介绍了服务器 SMPS 应用和趋势,然后讨论了 SMD 封装,涉及装配实施、热性能和高频操作中的低电感寄生优势。

表 1 总结了英飞凌在服务器 SMPS 中使用的 SMD 封装产品组合,并比较了它们的主要参数。

表 1:用于服务器应用的 SMD BSC 和 TSC 封装概述。为了评估封装电感,假设封装内具有类似 RDS(on) 的器件。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论