各位大神,我在给G030配置外部高速无源晶振之后,发现无法起振。电路图就跟其他的项目一样,很常规的一个配置。G030的datasheet里面也没说不能使用外部高速无源晶振啊,但是在使用Cube进行

2024-03-21 08:15:29

CXL(Compute Express Link)是一种业界支持的高速缓存一致性互连协议,用于处理器、内存扩展和加速器之间的通信。

2024-03-20 13:56:53 53

53

STM32H7系列,FMC接片外SDRAM,连续读写测试,每次读写间加一个延时不会报错,但去掉延时,连续读写就读写不一致了?

请教大神是哪里配置出了问题么?

另外还有个奇怪的现象。。。在循环的最后

2024-03-11 08:07:46

怎样使用Jlink (SEGGER) 通过SWD读写呢?Jlink没有找到CYPD6125的信号,官方也没有找到CYPD6125对应的FLM和xml 文件

2024-02-23 08:20:07

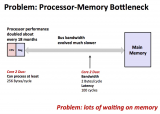

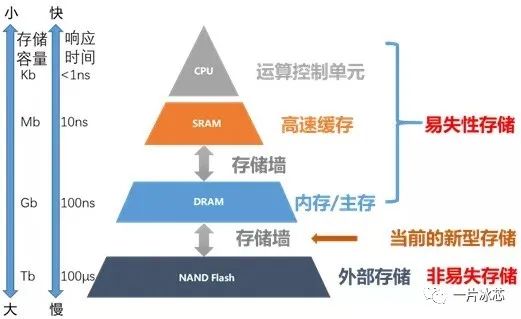

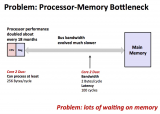

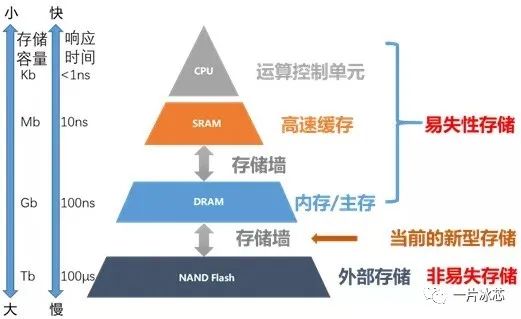

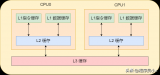

是为了解决CPU运算速度与内存(Memory)读写速度不匹配的矛盾而存在,是CPU与存储设备之间的临时存贮器,容量小,但是交换速度比内存快。内置高速缓存通常对CPU的性能

2024-01-26 10:00:26 181

181

高速缓存(Cache)主要是为了解决CPU运算速度与内存(Memory)读写速度不匹配的矛盾而存在, 是CPU与存储设备之间的临时存贮器,容量小,但是交换速度比内存快。内置高速缓存通常对CPU的性能提升具有较大作用。

2024-01-22 16:07:33 489

489

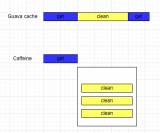

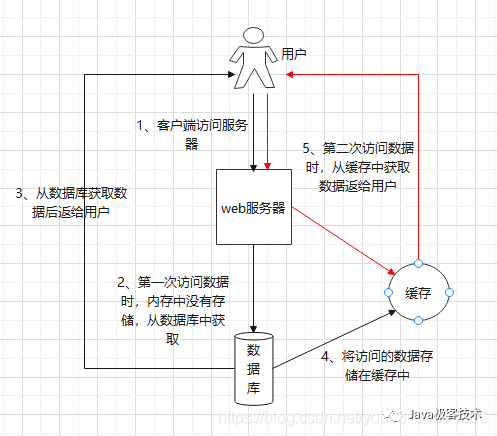

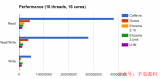

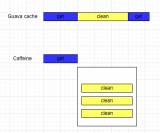

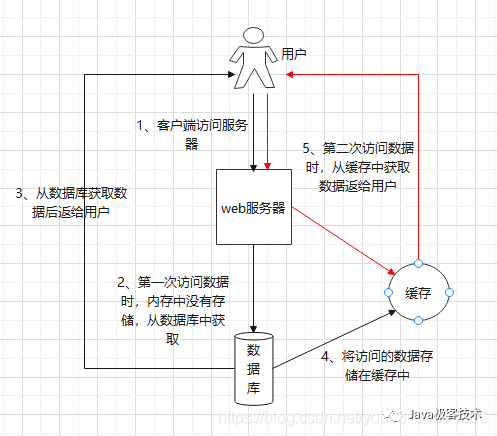

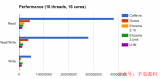

小编最近在使用系统的时候,发现尽管应用已经使用了 redis 缓存提高查询效率,但是仍然有进一步优化的空间,于是想到了比分布式缓存性能更好的本地缓存,因此对领域内常用的本地缓存进行了一番调研,有早期

2024-01-18 11:19:07 478

478

结合5nm和6nm工艺节点,采用先进的小芯片(Chiplets)设计,全新的计算单元和第二代AMD高速缓存威廉希尔官方网站

,相比AMD RDNA 2架构的每瓦性能提高54%;

2024-01-04 16:27:36 509

509

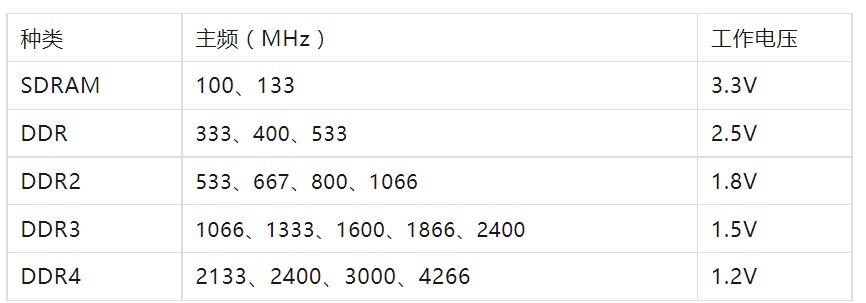

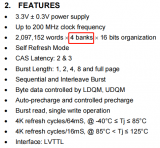

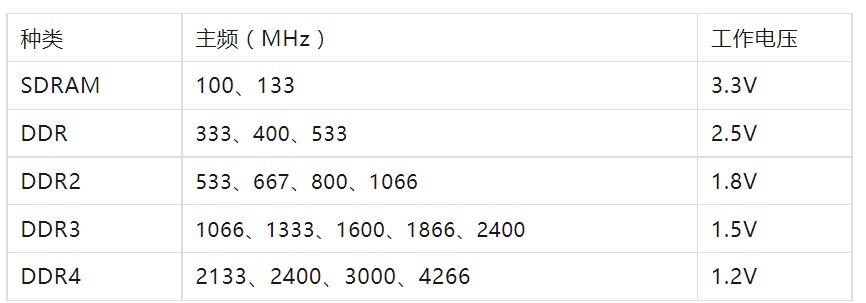

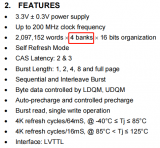

。 SDRAM是一种集成电路存储器,可以通过同步钟信号进行数据读写。与传统的静态随机存储器(SRAM)相比,SDRAM具有更高的存储密度和更低的成本。扩展SDRAM接口使得微控制器能够使用外部

2024-01-04 14:09:23 339

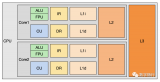

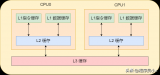

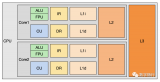

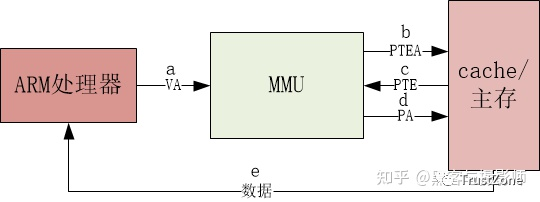

339 CPU的核心功能包括数据运算和指令控制。CPU运算的数据和执行的指令全部存储在CPU的寄存器中,这些数据和指令又都来自于CPU高速缓存。

2024-01-02 16:01:48 662

662

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 缓存预热就是系统上线后,提前将相关的缓存数据直接加载到缓存系统。

2023-12-25 09:41:02 250

250

靠近 CPU 的小、快速的高速缓存存储器(cache memory)做为一部分存储在相对慢速的主存储器(main memory)中数据和指令的缓冲区域。

2023-12-25 09:21:50 242

242

笔者与SDRAM有段不短的孽缘,它作为冤魂日夜不断纠缠笔者。笔者尝试过许多方法将其退散,不过屡试屡败的笔者,最终心情像橘子一样橙。

2023-12-15 09:09:03 634

634

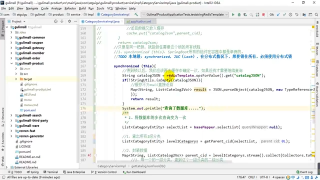

MyBatis是一种轻量级的持久化框架,它提供了一级缓存和二级缓存的机制来优化数据库操作性能。一级缓存是默认开启的,而二级缓存需要手动配置启用。 一、一级缓存 1.1 缓存生命周期 一级缓存存在于

2023-12-03 11:55:11 438

438 基本流程就是客户端A请求,先去删除缓存,然后将数据写入数据库,此时客户端B查询先去查询缓存,缓存没有返回,去查数据库,此时还没有完成主从同步,拿到是从库的旧数据,然后将旧数据进行缓存,在客户端A完成主从同步后,再次删除缓存,这时数据才是一致的,但是重点就是在休眠的几秒钟,会造成数据的不一致性;

2023-12-02 14:23:53 601

601

在设计周期中,您可保留多个版本的工程,这些工程使用相同的 IP 和相同的配置。重新运行整个工程会导致每次都要重新生成 IP,很费时间。

2023-12-01 09:14:14 295

295

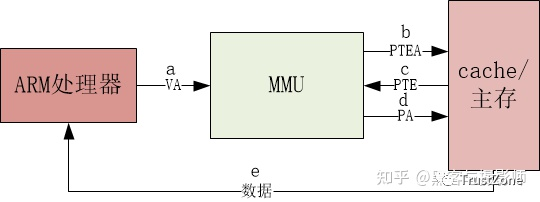

。 • d) MMU通过PTE映射物理地址,并把它传给高速缓存或主存。 • e) 高速缓存或主存返回物理地址对应的数据给处理器。 (2)缺页 • a) 处理器要对虚拟地址VA进行访问。 • b) MMU

2023-11-26 16:19:27 364

364

采用OV7670带缓存摄像头模块,用MM32F103能做简单的视频处理吗,比如判断颜色和形状,可以使用外部sdram

2023-11-08 06:27:16

SRAM是目前最成熟的易失性高速存储器,通常由6管(6T)实现数据的读写,可以用做CPU和内存(DRAM)之间的高速缓存。

2023-10-31 17:46:55 1259

1259

中存放一个副本,当该内容下次被访问时,不必连接到驻留网站,而是由Cache中保留的副本提供。 在企业Web应用中,通过缓存威廉希尔官方网站

能够提高请求的响应速度;减少系统IO开销;降低系统数据读写压力... 缓存的意义 首先我们要知道,在我们开发过程中,为什么要使用缓存,缓存能

2023-10-08 14:07:17 300

300 一、摘要 说到缓存,面试官基本上会绕不开以下几个话题! 项目中哪些地方用到了缓存?为什么要使用缓存?怎么使用它的?引入缓存后会带来哪些问题? 这些问题,基本上是互联网公司面试时必问的一些问题,如果

2023-09-30 15:29:00 338

338

电子发烧友网站提供《管理基于Cortex-M7的MCU的高速缓存一致性.pdf》资料免费下载

2023-09-25 10:11:48 0

0 在设计周期中,您可保留多个版本的工程,这些工程使用相同的 IP 和相同的配置。重新运行整个工程会导致每次都要重新生成 IP,很费时间。

2023-09-22 09:39:33 435

435

只是读写检测,没有硬件sdram接口的f103可以测试吗

2023-09-21 06:38:25

电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7(SAM S70/E70/V70/V71)MCU上创建不可高速缓存的存储区.pdf》资料免费下载

2023-09-20 11:50:46 0

0 电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7 MCU上在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-20 11:40:24 0

0 电子发烧友网站提供《使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-19 16:28:10 0

0 AMD锐龙7000系列处理器工作超5 GHz,具备至高16核心32线程和最大可达80MB的高速缓存,卓越性能让工作、游戏、设计、渲染更疾速。

2023-09-18 12:33:10 903

903 STM32MP151A/D器件基于高性能ARM®Cortex®-A7 32位RISC内核,运行频率高达800 MHz。

Cortex-A7处理器包括一个32K字节的一级指令高速缓存、一个32K字节

2023-09-13 07:23:32

片上闪存特性和系统框图

存储空间组织架构

用户闪存

系统闪存

OTP

选项字节

闪存读接口

等待周期

指令预取

指令高速缓存

数据高速缓存

擦除和编程操作

读保护和写保护

STM32F2和STM32F1的闪存特性比较

2023-09-13 07:10:38

闪存。

主32位AHB5多层总线矩阵,位于中央图中的11个主设备和10个从设备互连。

128位AHB5指令高速缓存再填充总线矩阵为由两个128位接口和两个32位接口组成接口。

128位接口是连接到的从0端口到闪存的指令缓存和主0端口存储器接口或FLITF。

2023-09-08 06:48:06

什么是高速缓存?• 高速存储器块,包含地址信息(通常称作TAG)和相关联的数据。• 目的是提高对存储器的平均访问速度• 高速缓存的应用基于下面两个程序的局部性 :• 空间局部性:如果一个存储器的位置

2023-09-07 08:22:51

下表中列出的 STM32 微控制器(MCU)中。这些缓存使用户从内部和外部存储器提取指令和数据时或在用于外部存储器的数据流量时提高应用性能并降低功耗。本文档提供了典型示例,以强调 ICACHE 和 DCACHE 功能,并便于配置。

2023-09-07 07:51:27

1.具有双发布功能的高性能6级流水线(每个时钟周期最多执行两条指令)。

2.作为系统总线的64位AXI总线接口。

3.可选的指令高速缓存(4至64KB)和数据高速缓存(4至64KB),每个高速

2023-09-04 06:28:56

每当一个核通过MVA操作对另一个核执行广播无效指令高速缓存时,例如,当将可执行代码从闪存复制到存储器时,其他核每次都刷新并重新启动它们的预取单元,而不进行任何处理。

由于该错误,其他核心可能停止它们的执行,直到不再发生剩余的广播操作。

2023-09-01 09:16:59

®v8.3-A扩展中引入的加载获取(LDAPR)指令·ARM®v8.4-A扩展中引入的Dot产品支持说明。

·EL1和EL0高速缓存控制的陷阱、支持Spectre变体4软件缓解的PSTATE SSB

2023-08-29 08:05:54

受影响的ARM CPU上,建议的缓解措施包括在转换到需要保护以前的执行上下文的执行上下文时,使部分或全部分支预测器缓存失效。

有关术语执行上下文的定义,请参见第1.2节。

CVE-2018-3639,也

2023-08-25 07:36:27

)的原理,与微程序复杂指令集计算机(CISC)相比,指令集和相关的解码机制得到了极大的简化。

片上混合数据和指令高速缓存与写缓冲区一起,大大提高了平均执行速度,并减少了处理器所需的平均内存带宽。

这允许外部存储器以最小的性能损失支持额外的处理器或直接存储器访问(DMA)通道

2023-08-24 07:16:02

电子发烧友网站提供《MySQL服务器优化LSI MegaRAID CacheCade Pro 2.0读写缓存软件和固态硬盘(SSD).pdf》资料免费下载

2023-08-21 14:19:00 0

0 CPU高速缓存集成于CPU的内部,其是CPU可以高效运行的成分之一,本文围绕下面三个话题来讲解CPU缓存的作用

2023-08-21 12:17:35 797

797

Cortex-A7 MPCore处理器是一款实现ARMv7-A架构的高性能、低功耗处理器。

Cortex-A7 MPCore处理器在带有一级高速缓存子系统、可选集成GIC和可选二级高速缓存控制器的单个多处理器设备中具有一到四个处理器

2023-08-18 07:25:18

吞吐量的Thumb-2威廉希尔官方网站

。

该流水线具有双重算术逻辑单元(ALU),具有双重指令发布,以有效地利用其他资源,例如寄存器堆。

该处理器在具有最多两个处理器的群集中具有1级(L1)数据高速缓存一致性

2023-08-18 06:34:29

(SB)、所有内核以及内核之间共享的逻辑。

共享逻辑包括CPU桥(CPU侧)(CBC)、L2高速缓存,以及维护核心中的高速缓存与L2高速缓存和低延迟RAM(LLRAM)存储器之间的一致性的一致性逻辑

2023-08-17 08:02:29

Cortex-A8处理器是一款高性能、低功耗、高速缓存的应用程序处理器,可提供完整的虚拟内存功能。

该处理器的功能包括:

·完全实现ARM体系结构v7-A指令集·具有高级可扩展接口(AXI)的可配

2023-08-17 07:43:12

Cortex-A5处理器是一款高性能、低功耗的ARM宏单元,具有提供完整虚拟内存功能的一级高速缓存子系统。

Cortex-A5处理器实现了ARMv7架构,并在Jazelle状态下运行32位ARM指令、16位和32位Thumb指令以及8位JAVA™字节码

2023-08-17 07:16:41

Cortex-A17 MPCore处理器是一款高性能、低功耗的处理器,采用ARMv7架构。

Cortex-A17 MPCore处理器在带有L1和L2高速缓存子系统的单个多处理器设备中具有一到四个处理器。

2023-08-17 07:06:31

Cortex-A9处理器是一款高性能、低功耗的ARM宏单元,具有提供完整虚拟内存功能的一级高速缓存子系统。

Cortex-A9处理器实现ARMv7-A架构,并在Jazelle状态下运行32位ARM

2023-08-17 06:53:00

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有四个Cortex-A32处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A32处理器支持

2023-08-16 06:54:59

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有四个Cortex-A35处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A35处理器支持

2023-08-12 07:39:00

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有八个处理器可用,该监听控制单元维护L1、L2和L3数据高速缓存一致性。

本节提供周期模型与硬件的功能比较的摘要,以及周期模型的性能和准确性

2023-08-12 07:30:35

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存关联群集中最多有四个Cortex-A53处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A53多处理器支持

2023-08-12 06:44:40

的电源、性能和面积(PPA)目标和其他关键要求。

RD-V2提供以下功能:

·32个MP1 ARMv9.0-A ARM®Neoverse™V2内核,支持直接连接和2MB专用,

每个核心的专用二级高速缓存

2023-08-11 07:54:59

如果中断被识别为CPU的最高优先级启用中断之一,并被发送到目标高速缓存,则存在一个单周期窗口,在该窗口中,如果重新编程该中断,则记录召回要求,但直到下一个外部触发时才执行。

触发器可以是以下任一项:

激活、释放或停用任何SPI。

任何SPI信号上的状态改变。

寄存器编程或CPU组启用更改。

2023-08-11 07:15:45

SDRAM全称Synchronous Dynamic RAM,同步动态随机存储器。首先,它是RAM,即随机存储器的一种。

2023-08-08 15:10:46 896

896

附件工程测试在main 循环中使用FMC读写外部内存时,TIM1中断响应时间出现不同程度延迟。

TIM1在CNT溢出时触发update中断,设置为最高优先级中断,在中断中读取TIM1-&

2023-08-05 07:15:56

消息支持,以管理分布式内存管理单元(MMU),例如CoreLink MMU-400。这些可以通信通过具有多达三个ACE Lite从机的CCI-400。

硬件管理的一致性可以通过以下方式提高系统性能并降低系统功耗共享片上数据。管理一致性有以下好处:

•减少外部存储器访问。

•减少软件开销。

2023-08-02 17:33:01

:

•用于增强操作系统安全性的TrustZone架构•专为高性能系统设计的主、从和外围AXI/AMBA接口•智能能源管理器(IEM)支持。

高速缓存控制器是一个统一的、物理寻址的、物理标记的8路高速缓存。您可

2023-08-02 15:09:49

当中央处理器(CPU)产生大量内存流量时,添加片上二级缓存(也称为二级缓存,L2CC)是提高计算机系统性能的公认方法。根据定义,二级缓存假定存在与CPU紧密耦合或内部的一级缓存或主缓存。

2023-08-02 13:11:45

系列兼容的软件。

片上混合的数据和指令高速缓存以及写入缓冲器大大提高了平均执行速度,并减少了处理器所需的平均内存带宽。这允许外部内存支持额外的处理器或直接内存访问(DMA)通道,同时将性能损失降至最低

2023-08-02 11:36:56

CCN-502是基于AMBA 5 CHI架构的可扩展相干互连。它设计用于高端网络和企业计算系统。

CCN-502将互连和一致性功能组合到单个模块中。它提供以下外部接口:

•四个完全一致的CHI端口

2023-08-02 10:38:59

的EPOC-32。ARM1020T由ARM10TDMI整数单元、数据和指令高速缓存、内存管理单元以及写缓冲区组成。

ARM1020T包括:

•带集成嵌入式ICE逻辑的ARM10TDMI整数单元

•外部协处理器

2023-08-02 08:33:42

MBIST是测试嵌入式存储器的行业标准方法。MBIST通过根据测试算法执行对存储器的读取和写入序列来工作。存在许多行业标准的测试算法。MBIST控制器生成正确的读取和写入序列。ARM L210 MBIST控制器用于与ARM L210一起执行二级高速缓存RAM的内存测试。

2023-08-02 08:07:10

电子发烧友网站提供《STM32F7威廉希尔官方网站

--高速缓存.pdf》资料免费下载

2023-08-01 15:18:55 0

0 工业产线涉及到原件到装配组件完成的一系列流程,传统的人工记难以对生产制造中的流程进行跟踪管理,借助工业RFID设备,可以实现产品的生产流程追溯,保证产品生产质量。下面我们就来举几个RFID读写

2023-07-31 14:55:08 244

244 ,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32590集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指

2023-07-14 14:33:26

构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32591集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令

2023-07-14 14:09:44

缓存服务器是什么?缓存服务器是专用网络服务器或充当在本地保存网页或其他互联网内容的服务器的服务。通过将以前请求的信息放入临时存储(或高速缓存)中,高速缓存服务器既可以加快数据访问速度,又可以减少

2023-07-07 17:48:59 353

353 向DSA慢慢靠拢;异构计算的核心之一是互连,传统的PCIe总线缺乏缓存一致性机制,导致内存性能低下,延迟低于可接受水平,因此出现了CCIX和CXL等协议,这些协议基于PCIe又高于PCIe,在继承PCIe兼容性的基础上,又提供了缓存一致性支持。在今年的

2023-06-29 09:56:59 519

519

SPI Flash为Slave (从设备),可将应用程序放在外部内存SPI Flash,要执行放在外部SPI Flash的程序时,硬件会透过SPI Flash控制单元将应用程序读取至新唐专为M480 SPI Flash 设计的32KB高速缓存执行应用程序。

2023-06-15 07:11:48

缓存是计算机科学中的一个重要概念。设想某个组件需要访问外部资源,它向外部源请求资源,接收并使用资源,这些步骤都需要花费时间。

2023-06-12 09:50:59 369

369

本地缓存 :应用中的缓存组件,缓存组件和应用在同一进程中,缓存的读写非常快,没有网络开销。但各应用或集群的各节点都需要维护自己的单独缓存,无法共享缓存。

2023-06-11 15:12:21 556

556

缓存(Cache)在代码世界中无处不在。从底层的CPU多级缓存,到客户端的页面缓存,处处都存在着缓存的身影。缓存从本质上来说,是一种空间换时间的手段,通过对数据进行一定的空间安排,使得下次进行数据访问时起到加速的效果。

2023-05-22 11:01:14 637

637

使用 TI SysBIOS,您可以在其中将高速缓存的一部分定义为具有特殊地址的快速 RAM。然后固件可以考虑将代码或变量放在那里,从而大大加快算法的速度。

我不知道 i.MX8mm 是否一般提供,我也不知道如何在构建嵌入式 Linux 时配置它。

2023-05-18 11:48:08

我想将 i.MX RT1024 与外部 64MB SDRAM 一起使用。根据数据表,它支持 8/16 位 SDRAM 外部存储器接口。从性能的角度来看,哪种模式更好?如何?如果有任何链接/参考可以通过此详细信息,请告诉我。谢谢

2023-05-05 11:17:30

我们想在我们的一个物联网应用项目中使用 MIMXRT1176DVMAA。为此,我们不需要外部 SDRAM。所以,我们想在没有 SDRAM 的情况下运行这个控制器。

根据数据表,该控制器具有内部 2MB SDRAM,因此我们要使用它。

你能证实这一点吗?

2023-05-04 08:12:41

今天给大家介绍一下如何在SpringBoot中解决Redis的缓存穿透、缓存击穿、缓存雪崩的问题。

2023-04-28 11:35:19 495

495 本公司目前MCU系列,到目前为止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已经把SDRAM合封入芯片,合封的SDRAM大小根据芯片型号不同,具体见官方手册。

2023-04-28 09:30:22 1496

1496

/misc_spifi_tst,在运行到spifi_comde_dst,在运行();就会出现总线异常进入而崩溃,如果程序在RAM中启动运行就不会出现总线异常,想请教下怎样才能在flash启动后,又能成功读写flash

2023-04-27 06:04:06

CPU主要包括运算器(ALU, Arithmetic and Logic Unit)和控制单元(CU, Control Unit),除此之外还包括若干寄存器、高速缓存器和它们之间通讯的数据、控制及状态的总线。

2023-04-24 16:23:53 2821

2821 有一个带有 SDRAM 的相同系统,并且相同的应用程序按预期运行,我可以将不可缓存的区域放在 SDRAM 的末尾,并且一切正常。将非缓存数据放在 HyperRAM 中有什么问题吗(或者我在打别的东西)?

2023-04-17 07:04:11

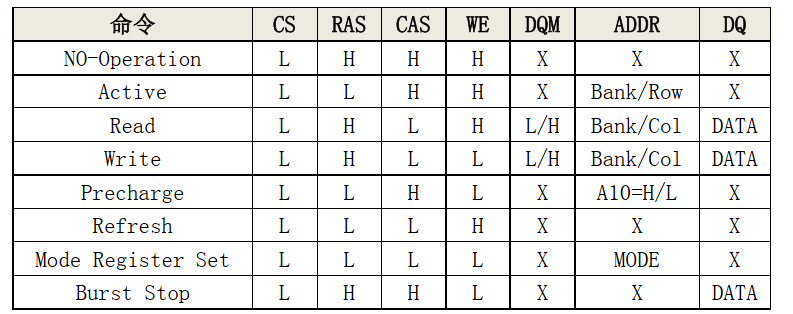

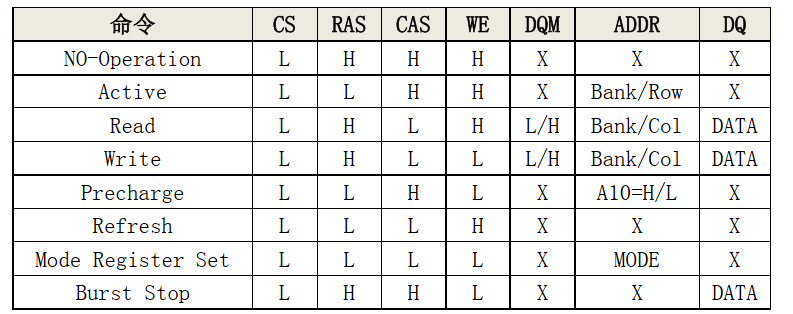

SDRAM的驱动需要用到一些命令,介绍几个常见的命令。

2023-04-04 17:13:19 1814

1814

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

信号,双 RISC-V 内核-32KB 高速缓存 (I/D Cache) 和双核共高达 512KB的零等待指令和数据本地存储器 (ILM / DLM),加上256KB 通用 SRAM,极大避免了低速

2023-04-03 14:32:24

和全局数据移动到 SDRAM。作为一个已知问题, 当我们将堆放在缓存内存(如 OCRAM 或 SDRAM)上时,许多中间件无法正常运行。但是通过使用宏

2023-03-31 08:36:41

SDRAM SLICE CARD

2023-03-30 12:05:53

高速DAP仿真器 BURNER

2023-03-28 13:06:20

工程代码可以登录叁芯智能科技官方威廉希尔官方网站

论坛下载。 在一些工程设计中,SDR SDRAM作为中间数据缓存器,往往需要接收上游传输过来的数据,并且还要输出下游所需的数据。为了能够解决下上游传输数据的需要

2023-03-27 17:09:14

C语言用格式化的方式读写文件**

对文件进行格式化输入输出时,要用fprintf函数和fscanf函数,作用与printf函数和scanf函数相仿,都是格式化读写函数。

2023-03-24 15:24:22 601

601 ;

else

sdr_addr <= 0;

end

endmodule

sdr_write设计实现

该模块负责将外部的数据写入到规定的地址中去。在SDR SDRAM中,每操作(读写)一次,都会

2023-03-23 17:40:58

电子发烧友App

电子发烧友App

评论