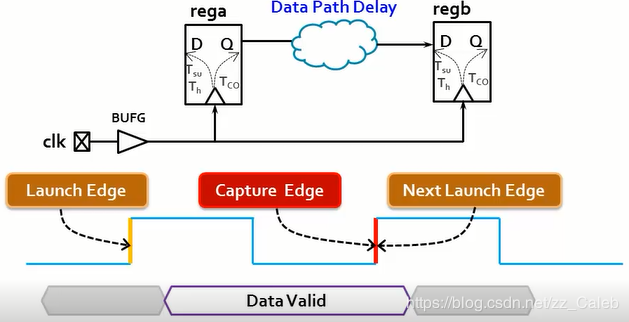

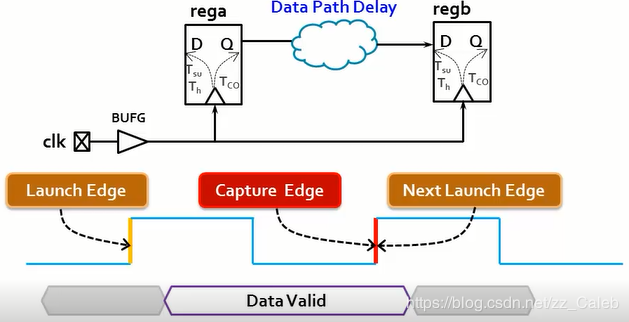

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2767

2767

边沿。 ④ 通常情况下这两个边沿会有一个时钟周期的差别。 2、时序路径 (Timing path典型时序路径有四种) ① ② 第一类时序路径(红色) - 从device A的时钟到FPGA的第一

2020-11-25 15:27:21 8566

8566

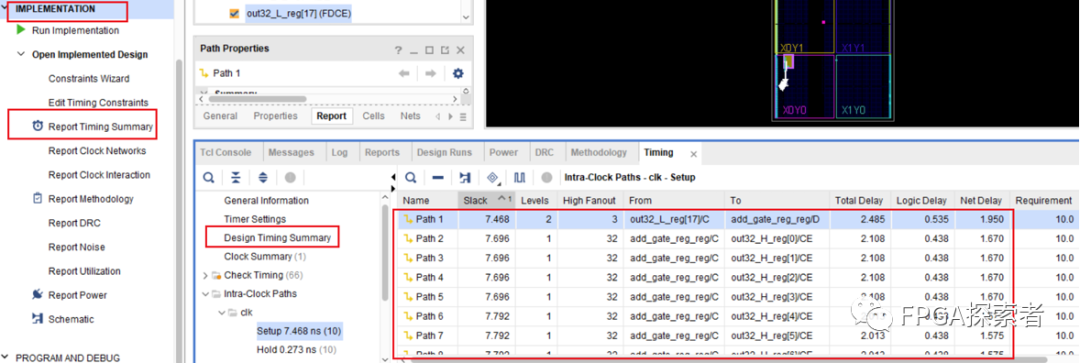

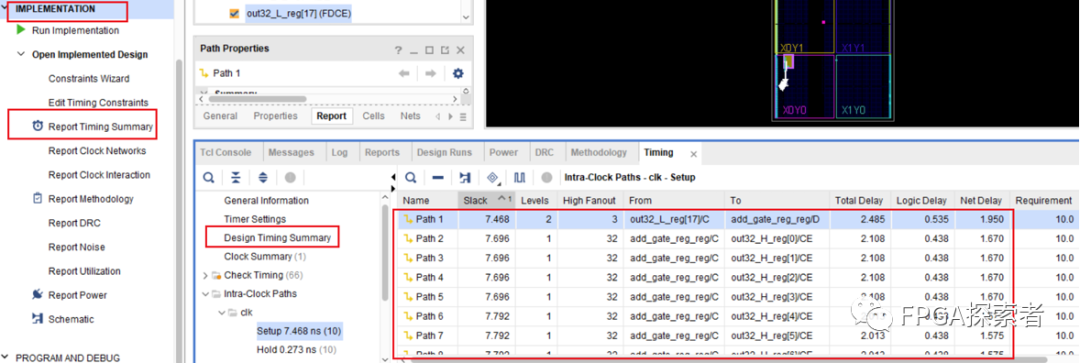

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 OFFSET语句:OFFSET说明了外部时钟和与其相关的输入,输出数据引脚之间的时序关系。

2020-11-25 14:23:43 2968

2968

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。

2023-06-21 14:14:16 1220

1220

reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的路径。

2023-06-26 14:28:01 604

604

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。

2023-08-03 09:27:25 915

915

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

分析。(但硬件路径不变还是存在跨时钟域问题) set_clock_groups -name async _clk0_clk1 -asynchronous-group{clk0 clk0_0

2018-09-21 12:40:56

某些特定的情况下,比如异步时钟域时,我们清楚地知道某些寄存器会发生建立时间或者保持时间不满足的情况,但这是不可避免的,设计者也已经对其进行了处理。在这种情况下,设计者最好告诉EDA软件忽略这些路径,否则EDA软件会努力尝试解决这些路径的时序冲突,既费时又没有效果。

2020-08-16 07:25:02

文章目录前言时钟及时钟域时钟,时序逻辑的心跳时钟信...

2021-07-29 07:43:44

bq1_dat稳定在1,bq2_dat也输出稳定的1。最后,从特权同学的经验和实践的角度聊一下。跨时钟域的信号同步到底需要1级还是2级,完全取决于具体的应用。如果设计中这类跨时钟域信号特别多,增加1级

2020-08-20 11:32:06

解释了什么时候要用到FALSE PATH: 1.从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。 2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域

2018-07-03 11:59:59

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

2015-01-04 15:17:16

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

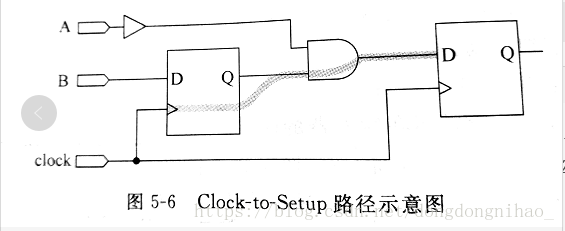

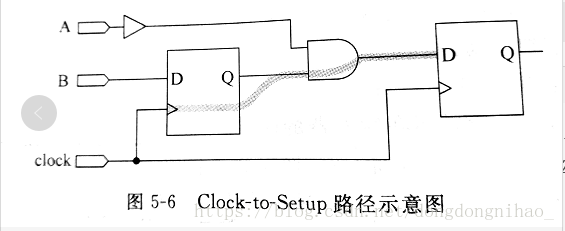

FPGA时序分析与约束(2)——与门电路代码对应电路模型的时序分本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:InterQuartesⅡ时序分析中常见的时间参数:Tclk1:时钟从时钟

2021-07-26 08:00:03

和时钟偏差组成的。

二、时序路径

时序路径是指从FPGA输入到输出的所有逻辑路径组成的路径。当存在时序路径时,需要考虑时序约束以确保正确的逻辑功能和时序性能。

时序路径中的关键元素包括:

(1) 路径

2023-11-15 17:41:10

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-03-04 09:22:51

,他们共用一个时钟(当然也有不共用一个时钟的reg2reg路径,这种路径的分析会复杂一些,这里不做深入讨论)。对于reg2reg路径,我们只要告诉FPGA的时序设计工具他们的时钟频率(或时钟周期),那么

2015-07-20 14:52:19

;所谓时钟路径,则是指时钟从源端到达各个寄存器输入端的路径。(特权同学,版权所有)图8.18 reg2reg的数据路径和时钟路径如图8.19所示,为了便于后续的时序余量分析和计算,我们提出了data

2015-07-24 12:03:37

的路径分析,则一般都需要用户指定一个符合相关时钟要求的虚拟时钟,这个虚拟时钟就作为pin端的时钟来分析时序,我们这里所约束的虚拟时钟对应的路径如图8.29所示。(特权同学,版权所有)图8.29 虚拟时钟路径

2015-07-30 22:07:42

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

edge、Tsu、Th、Tco概念1.launch edge 时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。2.latch edge 时序分析终点

2012-01-11 11:43:06

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理威廉希尔官方网站

是IC设计中非常重要的一个

2022-06-24 16:54:26

仪的特色之一,但MDO4000 绝不是以上罗列的五种测试工具的简单组合,这五种功能工作在同一时钟、同一触发机制下,使得MDO4000 具有创新的时域、频域、调制域时间相关的跨域分析功能。为此,我们将

2019-07-19 07:02:07

在于它推出了创新的概念-跨域分析,利用跨域分析,可以发现传统手段无法发现的嵌入式射频系统以及数字射频系统的疑难杂症。MDO4000 系列混合域分析仪究竟是什么?我们可以将其基本功能总结如下:- 四通

2019-07-19 06:43:08

Non-Project模式下使用OOC / 542.4 综合后的设计分析 / 542.4.1 时钟网络分析 / 542.4.2 跨时钟域路径分析 / 562.4.3 时序分析 / 602.4.4 资源利用率分析

2020-10-21 18:24:48

命令是设定了从时钟域 clkA到时钟域 clkB 的所有路径都为false path。第二条命令设定了从 regA 到 regB 的路径为 false path。这两种路径在做时序分析时都会被忽略

2012-03-05 15:02:22

如何克服ajax跨域

2020-04-30 13:25:07

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

能够有一些时序问题,我们再通过时序分析的方法对它进行优化。我们这里把原本的100M时钟改成了200M时钟,具体步骤如下: 一:更改时钟之后进行综合,并打开timing analysis 二:通过

2018-08-22 11:45:54

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-27 06:34:40

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-27 00:00:41

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-26 23:54:23

任务第4部分:数据总线道口顺便说一句,学习约metastablity(或为什么这么多的辛勤工作是需要跨时钟域),检查下面的链接 完整资料:[hide][/hide]

2012-03-19 15:16:20

时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出。对于使用异步双口RAM来处理多bit数据的跨时钟域,相信大家还是可以理解的。当然,在能使用异步双口RAM来处理跨

2021-01-08 16:55:23

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-02-21 07:00:00

高速到低速上图给定的条件:高速时钟到低速时钟两个时钟有2ns的offset源端时钟是目的端时钟频率两倍如果不使用多周期约束,quartus II的时序分析工具将按照数据建立时间setup time

2015-03-17 17:43:52

异步bus交互(一)— 两级DFF同步器跨时钟域处理 & 亚稳态处理1.问题产生现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率

2022-02-17 06:34:09

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

其他总结:get_registers 对应多周期约束;get_ports 对应时钟约束get_nets 对应IO约束get_clocks 对应跨时钟约束做时序约束还是要多参考官方文档,多做一些官方

2016-09-13 21:58:50

关于cdc跨时钟域处理的知识点,不看肯定后悔

2021-06-21 07:44:12

关于iFrame特性总计和iFrame跨域解决办法

2020-05-15 14:26:43

通常不是问题,因为快时钟域将对慢时钟域的控制信号进行一次或多次采样。在异步时钟域之间传递一个控制信号时,简单的双触发器同步器通常就足够了。但是如果将控制信号从较快的时钟域传递到较慢的时钟域时,可能会

2022-04-11 17:06:57

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

相当大的设计,需要大约一个半小时才能构建。我发现OOC模块占用了大约三分之一的时间,并且想知道是否有办法从合成中排除未修改的IP块。我尝试使用以下TCL命令从综合中排除这些:set_property

2020-04-29 07:43:42

逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等

2018-04-03 11:19:08

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

如果目标设置为 ESP32-S3,是否可以仅为 ESP32 添加组件“foo”并将其从要求中排除?还包括和排除源文件?代码:全选#if CONFIG_IDF_TARGET_ESP32file

2023-03-02 07:36:58

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-10-20 09:27:37

本帖最后由 iioloii 于 2022-4-24 10:44 编辑

分析A、B两个信号(由同一个时钟驱动)之间的时序时发现源时钟和目的时钟经过相同的元件或走线的延时是不一样的,不知道为甚会是

2022-04-24 10:32:49

逻辑出身的农民工兄弟在面试时总难以避免“跨时钟域”的拷问,在诸多跨时钟域的方法里,握手是一种常见的方式,而Stream作为一种天然的握手信号,不妨看看它里面是如做跨时钟域的握手

2022-07-07 17:25:02

如今,SoCs正变得越来越复杂,数据经常从一个时钟域传输到另一个时钟域。上图信号A由C1时钟域触发,被C2时钟域采样。根据这两个时钟之间的关系,在将数据从源时钟传输到目标时钟时,可能会出现不同类

2022-06-23 15:34:45

域异步时钟域自动相关同步时钟域(DLL,DCM,PLL,MMCM)因为它是自动的,从字面意思上看就是自动分析。当我们例化了一个DCM,DCM的输入输出信号之间的关系就已近确定了,譬如频率关系和相位关系

2019-07-09 09:14:48

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

40Nginx的反向代理功能解决跨域问题

2019-10-10 10:58:03

周期约束,至于为什么,上面已经说过了,这里直接来做 我们设置延时周期数为2,即在第二个时钟周期进行数据锁存,因为是输入路径时序违规,所以我们约束的多周期路径就是从我们的虚拟时钟,也就是SDRAM的工作

2015-03-31 10:35:18

给我们的FPGA做内部时钟,在输出到外部做SDRAM的工作时钟,所以上图中,晶振到外部器件的时钟路径,应该是PLL的输出到SDRAM的输出路径还有,我们之前做的静态时序分析,是基于在FPGA内部的,所以数据

2015-03-31 10:20:00

不会通过多路复用器传播。因此最后的时序分析报告中也就没有使用时钟PLLdiv8分析任何时序路径)Breaking Timing Arcs in Cells每个单元都有从其输入到输出的时序弧,并且时序路径

2023-04-20 16:17:54

特定的方式下根据指定的要求才能进行跨时钟域的时序分析。

4、通常来说,如果没有很好地理解,跨时钟域故障难以探测且难以调试。所以所有跨时钟域接口都必须要在任何功能实现之前被很好地定义和处理。

让我们首先

2023-06-02 14:26:23

正确收发数据,从而使系统不能正常工作。随着系统时钟频率的不断提高和信号边沿不断变陡,系统对时序有更高的要求,一方面留给数据传输的有效读写窗口越来越小,另一方面,传输延时要考虑的因素增多,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。

2012-08-02 22:26:06

静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 使用时钟PLL的源同步系统时序分析一)回顾源同步时序计算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 基于时序路径的FPGA时序分析威廉希尔官方网站

研究_周珊

2017-01-03 17:41:58 2

2 我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC

2017-11-18 04:04:24 5809

5809

PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端口,路径的终点是时序单元的输入引脚或是设计的输出端口。根据起点和终点

2018-06-22 14:40:00 6645

6645

时序分析的主要对象是:在REG2中,时钟信号CLK经过路径③的有效沿,与从REG1寄存器输出的数据经过路径①到达REG2的D端时的关系。

2019-11-22 07:08:00 1644

1644 时序分析的主要对象是:在REG2中,时钟信号CLK经过路径③的有效沿,与从REG1寄存器输出的数据经过路径①到达REG2的D端时的关系。

2019-11-22 07:10:00 1804

1804 静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37:00 2460

2460

其中前三类路径是和内部寄存器reg和时钟CLK有关的,因此还需关注内部数据信号与时钟锁存沿的建立时间和保存时间(具体见时序分析一),而最后一类信号的传输通常不经过时钟,因此它的约束也相对简单

2021-01-08 16:47:00 13

13 方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

2022-05-04 17:13:00 1827

1827 在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25:06 425

425

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30:43 247

247

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

2023-08-08 10:31:44 525

525

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312

电子发烧友App

电子发烧友App

评论