时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 6343

6343

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

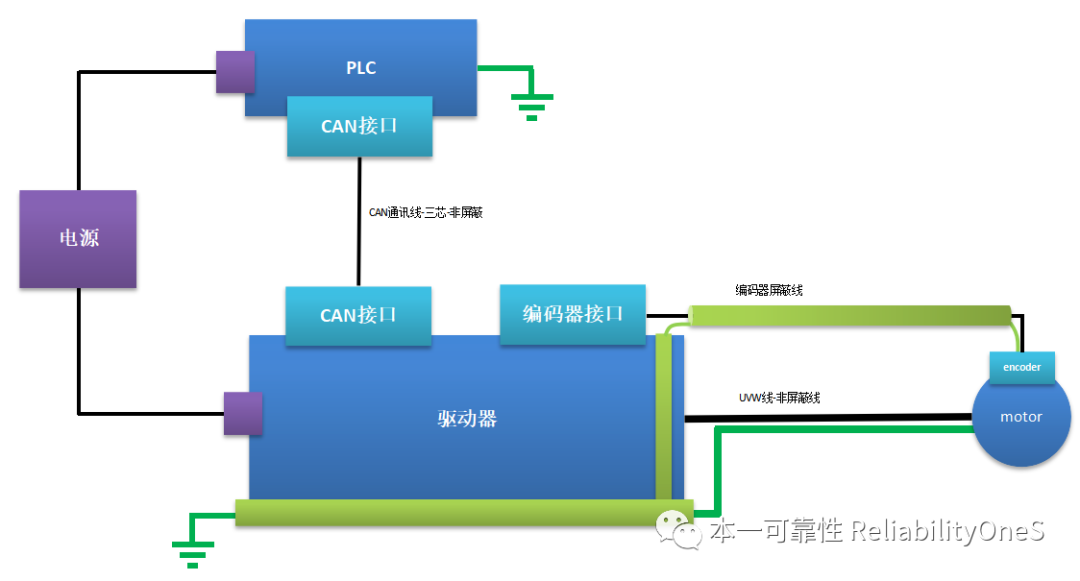

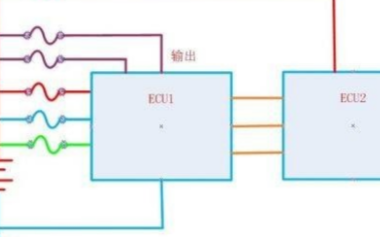

工程上常用关键路径分析法进行EMC问题的分析与排查手段,简单高效,适合大部分场景,但缺乏细致的过程路径分析,许多文献也是从仿真和基本路径的关键点进行。

2023-09-08 14:54:15 313

313

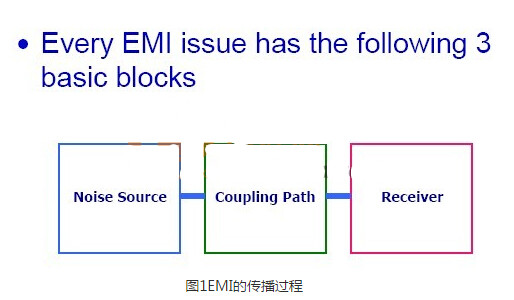

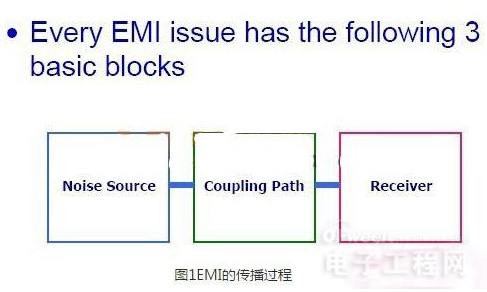

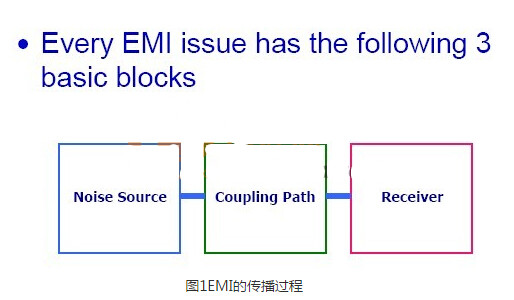

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文就将对EMI的传播过程进行一个大致的介绍。

2016-07-22 11:03:41 2162

2162

EMI/EMC设计常见问题有哪些?

2021-11-10 07:23:21

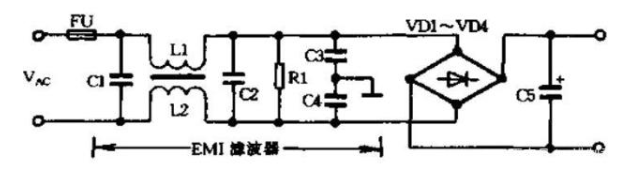

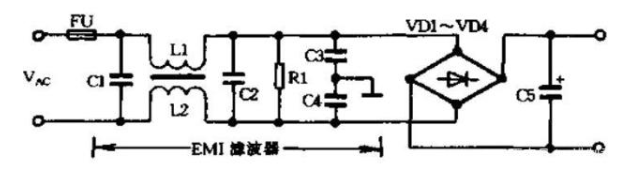

路的PCB线迹。常见的一些辐射 EMI 干扰源包括以前文章中谈及的组件,以及PCB板上开关式电源、连接线和开关或者时钟网络。传导性 EMI 干扰是开关电路正常工作与寄生电容和电感共同作用产生的结果。图 1

2013-12-06 18:01:44

,或者由一些电路板组件引起。一旦您的电路板接收到传导性干扰,它便驻入应用电路的 PCB 线迹。常见的一些辐射 EMI 干扰源包括以前文章中谈及的组件,以及板上开关式电源、连接线和开关或者时钟网络。图 1

2012-11-15 16:12:16

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文

2019-05-31 06:42:24

永久性损坏。因此,必须采取相应措施对电磁干扰进行抑制。 EMI的传播方式有两种: 1、辐射方式-能量通过磁场或电场耦合,或以干扰源与受扰设备间的电磁波形式传播。 2、传导方式-EMI能量通过

2020-11-26 17:24:38

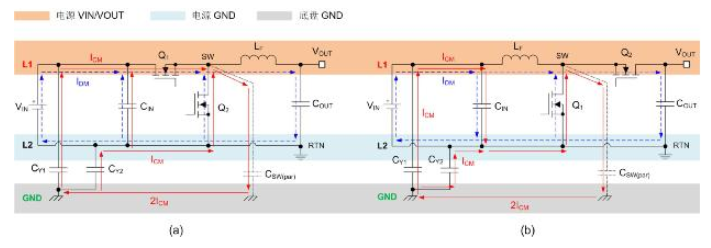

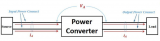

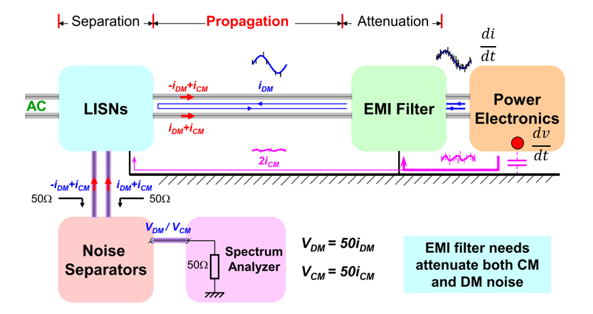

的 EMI 特性至关重要。在本系列文章的第 2 部分,您将了解差模 (DM) 和共模 (CM) 传导发射噪声分量的噪声源和传播路径,从而深入了解 DC/DC 转换器的传导 EMI 特性。本部分将介绍如何从总

2021-09-17 07:00:00

EMI超标常见是由什么引起的,怎么解决

2022-11-15 10:26:01

常见的电路分析方法有哪些

2021-03-11 07:17:53

这样。例如MMCME2_ADV这个元件,Vivado分析源时钟路径时这个元件的延时为-7.378ns,分析目的时钟路径时这个元件的延时为-6,292ns。

2022-04-24 10:32:49

求解路径分析表示根据要求解的阻抗查找最快、最短甚至是最优的路径。如果阻抗是时间,则最佳路线即为最快路线。如果阻抗是具有实时或历史流量的时间属性,则最佳路径是对指定日期和时间来说最快的路径。因此,可将

2019-06-03 08:04:46

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

2015-01-04 15:17:16

最近在分析EFT整改措施,想使整机的EFT抗扰度从B等级提升到A等级,想问问大家有没有EFT整改的一些经验,比如EFT入侵的路径分析,滤波器参数怎么调整、整机屏蔽和接地怎么处理等,希望有人能提出宝贵的经验,谢谢?

2014-06-05 07:24:40

所组成,一般对策方式为修改EMI低通滤波器/变压器耦合路径/Y电容大小/布线方式等来做对策,可依文章前面所述方法做确认。结 语电磁干扰(EMI)的防制在电源设计里是门很重要的学问,此篇文章将EMI传导

2021-03-30 15:51:57

;所谓时钟路径,则是指时钟从源端到达各个寄存器输入端的路径。(特权同学,版权所有)图8.18 reg2reg的数据路径和时钟路径如图8.19所示,为了便于后续的时序余量分析和计算,我们提出了data

2015-07-24 12:03:37

的充电部分是整机EMI效果的重要决定因素之一。<br/>因此在此专题里面将以Flyback架构为对象,分析其<br/>Noise源,传播途径

2009-10-12 08:40:11

把一 个电网络上的信号干扰到另一电网络。在高速系统设计中,集成电路引脚、高频信号线和各类接插头都是PCB板设计中常见的辐射干扰源,它们散发的电磁波就是 电磁干扰(EMI),自身和其他系统都会因此

2018-09-17 17:37:27

为了弄清楚信号在传输线的传播速度,有必要再次仔细地考察一下信号在传输线的传播过程。 前面介绍了传输线拥有两条路径:信号路径和电流返回路径。当信号源接入后,信号开始在传输线上传播,两条路径问

2018-09-03 11:06:48

系统设备达到电磁兼容标准最有效、成本最低的手段。本文介绍数字电路PCB设计中的EMI控制威廉希尔官方网站

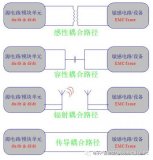

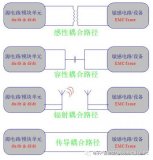

。 1EMI的产生及抑制原理 EMI的产生是由于电磁干扰源通过耦合路径将能量传递给敏感系统造成的。它包括

2011-11-09 20:22:16

量也就越大,因此,我们通过控制回流路径,可以使得环绕区域最小,从而控制辐射程度。4、回流问题的解决办法在PCB板上引起回流问题通常有三个方面:芯片互连,铜面切割,过孔跳跃。下面具体对这些因素进行分析

2021-11-27 07:00:00

产生的辐射能量。控制EMI的关键,是降低电源地平面谐振和电路回流路径阻抗,正确放置旁路和去耦电容。实例笔者使用EMISTREAM工具对板极的EMI问题进行分析。该工具是由日本NEC公司基于多年EMI

2009-04-14 16:42:41

本期直播邀请到原厂资深系统工程师为大家带来有关EMC/EMI的知识点,通过实际案例分析,EMI和EMC的测试的复杂性,有想要学习这方面知识点的同学们不要错过报名学习的机会噢~直播主题:EMC/EMI

2021-08-20 17:11:57

EMI进行预测,定位开关电源传导EMI传播路径的影响因素,在此基础上给出开关电源PCB及其结构设计的基本原则。对开关电源EMI预测过程中需要注意的问题以及降低开关电源传导EMI的方法策略进行了分析

2016-05-04 14:03:26

EMI进行预测,定位开关电源传导EMI传播路径的影响因素,在此基础上给出开关电源PCB及其结构设计的基本原则。对开关电源EMI预测过程中需要注意的问题以及降低开关电源传导EMI的方法策略进行了分析和总结

2016-04-20 16:25:31

®PCBDesigner 中 IDA(In-DesignAnalysis,设计同步分析)的 ReturnPath 分析功能,在 PCB 设计过程中进行回流路径分析,帮助工程师快速找出那些高速信号的回流路径

2020-12-07 09:24:05

EMI是电子电路设计过程中普遍的问题,一直在寻找能够完全消除或降低电磁干扰方法。想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎么样的,下面对EMI的传播过程进行一个大

2020-10-21 11:36:41

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文

2019-09-22 07:00:00

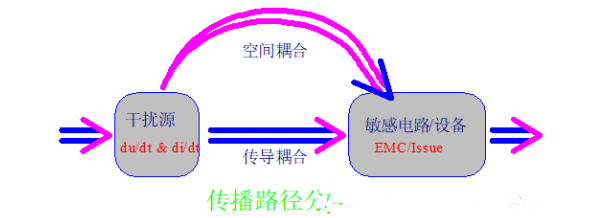

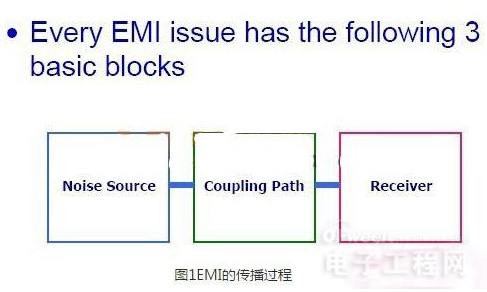

和差模干扰。**EMI的传播过程 **EMI的传播过程主要途经三个部分,干扰源、干扰途径、接收器。对于开关电源来说,最后一部分是不需要考虑的,干扰源也不能消灭,因为它也是开关电源之所以能工作的源头

2019-09-03 07:30:00

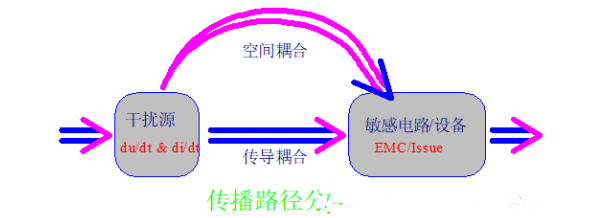

问题的方法第一,我们要了解干扰源的特点,并抑制干扰源!瞬时的电压,爬上时间,跌落时间,内阻,即干扰源发生器的特性。第二,我们要知道干扰源的传播路径并切断干扰源的传播干扰路径!我们知道干扰源的特性及路径

2018-09-02 16:22:46

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

关于开关电源EMI(Electro-Magnetic Interference)的研究,有些从EMI产生的机理出发,有些从EMI产生的影响出发,都提出了许多实用有价值的方案。这里分析与比较了几种

2018-12-03 11:22:05

系统设备达到电磁兼容标准最有效、成本最低的手段。本文介绍数字电路PCB设计中的EMI控制威廉希尔官方网站

。1、EMI的产生及抑制原理 MI的产生是由于电磁干扰源通过耦合路径将能量传递给敏感系统造成的。它包括经由

2019-09-16 22:37:29

噪声源和噪声的传播路径是什么如何选择隔离和限制噪声元件?

2021-04-08 06:05:44

电子系统通常在开关模式下工作,产生了较大的电磁干扰(EMI),EMI问题一直是电力电子工程师头疼的问题,解决EMI问题是一项既困难又耗时的工作,DC-DC 开关电源 EMI问题如何产生、传播以及如何优化解决?

2019-01-10 12:10:18

概述 如果一个新产品在电磁干扰(EMI )预兼容测试或者标准兼容测试中失败,进行故障诊断和改进是当务之急。而近场探头配合频谱分析仪查找干扰源,并验证改进效果是最常见易行的方法。 图一 安捷伦X系列信号分析仪和N9311X-100 近场探头

2019-07-22 07:54:10

针对开关电源设计阶段应考虑的EMC问题,介绍了PCB及其结构寄生参数提取和频域仿真的方法,在开关电源设计阶段对其传导EMI进行预测,定位开关电源传导EMI传播路径的影响因素,在此基础上给出开关电源

2023-09-22 07:18:09

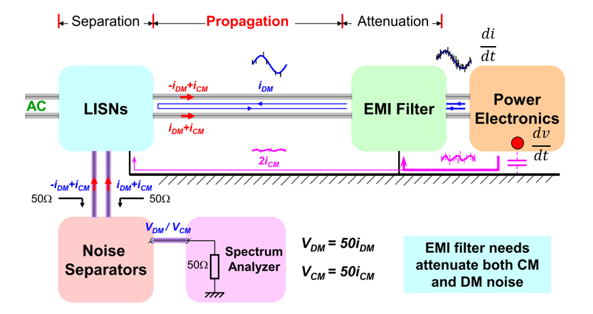

得到该电路的阻抗,谐振点等,从而为降低EMI提供有力的依据。 由于差模噪声和共模噪声的传播路径不同,有必要对DM 传播路径和CM 传播路径分别建模。这样可以更好地分析各种干扰的特点,而且还可

2011-11-01 17:56:53

开关电源传导EMI的频谱波形,通过分析波形可以定位开关电源EMI的问题所在,进而通过解决该问题而降低EMI。 降低开关电源EMI,需要从噪声源和传播路径入手。首先,对于噪声源,可以通过加吸收电路,减小di

2020-07-20 09:01:35

开关电源的EMI源 开关电源的EMI干扰源集中体现在功率开关管、整流二极管、高频变压器等,外部环境对开关电源的干扰主要来自电网的抖动、雷击、外界辐射等。 (1)功率开关管:功率开关管工作在

2011-07-11 11:37:09

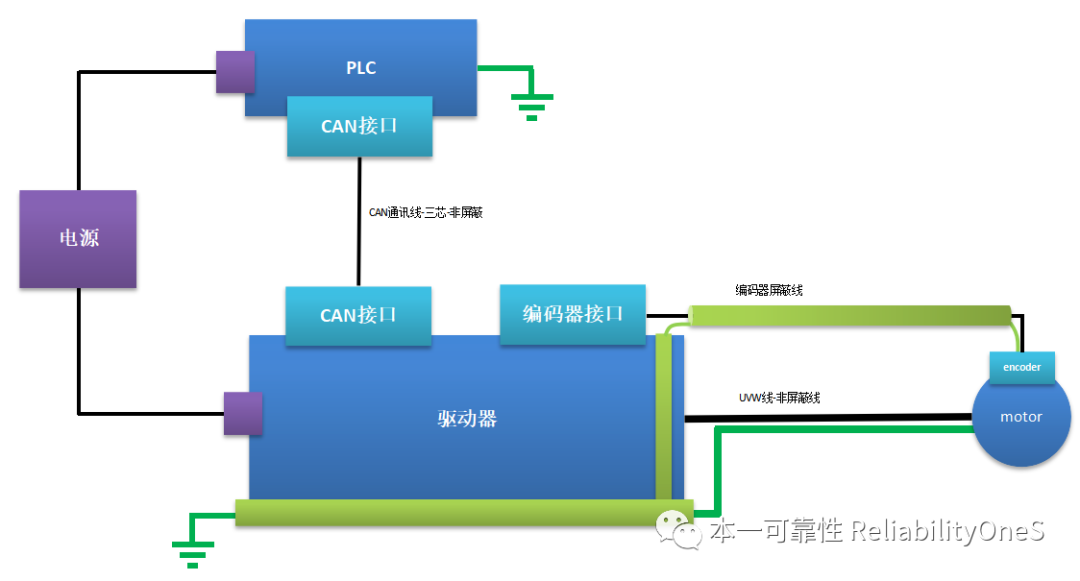

的角度能看出什么问题吗???请参考公众号文章《电子产品:PCB布局布线的耦合EMI路径分析!》提供分析依据,搞定EMI的超标设计问题!如下分析思路供参考:容性耦合路径问题注意电路中任意相近的两根电流导线都会存在分布电容耦合:临近PCB走线及 关键走线&连接线&输入共模滤波器,散热器等等;

2019-09-13 07:30:00

1. 路径传播损耗(自由空间传播损耗)L0=32.45dB+20lg(f)+20lg(D)-Gt(dB)-Gr(dB),其中D传播距离为Km.F发射频率的单位为MHz.Gt是发射天线增益,单位为

2017-09-26 10:11:53

1. 路径传播损耗(自由空间传播损耗)L0=32.45dB+20lg(f)+20lg(D)-Gt(dB)-Gr(dB),其中D传播距离为Km.F发射频率的单位为MHz.Gt是发射天线增益,单位为dB

2017-10-30 10:46:34

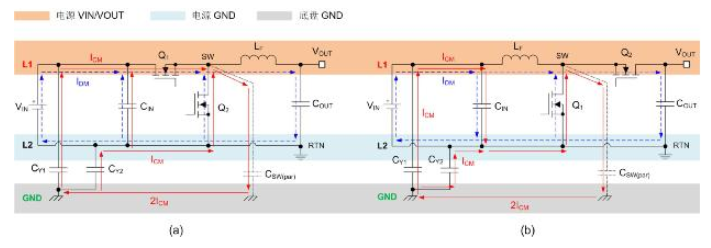

拓扑中 DM 和 CM 电流的相关传播路径(包括与高 dv/dt 和 di/dt 开关相关的电容(电场)和电感(磁场)耦合)非常重要。在 EMI 测试过程中,将 DM 和 CM 发射分开处理有助于对相关 EMI 源进行故障排除,从而简化 EMI 滤波器设计流程。

2020-09-18 07:00:00

拓扑中 DM 和 CM 电流的相关传播路径(包括与高 dv/dt 和 di/dt 开关相关的电容(电场)和电感(磁场)耦合)非常重要。在 EMI 测试过程中,将 DM 和 CM 发射分开处理有助于对相关 EMI 源进行故障排除,从而简化 EMI 滤波器设计流程。

2022-06-09 10:18:42

在电子系统设计中形成干扰的基本要素是什么?抑制干扰源的常用措施有哪些?切断干扰传播路径的常用措施有哪些?

2021-04-21 06:33:23

的 EMI 特性至关重要。在本系列文章的第 2 部分,您将了解差模 (DM) 和共模 (CM) 传导发射噪声分量的噪声源和传播路径,从而深入了解 DC/DC 转换器的传导 EMI 特性。本部分将介绍如何从总

2022-11-09 07:23:36

回路产生的,当然共模干扰也会产生部分辐射干扰。因此在设计电路时减小功率开关电流回路对传导辐射干扰有很大的帮助。 图4 DCDC噪声源及耦合路径 既然有了上面对EMI产生的原因分析,我们就可以按照

2018-12-25 11:47:36

电磁兼容试验中的重要内容就是骚扰发射试验。因此,控制骚扰发射是一项重要的设计内容。为了控制骚扰发射,首先要找到骚扰源,然后采取措施消除它,或者截断它发射骚扰能量的路径。EMI骚扰源有啥特征呢?以往

2021-12-28 07:50:47

的角度能看出什么问题吗???请参考公众号文章《电子产品:PCB布局布线的耦合EMI路径分析!》提供分析依据,搞定EMI的超标设计问题!如下分析思路供参考:容性耦合路径问题注意电路中任意相近的两根电流导线都会存在分布电容耦合:临近PCB走线及 关键走线&连接线&输入共模滤波器,散热器等等;

2019-10-08 08:00:00

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文

2021-11-08 09:32:29

简单,但也并非复杂难解。只有在充分理解 EMI 的原力之后才能对 EMI 进行行之有效的规避和抑制,希望大家在阅读过本文后能对 EMI 有进一步的了解。...

2021-06-28 08:32:43

如何通过网络数据集进行一个最短路径分析的例子。一、网络数据集的创建1.首先打开MXD地图。2.激活你的拓展模块点击菜单栏 自定义-拓展模块,然后把network给勾上

2019-05-21 06:17:12

EMI/RFI屏蔽是什么原理?常见的EMI/RFI材料有什么?

2021-04-09 06:59:43

设计,输出 15V/0.1A 典型系统供电电路;EMI 电路的滤波电路使用 2 级滤波器结构;我进行上述的 EMI 的路径分析这个 2 级滤波器完全足够解决 150KHZ-10MHZ 的传导干扰;进行

2020-07-13 14:04:11

中,我将回顾集成了有源EMI滤波器功能的汽车同步降压控制器设计的结果。EMI滤波无源滤波使用电感器和电容器在EMI电流路径中产生阻抗失配,以此减少电源电路的传导发射。相比之下,有源滤波可感应输入总线上的电压…

2022-11-04 08:12:50

降低電源中的EMI

2021-08-25 17:11:19

(In-DesignAnalysis,设计同步分析)的 ReturnPath 分析功能,在 PCB 设计过程中进行回流路径分析,帮助工程师快速找出那些高速信号的回流路径是否适当,以确保 Layout

2021-02-05 07:00:00

电波传播计算图内容有光滑地球凸起高度,球面地反射点的位置,超超波的规距,电波传播路径与大圆距离等内容。

2009-02-19 10:37:58 11

11 针对开关电源设计阶段应考虑的EMC问题,介绍了PCB及其结构寄生参数提取和频域仿真的方法,在开关电源设计阶段对其传导 EMI 进行预测,定位开关电源传导EMI传播路径的影响因素,在

2011-09-09 14:10:57 2183

2183

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。

2017-02-10 02:35:39 1245

1245

文中目的在于研究分析基于网络路径仿真系统设计的相关问题。基于广域网路径分析中,为确保提升端到端路径质量,在检测中通常采用tracert 来探测实际经由路径信息,监控网络路径质量安全;对此分析设计网

2017-10-30 10:27:25 0

0 森林通信的研究是在实际应用中提出的,因此,研究基本上是从理论和实验这两方面同时进行的。理论研究主要集中研究森林通信中电波传播主要模式—侧面波的传播特性和传播机制;实验研究则以测量实际丛林环境下的电波传播路径损耗及天线效应为主。

2017-12-26 08:44:39 10510

10510

开展大用户直购电能够激发电力市场的潜力,是电力工业市场化改革的突破口。大规模直购电交易一般为跨区跨省的长距离电力交易,对电网的运行方式和潮流计算产生影响。分析大用户直购电交易的输电路径,将为电网运行

2018-03-27 14:01:55 0

0 EMI的传播路径:感性耦合;容性耦合;传导耦合;辐射耦合! 在电磁兼容设计中;我们基本的理论是:A.确认噪声源B.了解噪声源的特性C.确认噪声源的传播路径。

2018-10-16 10:00:00 2778

2778

通过引文分析和主路径分析的方法,将Web of Science (WOS)数据库中以负面口碑为主题的文献作为研究对象,研究负面口碑的重要文献与逻辑演化路径。研究发现:Richins (1983

2018-12-20 11:20:37 0

0 EMI的传播过程主要途经三个部分,干扰源、干扰途径、接收器。干扰源可以理解成设备发现来的干扰,经过的传染途径。而对于电源来说,一般只能从两方面下手,要么减少干扰源,要么切断干扰途径。

2019-03-14 14:17:37 3067

3067

我们对EMI的传播路径:空间耦合和传导耦合比较熟悉;我们实际也是重点在运用上述的理论来进行我们的实践指导。

2019-08-25 10:36:01 2165

2165

在本系列文章的第 2 部分,您将了解差模 (DM) 和共模 (CM) 传导发射噪声分量的噪声源和传播路径,从而深入了解 DC/DC 转换器的传导 EMI 特性。

2019-08-27 15:24:22 2945

2945

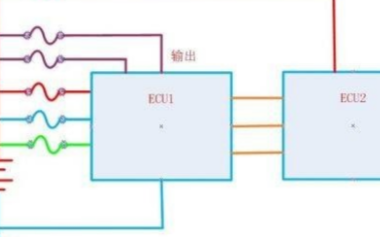

在汽车电子中有个非常重要的事情,就是潜在路径分析这个内容,如果搜索这个词,你在网上很少会发现它,事实上在国内一般只有航天航空军工去关注它。

2020-01-19 10:01:00 750

750

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文

2020-11-12 10:39:00 2

2 1、如何快速且有效地诊断EMI的噪声源头和耦合路径?

2、系统级EMI设计常见的失效原因有哪些?

3、理论和实践相结合,快速整改通过系统级EMI问题?

2020-08-17 15:26:46 2721

2721 因电磁波造成电气设备、传输通道或者系统性能降低的一种电磁现象称为电磁干扰(EMI)。

2020-12-16 11:01:10 1829

1829

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。

2020-12-31 15:17:14 1788

1788 电子发烧友网为你提供几个常见的EMI辐射问题分析思路资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:42:28 5

5 电子发烧友网为你提供一文理清EMI的传播过程资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:52:28 5

5 电子发烧友网为你提供散热障碍与散热路径分析资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-12 08:45:14 13

13 分享雷击标准、雷击实验配置、差模及共模干扰路径分析和设计原则。 雷击标准 IEC61000-4-5为常用的雷击测试标准,其定义及实验规程如下: 一般情况下,在交流线路上施加±1kV~±6kV的浪涌电压。试验源为测试设备(EUT)的交流线路和

2021-05-11 11:16:18 12949

12949

方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

基于路径分析和关系描述的知识图谱补全方法,并以泛娱乐领域相关数据为例,对该方法的有效性进行验证。构建基于泛娱乐知识特点的泛娱乐领域知识图谱,并在该知识图谱上进行验证实验。实验结果表明,提岀的方法能够很妤地

2021-06-18 11:37:11 11

11 在电力电子的EMI分析与建模中,若要得到准确的结果,一个至关重要的前提是能够准确测量出噪声源与传播路径上的阻抗。对于辐射EMI来说,通常的对应频段在30MHz到1GHz之间,由于频率很高,其电压,电流,阻抗等参数的测量容易有较大的误差。

2021-12-16 15:59:01 2277

2277

电磁干扰是电子电路设计过程中最常见的问题,设计师们一直在寻找能够完全消除或降低电磁干扰,也就是EMI的方法。但想要完全的消除EMI的干扰,首先需要的就是了解EMI是什么,它的传播过程是怎样的,本文就将对EMI的传播过程进行一个大致的介绍。

2022-02-09 11:40:06 11

11 在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25:06 426

426

EMI 的工程师指南第 2 部分 — 噪声传播和滤波

2022-10-31 08:23:58 4

4 攻击路径是指网络攻击者潜入到企业内部网络应用系统所采取的路径,换句话说,也就是攻击者进行攻击时所采取的相关措施。攻击途径通常代表着有明确目的性的威胁,因为它们会经过详细的准备和规划。从心怀不满的内部人员到恶意黑客、间谍团伙,都可能会利用这些攻击路径,窃取公司威廉希尔官方网站

、机密信息或敲诈钱财。

2022-11-02 14:13:52 777

777 对EMI进行预测。 EMI分传导和辐射两部分,传导EMI噪声可通过缆线或其他导体传到受害设备,辐射EMI噪声则是直接通过空间耦合到受害设备上。 这两种噪声因为传播途径的不同,建模和分析方法则需要分别来进行探讨。 传导EMI 那传导EMI怎么来分析? 我

2022-11-25 16:19:22 442

442 当 RPQF 值越趋近于 1,则表示信号布线与与回流路径是越贴近的,越高则代表回流路径越曲折绕越远的路径。

2023-04-17 10:28:11 2360

2360 对于NVH纷繁复杂的问题,广电计量引进传递路径分析和虚拟现实威廉希尔官方网站

。通过搭建传递路径分析模型及对模型的解析,帮助客户迅速锁定问题来源

2022-06-20 16:16:28 580

580

。 由于电磁干扰(EMI)测试通常在最后设计阶段进行,因此能够建模和分析电磁兼容性(EMI)能够有效地帮助设计者从最初设计阶段到整个设计过程中优化电磁兼容性(EMI),帮助他们避免延误和意外成本。 EMI在电子电路中通过两种途径传播:进行和辐射EMI;通过有物理

2023-08-25 15:19:20 465

465

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间

2024-01-18 16:31:44 197

197

电子发烧友App

电子发烧友App

评论