KIT STARTER COOLRUNNER-II

2023-03-30 11:49:21

它们的基本设计方法是借助于 EDA 设计软件,用原理图、状态机和硬件描述语言等方法,生成相应的目标文件,最后用编程器或下载电缆,由 CPLD/FPGA 目标器件实现。 生产 CPLD/FPGA

2019-03-04 14:10:13

亲爱的朋友们,作为一个业余爱好者,我想问一个关于通过板载USB端口连接我的CoolRunner-II CPLD入门套件的问题。是否可以使用板载USB设备对CPLD进行编程,然后将其作为已实现应用程序的通信接口进行优化?如果有可能,我应该怎么做? :)或者我需要实现额外的通信接口?玛丽亚,提前谢谢你。

2019-08-20 10:48:23

嗨团队,我在我的卡设计中使用Coolrunner 2 XC2C256 -7FT256 CPLD。该设计要求我将UART线(TXD,RXD,RTS和CTS)引脚复用为4个端口。它是TXD和RTS的1

2019-04-23 14:50:44

GPS MODULE - COPERNICUS II DIP (

2023-03-29 19:42:43

针对GPS测量系统数据传输过程中的安全问题,采用FPGA威廉希尔官方网站

设计了GPS数据加密系统。系统移植MD5算法到NIOS中对系统口令加密,并设计DES IP对GPS数据加密。实验表明,该设计可有效防止GPS数据被非法窃取,具有安全性强、速度快、操作简便等特点。

2019-08-22 06:03:00

XtremeDSP 视频入门套件加速 FPGA 上的视频开发106.3用 Spartan-3A DSP 器件实现汽车应用中的块匹配146.4 利用 CoolRunner-II CPLD 设计 GPS 系统

2012-02-27 15:46:40

This bulletin explains how to interface the Garmin GPS II Plus (p/n 2263-065) to the data collection system.

2019-03-18 13:26:17

KIT STARTER COOLRUNNER-II BUNDLE

2023-03-22 20:00:18

立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-11-04 07:42:16

需要旅行,并希望在我的酒店房间工作后学习和玩CPLD。也许BootCamp可能是一个解决方案,但我不喜欢分区我的HD并在开始时决定启动什么操作系统。此外,我无法从Mac跳到araound,反之亦然。schneetiger先谢谢你的帮助。

2019-09-02 09:58:50

KIT STARTER COOLRUNNER-II LP/LC

2023-03-22 19:57:00

你好。我试图了解Xilinx参考设计(XAPP391:使用CoolRunner-II CPLD设计16b / 20b编码器/解码器))。当执行功能模拟(包括在下载文件中)时,解码器的错误检测信号在

2018-09-28 11:18:56

XC2C32A CoolRunner-II CPLD 的一般IO 輸出電流是多少呀,採用了RC濾波,如果發現IO輸出控制端延遲了,但電容不能減小,EMI會不過,那電阻能縮小到什麽程度呢,求有相應中文資料或大神解釋相關應用

2013-11-04 14:31:09

)• Virtex-E FPGA(XCV5)• SPARTAN-6 FPGA(XC6S)• SPARTAN-3 FPGA(XC3S)• CoolRunner-II CPLD(XC2C)• 配置存储器完整版资料:Xilinx公司产品导购手册[hide][/hide]

2012-02-28 16:43:31

控制性结合Nios II软核的灵活的功能,可方便地实现功能修改和添加;高度地集成能力,较大程度上减少产品体积以及外部信号对系统的干扰,增加了系统的可靠性、稳定性和灵 活性。利用GSM和GPS进行定位数据的无线传输系统具有简单、稳定、可靠、覆盖范围广的特点,而且在成本上具有较大地优势。

2015-01-30 11:05:50

你好,我一直在尝试使用CPLD套件来控制步进电机,但是当我将其下载到CPLD套件时似乎无法工作。是不能在xc2c256 coolrunner 2 CPLD上实现状态机,或者我的代码是错误的,如果有

2019-02-12 10:06:36

你好,我正在尝试在Coolrunner2系列CPLD上实现一个系统。该系统通过不同的输入进行控制。其中一个编码为2个字节,在翻译期间被删除。[警告]:Cpld:1007- 删除未使用的输入

2018-10-08 17:39:45

GPS与GPRS分别是什么?基于GPS/GPRS的车辆监控系统是由哪些部分组成的?基于GPS/GPRS的车辆监控系统如何去实现?

2021-05-14 06:36:50

如何实现μC/OS-II系统的移植?

2021-04-28 06:01:29

本文以DSP和CPLD为主体,构建电池管理系统的硬件平台,并在DSP内部嵌入μC/OS-II实时操作系统,可大大提高系统的稳定性和实时响应能力,增强系统的可扩展性和可移植性。

2021-05-13 07:00:27

配置指南时,它说Virtex 5和Spartan 6能够通过CPLD或微控制器进行配置,但它只讨论了Coolrunner II如何配置Virtex 5,但它没有说明配置斯巴达6.有什么帮助吗?以上

2019-07-02 11:04:53

设计的基于CPLD与单片机的高速数据采集系统在QUARTUS II软件中进行了仿真并达到了预期的控制逻辑。

2021-04-13 06:07:06

应用cpld的光端机的实现,介绍了原理和系统框架,资料是河南恒茂的朋友提供的,给大家分享一下。

2014-06-10 09:00:41

怎么实现基于51单片机&GPS的导航系统设计?

2021-09-30 07:40:24

介绍了一种基于CPLD和MT8880的远程控制及语音通信的解决方案。给出了系统的原理框图和关键电路, 并对关键电路的工作原理进行了说明; 最后给出了系统主机控制器中关键模块的QUARTUS II设计图及基于VHDL语言的MT8880收发程序源代码。[/td]

2021-05-26 07:01:53

本没计以DSP和CPLD为主体,构建电池管理系统的硬件平台,并在DSP内部嵌入μC/OS-II实时操作系统,可大大提高系统的稳定性和实时响应能力,增强系统的可扩展性和可移植性。

2021-05-18 06:28:15

怎么实现基于伽利略卫星网络的GPS系统设计?

2021-06-02 06:56:02

怎么实现嵌入式GPS导航系统的设计?

2021-05-26 07:07:59

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

怎样将gps芯片防到我自己的系统中? 想再系统中加入gps功能,如何实现呢?

2022-06-22 11:53:31

Xilinx—FPGA中文实例教程Spartan-3E入门实验板使设计人员能够即时利用Spartan-3E系列的完整平台性能。设备支持:Spartan-3E、CoolRunner-II关键特性

2012-02-28 15:51:22

如何实现CPLD的在系统编程?

2021-04-25 07:05:12

嗨,我目前正在使用Artix-7 FPGA和Coolrunner II CPLD。在完成FPGA配置之前,CPLD将在复位时保留电路板上的所有内容。所以,我需要监控那个引脚。我的DONE引脚如下

2020-07-20 10:43:01

开始,因为我阅读比VHDL更容易)和设计CPLD。我的雇主从事嵌入式设计业务,其设计主要基于PLD。我购买了CoolRunner II套件并下载了Xilinx ISE软件套件。关于Verilog的好书

2019-01-11 10:55:16

CPLD CoolRunner -II Family 750Gates 32 Macro Cells 200MHz 0.18um, CMOS Technology 1.8V 32Pin QFN

2022-05-30 16:48:06

EPM570T144C5N - 芯片, CPLD, MAX II, 570单元, 144TQFP

2022-07-29 17:19:16

Xilinx CoolRunner XPLA3 CPLDs provide designers with several useful configuration optionsfor each

2009-05-13 12:58:31 28

28 An interface to the 8051 microcontroller has been implemented in a CoolRunner XPLA3 CPLD

2009-05-13 14:57:00 15

15 Implementing Keypad Scanners with CoolRunner-II

This application note provides a functional

2009-05-14 11:01:24 20

20 在单片机系统中使用CPLD,可使系统构成灵活,提高可靠性,缩短开发周期。介绍在MCS-51 应用系统中的CPLD 应用设计实例, 详细分析CPLD 的应用和实现方法,提出设计中选用和使用CPLD

2009-05-14 13:49:49 39

39 介绍了基于CPLD 和EDA 威廉希尔官方网站

的BIT(机内测试)系统的实现。本系统以CPLD 为控制核心,在MAX+PLUSII 环境下采用VHDL 语言实现了系统接口及测频电路。该系统具有集成度高、灵活性强、易于开

2009-09-03 09:30:51 9

9 由高速图像采集子系统和GPS 精密授时子系统构成,为图像采集提供精确的时间基准。设计并实现了基于PCI 总线的GPS 时间获取板卡,并完成了一系列软件的设计开发。首先通过CPLD

2009-12-19 14:01:07 21

21 本文介绍了Jupiter GPS 接收板及其提供的时间信息,利用Jupiter GPS 接收板设计并实现了完整的自动授时时钟系统,可对本地时钟和计算机时钟进行自动和手动同步,时钟精度可达毫

2009-12-26 11:06:12 22

22 用CoolRunner-II CPLD降低设计难度(提高易用性):CoolRunner-II CPLD 入门套件内置实时功耗测量与报告功能。XMeter程序读出1.8V电源的功耗测量值,并且将数据实时绘制成曲线图。

2010-04-25 10:27:26 16

16 CoolRunner-II CPLD应用资料

This application note describes a method to configure Xilinx FPGAs

2010-05-13 13:54:24 11

11 CPLD应用资料

Managing Power with CoolRunner-II CPLDs

This application note demonstrates how multiple

2010-05-13 14:00:19 39

39 在单片机系统中使用CPLD,可使系统构成灵活,提高可靠性,缩短开发周期。介绍在MCS-51应用系统中的CPLD应用设计实例,详细分析CPLD的应用和实现方法,提出设计中选用和使用CPLD的

2010-07-14 14:04:25 39

39 介绍了基于CPLD的刷卡式电脑联网集控型自动存包系统的设计,并对系统的软硬件构成、CPLD内部逻辑设计、工作原理等进行了详细说明。该系统速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

20 由高速图像采集子系统和GPS精密授时子系统构成,为图像采集提供精确的时间基准。设计并实现了基于PCI总线的GPS时间获取板卡,并完成了一系列软件的设计开发。首先通过CPLD硬件实

2010-07-23 10:52:15 16

16 XCR3256是Xilinx公司推出的CoolRunner系列CPLD器件,在数字系统设计中的应用非常广泛。本文详细分析了CoolRunner系列CPLD的特点、结构及功能,使用VHDL语言编程实现数字逻辑,实现了水下冲击

2010-08-06 16:29:07 15

15 基于CPLD和嵌入式系统的高速数据采集系统的设计与实现

介绍一种基于CPLD和嵌入式系统的高速数据采集系统,并详细阐述了系统的结构和软硬件的实

2009-10-15 23:46:59 616

616

Altera增强MAX II系列,进一步拓展其CPLD应用

Altera公司宣布,提供工业级温度范围以及功耗更低的MAX IIZ器件,从而进一步增强了MAX II CPLD系列。MAX IIZ CPLD完美的结合了逻辑

2009-11-05 09:53:58 1283

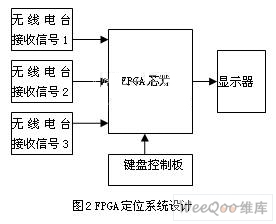

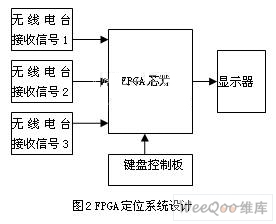

1283 GPS定位替代系统的FPGA实现

概述:本文在分析目前使用的GPS定位系统的基础上,探讨了一种替代系统,系统通过接收不同城市广播电台的发出的报时信号,算出这些地

2010-04-17 17:40:35 1023

1023

Spartan-3E入门实验板使设计人员能够即时利用Spartan-3E系列的完整平台性能。 设备支持:Spartan-3E、CoolRunner-II 关键特性:Xilinx 器件

2011-01-18 16:23:32 110

110 This white paper provides an overview of the RealDigital technology used in Xilinx CoolRunner-II

2011-03-31 17:35:27 18

18 供电元件关断和接通(也称为闪断)功能需要很少的系统干预,是非常有用的节电威廉希尔官方网站

。Altera MAX II CPLD支持简洁的上电排序,提供专用功能,非常适合实现这类威廉希尔官方网站

。本应用笔记讨论利用

2011-04-13 14:17:53 46

46 本文介绍了基于CoolRunner CPLD的MP3应用开发板的设计流程,验证了利用现有IP Core设计的可行性和高效性。在设计过程中,硬件(实验评估板)的设计和基于IP Core的算法设计可同步进行,避免

2011-08-18 10:14:51 1491

1491

This application note shows how a Xilinx CoolRunnerTM-II CPLD can be used as a simplelogical switch

2012-02-09 14:25:56 32

32 The CoolRunner-II CPLD is a highly uniform family of fast, low-power devices. Theunderlying

2012-02-09 17:14:36 25

25 for a N x N DigitalCrosspoint Switch. The code is designed with eight inputs and eight outputs in order to targetthe 128-macrocell CoolRunner-II CPLD device but can

2012-02-09 17:19:37 23

23 本资料是关于基于Quartus II FPGA/CPLD数字系统设计实例(VHDL源代码文件),需要的可以自己下载。

2012-11-13 14:03:36 907

907 NBP13 Xilinx CoolRunner-II PQ208 Rev1.01

2016-02-17 14:51:49 0

0 基于CPLD的SGPIO总线实现及应用

2017-01-24 16:00:51 75

75 GPS接收机中1553B总线接口的CPLD设计

2017-02-07 15:53:43 10

10 基于单片机的GPS智能导游机系统设计与实现_付欣玮

2017-03-17 10:27:46 10

10 ARM9和μC_OS-II的SD卡文件系统设计与实现

2017-10-31 11:09:39 7

7 PicoBlaze是8位微处理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA与CoolRunner-II系列以上的CPLD器件设计中以IP核的方式提供,使用是免费的 。常见的版本有KCPSM3和KCPSM6。其中KCPSM支持7系列的Xilinx FPGA。

2017-11-17 20:28:01 3437

3437

介绍了一种用CPLD(复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过时cPLD和竹L电路的比较及cPLD在系统中实现的强大功能,论述了CPLD在测试系统接口中应用的可行性和优越性,简单介绍

2019-01-01 16:18:00 1472

1472

CoolRunner II汽车256宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-19 14:49:15 3

3 CoolRunner II汽车384宏单元装置设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-19 14:49:18 6

6 CoolRunner II汽车64宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-20 11:12:25 13

13 CoolRunner II汽车128宏单元设备是专为高性能和低功耗应用而设计的。这为高端通信设备节省了电能,并为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-20 11:12:26 6

6 CoolRunner™II汽车32宏单元设备是专为高性能和低功耗应用而设计的。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-21 11:34:55 8

8 Xilinx CoolRunner™-II汽车CPLD提供与XA9500XL CPLD系列相关的高速和易用性,以及在单个CPLD中的极低功率多功能性。这意味着,完全相同的部件可以用于高速数据通信

2019-02-21 15:04:21 9

9 CoolRunner™II 32宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-22 11:47:41 46

46 CoolRunner II 512宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-22 11:47:30 6

6 CoolRunner II 384宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-22 16:21:42 12

12 Xilinx CoolRunner™-II CPLD提供与XC9500/XL/XV CPLD系列相关的高速和易用性,在单个CPLD中具有极低功率的XPLA3系列多功能性。这意味着,完全相同的部件

2019-02-22 17:25:50 6

6 CoolRunner II 128宏单元设备设计用于高性能和低功耗应用。这为高端通信设备节省了电能,为电池驱动的设备提供了高速电能。由于低功耗的备用和动态运行,提高了系统的整体可靠性。

2019-02-26 10:29:24 23

23 无论是设计通信、消费、计算机或工业应用,MAX II器件都能够为成本和功率受限的控制通道应用提供所需的功能。MAX II更低的价格,更低的功率和更大的容量使其成为复杂控制应用的理想方案,包括以往不可能在CPLD中实现的新应用。

2019-03-27 16:42:55 18

18 MAX II具有传统CPLD设计的低成本特性,MAX II CPLD还进一步提高了高密度产品的功耗和成本优势,可以使用MAX II CPLD来替代高功耗和高成本ASSP以及标准逻辑CPLD。

2019-12-18 07:04:00 3059

3059

Altera的MAX® II 系列在所有CPLD系列中,其单位I/O引脚的功耗和成本都是最低的。MAX II CPLD支持高级功能集成,以降低系统设计成本。

2019-12-12 07:02:00 2421

2421

CPLD实现Watchdog 功能,通过对寄存器的操作,实现Watchdog各项功能。CPLD 内部Watchdog 模块逻辑框图如下所示。

2019-06-12 15:59:33 10

10 CoolRunner-II是一个可帮助设计人员开发出最新的CPLD设计的完整工具箱!

2019-11-14 16:03:17 2374

2374

Quartus II软件为使用Altera?FPGA和CPLD设备进行设计的系统设计师提供了一个完整的软件解决方案。Quartus II程序员是Quartus II软件包的一部分,它允许您编程

2020-09-17 14:41:00 32

32 立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 电子发烧友网站提供《利用MAX II CPLD实现LCD控制器.pdf》资料免费下载

2023-11-10 09:36:39 0

0 AMD公司近日宣布,将停产一系列老旧的芯片产品,包括CoolRunner和CoolRunner II CPLD芯片,以及Spartan II和Spartan 3 FPGA芯片。

2024-01-18 17:00:06 746

746

电子发烧友App

电子发烧友App

评论