加载方法 ZYNQ的启动镜像是由FSBL程序(bootloader),PL配置文件(硬件比特流文件),应用层软件三个部分组成,其通过SDK的软件生成工具把三个部分按规定的格式拼凑成一个.bin文件

2020-12-05 10:15:37 4952

4952

比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

733 FPGA器件有哪些配置下载方式?下载电缆ByteBlaster原理及配置方式

2021-04-15 06:26:33

嗨,大家好,只是一个简单的问题。 FPGA编辑器是否有限制为包含嵌入式处理器(如PowerPC)的设计生成比特流?我问的原因是因为我在Project Navigator中创建了一个设计并运行了PAR

2018-10-18 14:44:29

Zynq FSBL src main.c在哪里是从QSPI加载比特流到Artix的PL的函数。我正在尝试添加从QSPI加载位的功能到XIP的PL(参见下面的链接)。在下面的示例中,没有PL。另一个

2020-03-19 10:33:09

嗨,我正在使用Zynq进行部分动态重新配置。我知道我可以在启动时通过boot.bin加载静态位流。同时,我还可以在boot.bin中包含我的部分比特流,以便在启动时将其存储在RAM中的某个地址中

2020-04-21 10:23:57

`请问比特流是什么?`

2019-08-23 16:24:40

ATK-领航者ZYNQ开发板-7010 Edition DEVB_120X160MM 6~24V

2023-03-28 13:05:54

ATK-领航者ZYNQ开发板-7020 Edition DEVB_120X160MM 6~24V

2023-03-28 13:05:54

STM32开发板 STM32F103RCT6最小系统板 ARM 一键串口下载 液晶屏

2023-04-04 11:05:04

1.为什么用USRP发送数字调制信号后,如FSK和QPSK,接收端解码出来的比特流都是不对的?

2019-08-28 09:18:11

,我生成了比特流,我得到以下两个错误:[DRC NSTD-1]未指定的I / O标准:4个逻辑端口中有1个使用I / O标准(IOSTANDARD)值'DEFAULT',而不是用户指定的特定值。这可

2019-09-30 10:39:23

(xczu7eg-ffvf1517-1-e),代码实现并正确生成比特流。然而,当我使用Xilinx平台电缆II通过JTAG配置带有比特流的设备时,我得到错误Labtools 27-3303。 (分配给设备的比特流不正确

2020-06-09 14:24:42

嗨,大家好,我正在开发一个Vivado项目,其中包含JESD IP内核。我使用的工具是Vivado 2015.4,我们拥有JESD的有效许可证。该项目的合成和实施是成功的。但是,生成比特流时发生错误

2018-12-18 10:45:31

大家好,最近刚接触FPGA不久 现在手上有一块xilinx SP3E开发板,简单的设计了一个流水灯的程序 通过JTAG下载方式 直接下到FPGA里 板子可以运行 因为想实现断电后重启板子自动

2014-10-11 11:16:08

你好,我只是想知道Xilinx是否有用于比特流加密的文档(或教程)。 UG191的第33-35页有一些简短的说明,但我不知道Xilinx是否喜欢逐步实施。谢谢。强

2020-06-15 13:39:44

(具体可以查阅xilinx的相关教程),然后再下载到开发板上的flash中。这整个过程都没问题,但是本人一直很奇怪.mcs文件是怎么写入flash中的,是通过JTAG连接器经过FPGA芯片在写入

2017-09-20 21:29:07

大家好,我正在与SoC迈出第一步,我目前正在使用Zybo Zynq开发板。我有一个简单的问题:是否可以创建多个设备配置,为每个配置生成比特流并将比特流存储在内存或其他内容中,以便创建一个说“配置库

2020-05-20 10:44:19

ch340下载方式与STLINK/JLINK下载方式有哪些不同呢?

2021-12-15 07:00:38

labview怎么导入视频,然后再将其转化为比特流?新手小白,求助各位大佬解答,最好能给个vi例子解释一下,非常感谢

2023-10-18 23:58:07

。第二步:如果你是在原来的工程上面修改的,建议你在export hardware时把原来工程的.sdk文件夹里面的东西全都删掉,然后再重新产生比特流。.sdk文件夹中的内容,.hdf是生成比特流后产生

2015-06-14 14:27:17

都还离不开ISE,除非,ISE不支持该芯片(比如A7最小的那几块)。 (3)用vivado集成环境内的硬件会话(hardware session)下载比特流时断开板子再连接, hw_server就会连接不上, 卡顿在那,必须退出vivado, 在任务管理器结束hw_server才行。

2015-07-08 17:35:03

嗨,我正在尝试部分自我重新配置。想法是通过介质将部分比特流发送到FPGA。FPGA接收它(在多个块中)并将比特流写入ICAP。当连接发生时,我的FPGA的行为会发生什么发送部分比特流中途消失了?我

2019-02-14 09:40:06

50MHz QSPI频率.-使用比特流压缩将我的比特流文件减少到大约1,6MB而不是3,6MB通过这种方法,我可以达到160毫秒左右的启动时间。这适用于某些PC但不适用于所有PC。我知道Tandem

2020-06-09 16:42:15

大家好,有没有一种简单的方法可以使用IMPACT(ISE)将比特流下载到Zynq设备中而无需启动ARM?我知道这可以用Vivado完成。TIA

2020-07-21 15:11:31

加载部分比特流时,它不起作用。我在ML605板上工作。我阅读了有关PRC和EPRC的XAPP887,但我真的不明白如何更改设计以执行加密。有人可以帮帮我吗?星期六以上来自于谷歌翻译以下为原文Hi, I

2019-01-23 10:43:02

大家好,当我将在XPS中为我的系统生成的比特流下载到我的目标板时出现错误.jtag链是串行链,设备1是来自ACTEL的aglp125vs CPLD,设备2是目标fpga

2019-01-18 17:20:43

25MHz的自由运行clk模式下完成。我不知道如何调试这个。我可以以某种方式回读fpga比特流,看看差异在哪里。我记得这对ise / impact来说是不可能的,因为比特流在回读时会以某种方式被修改 - 是否有可能用vivado做到这一点?问候Klemen

2020-08-06 09:15:36

如标题所述,我想从相同的实现为同一FPGA(Artix-7)生成2种类型的比特流(SPI x4和SelectMAP x16)。这有点可能吗?目前,我有两种不同的实现运行(由于约束集 - 在xdc文件中的CONFIG_MODE是不同的),它们必须单独运行以生成相应的比特流。

2020-06-09 07:40:00

我正在开发一个具有大型远程可升级比特流和慢速闪存写入速度的项目。这些比特流使用普通文件压缩(pkzip,gzip等)传送。我想将更新的比特流以压缩格式存储在闪存上,并使用多引导方法引导它们

2020-05-29 17:12:21

你好,请有人解释我如何使用IMPACT在FPGA xilinx中下载比特流先谢谢你以上来自于谷歌翻译以下为原文hello,please can someone explain me how

2019-01-15 10:08:59

:PROM应包含以USR_ACCESS寄存器为目标的数据包。我使用iMPACT生成了我的PROM文件,只需将两个比特流放入单个MCS文件中,这可能是错误的。我认为我的MCS应该包含正常的主FPGA比特流,然后

2020-05-29 10:14:55

Mul7.穆添加8. Mul Sub9. Mul Mul现在我希望为上述任何一种组合提供完整的比特流(比如Add Add)。并且我希望部分比特流用于所选择的组合,即添加用于部分区域1和1。 2,Sub

2020-05-05 09:42:44

的笔记本电脑我想将一些比特流文件发送到NEXYS 4 Board中的Artix-7 Xilinx FPGA,然后使用这个比特流数据存储闪光灯。我已经为这块板提供了Pmod Wifi模块。可以与我的笔记本电脑

2020-04-30 07:46:17

如何检查比特流中的多重引导回退设置? abitstream中的CONFIGFALLBACK ENABLE信息在哪里?我对多重引导的约束设置看起来很合理,我只想确认比特流中的设置是否符合约束条件。从我

2020-06-05 12:38:38

这就是为什么DDR3 SODIMM无法工作的原因。为了确认效果,我在比特流的“启动选项”中选择“等待DCI匹配”作为“自动”。根据选项,如果DCI无法匹配,DONE将不会变高。我使用上述设置下载比特流

2020-06-15 16:36:57

你好,这是一个思维设计,而不是我正在积极努力的东西,但是:我想分析一下比特流。比特流包含在时钟脉冲或两个时钟脉冲之间对齐的脉冲。没有明确的时钟信号,但我知道粗略的时钟速度,并且在比特流中嵌入同步序列

2018-12-17 16:35:26

所有:由于缺少DMS respin的源文件,我很高兴不得不重用遗留部分。我所拥有的只是一个最初存储在XC1701部件上的比特流。我们相信我们已经使用板外编程器成功地将此流编程到Micron

2020-05-29 11:06:25

XPS中设计了您的硬件平台,最终为FPGA生成了一个比特流。”这是真实的,我就是这样。现在它说,“......你将硬件平台描述导出到软件开发套件(SDK)。”手册说要遵循以下步骤:1.在PlanAhead

2020-03-23 09:19:10

用iMPACT工具向Spartan 6下载“SPI Flash编程”比特流,该工具将从PC接收数据,以便使用步骤2中生成的文件对SPI进行编程。4.我们将使用PROG_B使用SPI中的新数据重启Spartan

2019-07-04 08:13:32

你好我有一个在MIcroBlaze上运行linux的设计要求。我能够在我的Virtex-7 FPGA上下载比特流(在Vivado 2014.4中生成)。我使用Impact来编程我的FPGA。我因此

2020-04-02 10:05:40

嗨,我有一个应用程序,我希望在下载到FPGA之前使用类似于data2mem的工具来在FPGA比特流中破解块内存内容。FPGA可以是Virtex 6或Artix 7或Kintex 7。比特流未加密且未

2019-03-19 12:44:14

我在使用EDK 10.1中的微填充处理器在FPGA中下载比特流文件时遇到问题。我只是将Microblaze processsor比特串文件下载到FPGA中(斯巴达3a dsp)...连接的要求是什么?我有JTAG和一个串口....什么是stepi必须遵循。

2020-03-30 10:07:31

嗨,我有几块带有Spartan 3器件的电路板,并希望将相同的比特流加载到所有电路板中。我应该选择哪个端口在电路板和设备上使用?是否可以在JTAG配置模式下进行配置?谢谢。阿卜杜拉以上来自于谷歌翻译

2019-01-10 11:15:42

嗨,我想尝试色度重采样器IP。所以我获得了硬件评估许可证,以便在我的主板上进行测试。但是,在比特流生成过程中,我得到了:[Common 17-69]命令失败:此设计包含一个或多个不允许生成比特流

2019-01-08 10:07:07

嗨我有一个问题,我无法在我的spi flash中加载比特流,我在链中有两个不同的FPGA。 Impact看到了单个FPGA及其Flash,但是我无法在比特流中加载它们。我试图简化链路绕过两个附加

2020-03-23 08:47:52

'hdcp@2015.09'未经许可.IPCP功能在IP GUI上也不可用(灰显)。忽略此严重警告后,我们能够生成,合成,放置和路由知识产权。但无法生成比特流。错误是:[Common 17-69]命令失败:此

2019-01-03 11:06:05

你好,我使用Vivado 2017.4;当我运行Synthesis和Implementation时,一切似乎都可以。但是,当我想生成比特流文件时,没有任何错误消息发生。.runs / impl_l

2018-11-09 11:37:53

嗨专家, 我正在使用spartan-6 FPGA进行多重启动实验。我发现位文件位于ug380上,如下图所示。黄金比特流位于闪存的下部块上,多重引导比特流位于闪存的较高块上。 因此,如果我想使用保护区

2020-06-09 17:43:26

来自EMI12.4和13.3的比特流文件中的重要区别是什么?我从开始文件tosequence 0xF,交换和loadind到FPGA切换字节。来自12.4boot的比特流确定,但不是来自13.3。谁能帮我?

2020-06-12 14:04:57

求助,生成DDR200T开发板FPGA bit/mcs文件时需要下载Release package怎么下载?

2023-08-12 08:30:07

嗨,我正在尝试使用JTAG将比特流下载到ML507。平台电缆变为绿色并检测到JTAG链。问题是,我无法下载比特流。IMPACT报告:错误显示在状态寄存器中,释放完成位不是1。SW3配置为:00010100希望有人可以提供帮助,安德烈log.txt 6 KB

2019-08-26 10:03:51

大家好,当我尝试在本教程中生成比特流时:http://blog.idv-tech.com/2014/05/18

2018-10-24 15:31:25

STM32程序的DAP下载方式和串口下载方式分析前提简述DAP下载方式功能快捷键合理的创建标题,有助于目录的生成如何改变文本的样式插入链接与图片如何插入一段漂亮的代码片生成一个适合你的列表创建一个

2021-07-16 06:20:09

你好我用vertex6购买评估板我下载ISE 12.1,安装完整版,进行30天评估,获得许可。但是,当我在XPS中生成比特流时,我得到:信息:安全性:65- 您的“ISE”许可仅供试用:安全:69-

2018-11-27 14:36:14

有没有办法改变比特流文件位于Vivado(2016.1)内的位置?我知道我可以在Tcl控制台上输入tcl命令“write_bitstream”(https://forums.xilinx.com

2020-05-12 09:23:20

的模块。之后,我可以执行实现和位生成,该工具将创建完整和部分比特流。通过这种方式,我将得到4个比特流,两个部分(每个可重新配置模块一个比特流 - 让我们称之为BIT_A)和两个完整(一个比特流,左移

2020-06-04 08:52:24

MYD-C7Z015是米尔科技推出的基于Xilinx Zynq-7015(XC7Z015)芯片的一款FPGA+ARM的嵌入式开发板,该产品采用核心板加底板架构模式,提供了稳定的CPU最小系统模块,方便二次开发产品外围接口、功能,使不同william hill官网

的产品快速上市。

2021-07-27 11:08:19

FPGA/CPLD下载方式 (ISP下载线接口电路)

SP功能提高设计和应用的灵活性未编程前先焊接安装系统内编

2009-03-08 10:47:02 129

129 本资料是FPGA开发板DIY 脚本文件。

2012-09-29 11:29:36 73

73 串口isp下载方式串口isp下载方式串口isp下载方式串口isp下载方式串口isp下载方式

2015-12-18 11:48:43 0

0 学习FPGA的程序下载方式,包含altera和xilinx程序下载方式,下载程序所用格式分类以及格式转换工具介绍。

2018-10-31 08:00:00 17

17 在使用 FPGA 构建的基于微控制器的典型系统中,开发人员需要管理用于加载 FPGA 编程比特流的序列和安全性。在 Zynq SoC 中,集成的处理器负责执行常规微控制器的任务,包括管理 PL 结构

2019-04-30 16:42:51 4721

4721

本文档的主要内容详细介绍的是火龙果ZYNQ FPGA开发板的电路原理图免费下载。

2020-03-09 08:00:00 37

37 有些人对于FPGA下JTAG的下载方式有些迷惑,为什么出现配置芯片了,为什么要用不同的下载电缆,不同的下载模式?通过在网上查阅相关资料做了总结和整理如下:

2021-01-05 16:21:16 17

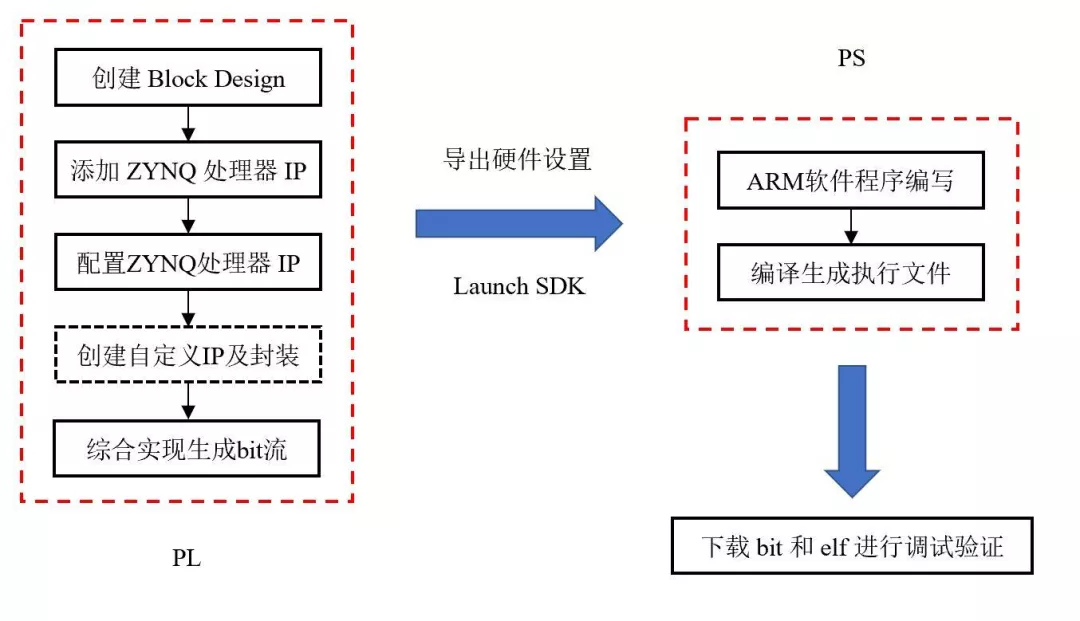

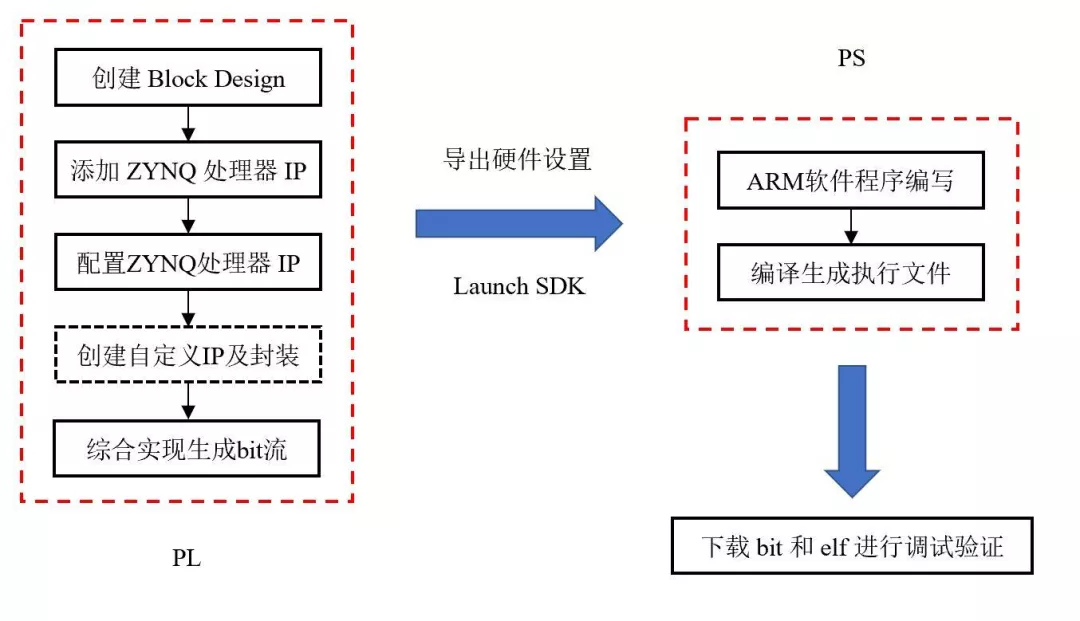

17 硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

2022-02-08 11:48:37 1021

1021

硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

2021-01-26 07:30:29 20

20 本文档的主要内容详细介绍的是Altera Cyclone III系列FPGA开发板的库文件免费下载。

2021-03-07 08:00:00 17

17 STM32环境配置和下载方式

2021-12-07 11:06:10 6

6 电子发烧友网站提供《使用加密保护7系列FPGA比特流.pdf》资料免费下载

2023-09-13 15:31:19 0

0 接下来我们下载两块开发板的测试程序,先在5CEFA7F23的下载器内添加比特流文件,输入翻转率50%比特流文件并且加载。

2023-12-15 11:41:00 239

239

电子发烧友App

电子发烧友App

评论