亲爱的先生,我们有一个项目,我们需要6个UART。所以我们计划使用100引脚控制器。市场上可用的100引脚控制器是PIC24FJXXXGB610这个控制器包含6个UART,当我看到数据表时,它显示

2020-05-14 08:36:53

10G以太网系统中的并行CRC编解码器的设计

2012-08-10 17:59:00

的应用可略见一斑。差错控制理论是在代数理论基础上建立起来的。这里我们着眼于介绍CRC的算法与实现,对原理只能捎带说明一下。若需要进一步了解线性码、分组码、循环码、纠错编码等方面的原理,可以阅读有关资料

2010-09-20 12:13:14

FPGA实现的SATA控制器FPGA实现的SATA控制器

2012-08-11 18:08:52

问答选编问:Cortex-M1微控制器有哪些接口资源?答:Cortex-M1处理器挂在AHB总线上,AHB总线通过桥接逻辑可以挂APB总线,APB总线上可以挂的接口有IIC、UART、PWM、中断

2019-07-26 07:46:51

;25.4.3 CRC 控制寄存器(CRC_CR)位 4:3 POLYSIZE[1:0]:多项式大小这些位控制多项式的大小。00:32 位多项式01:16位多项式10:8位多项式11:7位多项式"

2022-12-09 06:14:34

FPGA中的数字控制器是什么?System Generator中的PID控制器是如何设计的?

2021-04-08 06:51:46

Verilog并行CRC校验

2012-08-20 21:52:15

大家好,STM32L0 系列微控制器通过 UART 闪存,但 STM32G0 系列微控制器不是能够通过 UART 闪烁。所以问题是“使用 UART 闪存 STM32G0 系列微控制器的方法是什么”

2022-12-21 06:02:40

分享如何利用FPGA设计帧存控制器的方法?从而去实现帧存的交替 、上电清屏等。

2021-04-08 06:19:05

。实际上,这种经验很难以实际应用。硬件的选择受限于微控制器内核的基本算法函数,以及DSP内核的乘法/累加和线性函数处理,虽然FPGA所具有更高灵活度,但其缺点是外形尺寸、功耗以及批量时的单位成本。可选

2008-09-27 11:42:55

DSP芯片组成并行处理系统。另外,为充分发挥 DSP芯片在复杂算法处理上的优势及FPGA在大数据量的底层算法上的优势,设计了一种基于FPGA控制的多DSP并行处理系统。1 系统设计基于FPGA控制的多

2019-05-21 05:00:19

目前伺服控制器的设计多以DSP或MCU为控制核心,但DSP的灵活性不如FPGA,且在某些环境比较恶劣的条件如高温高压下DSP的应用效果会大打折扣,因此以FPGA为控制核心,对应用于机载三轴伺服控制平台的控制器进行了设计与优化。

2019-07-16 07:41:04

基于FPGA的图形式AMLCD控制器该如何去设计?怎样去设计一种VGA视频接口电路?

2021-06-08 06:57:57

现在市场上有基于FPGA的多电机运动控制器的成品吗,注意是成品哟,成品!成品!成品!

2016-01-19 11:22:17

刚刚开始入门FPGA,现在想做基于FPGA的智能温度采集控制器设计,各位大神谁做过这个设计,能不能把包给我!!谢谢了,我qq985984834

2014-02-18 15:50:32

转帖摘要: 针对嵌入式软件无法满足数字图像实时处理速度问题,提出用硬件加速器的思想,通过FPGA实现Sobel边缘检测算法。通过乒乓操作、并行处理数据和流水线设计,大大提高算法的处理速度。采用模块

2017-11-29 08:57:04

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来说,其并行度和扩展性都很好,它逐渐成为构造可编程高性能算法结构的新选择。

2019-10-22 07:14:04

哪位大侠可以提供基于ADC0832与FPGA的采样控制器的设计思路,万分感谢!!!最好可以提供采样精度算法、中断控制流程

2013-12-28 20:11:06

在很多嵌入式控制系统中,系统既要完成大量的信息采集和复杂的算法,又要实现精确的控制功能。采用运行有嵌入式Linux操作系统的ARM9微控制器完成信号采集及实现上层控制算法,并向DSP芯片发送上层算法得到控制参数,DSP芯片根据获得的参数和下层控制算法实现精确、可靠的闭环控制。

2019-08-19 06:29:34

(FPGA)作为核心处理器的协处理架构的开放式运动控制器。该控制器将PC机和DSP的信息处理能力与FPGA的外围扩展功能很好的结合在一起,具有信息处理能力强、模块化、开放程度高、运动轨迹控制精确等优点。

2019-09-04 07:10:42

(FPGA)作为核心处理器的协处理架构的开放式运动控制器。该控制器将PC机和DSP的信息处理能力与FPGA的外围扩展功能很好的结合在一起,具有信息处理能力强、模块化、开放程度高、运动轨迹控制精确等优点。

2019-08-30 08:27:17

控制器越来越多地运用在运动控制系统中,具有较高的集成度和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。本文选用DSP与FPGA作为运动控制器的核心部件,设计了

2009-09-19 09:43:00

请教一下,基于DSP和FPGA的嵌入式控制器该如何去设计?

2021-05-06 09:16:19

基于查表法的快速CRC算法设计

2012-08-20 20:01:16

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

你好,我正在使用连接到TMS320F28335 DSP的XC7A35T FPGA。有没有办法将位流CRC存储在FPGA中,然后使用DSP进行读取?我想为每个版本生成一个新的固件版本号,将版本号存储在FPGA中,然后使用微控制器读取它。我该怎么做谢谢。斯蒂芬

2020-06-10 14:58:29

的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。利用DSP与FPGA设计运动控制器,其中DSP用于运动轨迹规划、速度控制及位置控制等功能;FPGA完成运动控制器的精插补功能,用于精确计算步进电机或伺服驱动元件的控制脉冲,同时接收并处理脉冲型位置反馈信号。那么,我们具体该怎么做呢?

2019-08-06 06:27:00

基于FPGA的SDRAM控制器包括哪些部分呢?如何去实现一种基于FPGA的SDRAM控制器设计呢?

2021-11-04 06:47:44

请问如何将8051微控制器引到FPGA中去?

2021-04-28 06:41:17

为 STSPIN 提供的 6 步算法。我们应该将该代码移植到任何其他 ST 控制器吗?如何将BLDC进电机控制算法移植到STM微控制器上呢?

2023-01-17 08:54:28

晚上好,如何将微控制器与FPGA连接?如何使用微控制器配置FPGA?如何使用微控制器或软件程序为FPGA创建.bit文件以使用微控制器配置FPGA?任何人都可以告诉发送与这些排队相关的文件....提前致谢问候Vimala

2020-03-25 09:22:18

本文介绍通过FPGA实现的步进电机控制器。该控制器可以作为单片机或DSP的一个直接数字控制的外设,只需向控制器的控制寄存器和分频寄存器写入数据,即可实现对步进电机的控制。

2021-04-29 06:05:44

问候语!我想使用PIC18F控制器的外部并行SRAM。但是我有2个UART接口激活,我想把数据安全地送到外部SRAM。并且数据应该由控制器来计算。因此,我有3个进程必须访问SRAM。我可以整理这个

2019-04-02 09:55:26

本文介绍一种使用硬件描述语言VHDL来实现基于Petri网的并行控制器的方法。首先使用Petri网对问题进行建模,并对模型进行分析和控制,获得控制器的Petri网模型;然后用VHDL对Petri网

2019-08-16 07:52:03

国内普遍采用TM320系列的DSP器件作为永磁同步电机控制系统的主控制器,因CPU负载过重导致系统实时性降低的问题日益显著。采用具有并行工作特性的FPGA器件作为主控制器能够提高系统实时性。因此,我们具体该怎么设计呢?

2019-08-14 08:02:56

本文采用Verilog FPGA设计悬挂运动控制系统的控制器,通过输入模块传送控制参数,采用HDL语言编程实现的控制算法,驱动步进电机,对悬挂运动物体进行精确的控制。

2021-05-06 07:11:03

课程设计。俺菜鸟,时间来不及了。在这里求大神们帮忙下。求基于FPGA的uart控制器的设计和仿真用Verilog将完整的程序编写,QuartusII软件上进行仿真。这个应该不算难不过时间来不及了。q 136201727如果有的话可以发一下么第一次发帖 不知道合不合规矩请谅解

2013-04-04 14:34:48

目前我们在一个项目中使用 STM32G473CC 控制器,我们在其中使用 CAN 模块(CAN 2.0 模式)以及 UART1/LPUART1 等外围设备。我们在 CAN 驱动程序之上集成了 CAN

2022-12-12 08:29:48

如何去设计模糊PID自整定控制器?关于模糊控制器算法的研究是什么?模糊PID控制器具有哪些特点?

2021-04-21 06:08:28

基于FPGA的MCU设计有两种基本实现方式如何实现微控制器与FPGA的接口设计

2021-05-06 10:05:17

,本文的目标是介绍CRC算法的基本原理和实现方式,用到的数学尽量控制在高中生可以理解的深度。另外,鉴于大多数嵌入式程序员都是半路出家转行过来的,不少人只会C语言。因此,文中的示例代码全部采用C语言来

2016-08-01 18:32:16

和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。本文选用DSP与FPGA作为运动控制器的核心部件,设计了通用型运动控制器。其中DSP用于运动轨迹规划、速度控制

2019-07-31 08:15:26

虽说懂原理,但是这算法还不理解/*******************************************************************//**//*DS18B20

2014-04-25 15:17:17

介绍了CRC(循环冗余码校验)原理及集成混合信号片上系统单片机C8051F的新特性,推导获得以字节为单位的数据序列CRC码递推算法,利用C8051F单片机的自带CAN2.0B总线接口控制器可以很

2009-03-14 08:39:50 46

46 本文从理论上推导出CRC 算法实现原理,给出三种分别适应不同计算机或微控制器硬件环境的C 语言程序。读者更能根据本算法原理,用不同的语言编写出独特风格更加实用的CRC 计算

2009-07-20 15:27:14 32

32 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。UART 的波特率可设置调整,工作状态可读取。系统结构进行了模块化分解,使之适应自顶向下(Top-Down)的设计

2009-08-21 11:35:03 52

52 CRC算法原理及C语言实现:本文从理论上推导出CRC 算法实现原理,给出三种分别适应不同计算机或微控制器硬件环境的C 语言程序。读者更能根据本算法原理,用不同的语言编写出独特

2009-09-23 23:38:50 31

31 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 威廉希尔官方网站

,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 针对工业控制系统中的特殊应用,提出利用CRC校验方法提高通信可靠性,并着重介绍了CRC校验原理及在工业控制网络中的实现方法,重点阐述了查表法的CRC实现,同时给出余式项的生成

2011-04-03 19:30:07 46

46 为了实现军航管制系统中雷达数据的可靠传输,根据 HDLC 协议的帧结构和循环冗余校验(CRC)原理,提出了一种新型的基于并行机制的HDLC协议控制器,讨论采用FPGA新威廉希尔官方网站

实现HDLC协议帧的构成

2011-07-20 16:17:50 93

93 循环冗余码校验 CRC (Cyclic Redundancy Check) 广泛用于通讯领域和数据存储的数据检错。基于FPGA在通讯领域和数据存储的应用越来越广泛,CRC的编码解码模块已经是FPGA上的常用模块了。采

2011-08-15 11:19:57 40

40 针对大数据量的串口间通信,在常规的UART串行数据通信的基础上,结合Cortex-M3微控制器中DMA控制器的作用,实现DMA控制的UART串口数据包收发。设计链表项缓存,最终实现DMA的分散/聚集

2012-04-20 10:54:07 46

46 基于解决Xmodem协议中CRC校验的目的,以经典的LFSR硬件电路为基础,采用了按字节并行运算CRC校验码,以及多字节CRC算法的方法。在Quartus II环境下,通过以VHDL语言仿真试验,得出Xmodem协

2012-05-07 15:29:01 47

47 设计了一种基于DSP与FPGA的运动控制器。该控制器以DSP为控制核心,用FPGA构建运动控制器与传感器以及电机驱动器的接口电路。充分发挥了DSP强大的运算能力和FPGA的并行处理能力。具有

2012-10-26 15:21:51 93

93 在介绍CRC校验原理和传统CRC32串行比特算法的基础上,由串行比特型算法推导出一种CRC32并行算法。并结合SATAⅡ协议的要求,完成了SATAⅡ主控制器设计中CRC生成与校验模块的设计。最后

2012-11-07 16:19:37 54

54 运用低功耗C0rtex-M3微控制器STM32F103VBT6和FPGA芯片设计一种基于CAN总线的运动控制器。介绍系统的体系结构、主要硬件设计和软件结构。利用FPGA高速处理能力实现控制算法,与外界通信采

2013-01-31 14:33:39 45

45 介绍了一种基于FPGA的多轴控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外围电路组成,用于同时控制多路电机的运动。利用Verilog HDL 硬件描述语言在FPGA中实现了电机控制逻

2013-04-27 16:23:11 82

82 基于 FPGA的LCD控制器设计的论文。

2015-10-29 14:05:37 17

17 利用查表法实现CRC算法,CRC算法广泛应用与各行业,查表法实现CRC简单快速方便

2016-01-06 11:29:49 15

15 Xilinx FPGA工程例子源码:在FPGA上实现CRC算法的程序

2016-06-07 15:07:45 28

28 基于FPGA的LED屏控制器设计基于FPGA的LED屏控制器设计

2016-06-21 17:56:39 50

50 基于FPGA的嵌入式多核处理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 16位CRC校验原理与算法分析,感兴趣的小伙伴们可以看看。

2016-10-10 14:55:44 10

10 针对高速网络通信中高位宽并行数据的实时校验需求,提出了一种可单周期实现的、面向128位并行数据的循环冗余校验算法(Cyclic Redundancy Check,CRC )。该算法首先根据CRC

2017-10-30 16:39:25 3

3 。CRC的实现方式分为串行方式和并行方式,由于并行方式一个时钟周期内可以处理8个bit,与千兆以太网的C;MIl接口协议相符合,故千兆以太网的CRC校验码的生成和校验中常使用并行算法实现。本文研究了CRC校验码的串行实现算法和并行实现算法,并且

2017-11-13 14:20:47 12

12 传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09:04 0

0 实现RS-232电平和TTL/CMOS电平转换可以用接口芯片来实现,实现数据的串行到并行转换用的是UART,它们是实现串行通信必不可少的两个部分。虽然目前大部分处理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

介绍了CRC(循环冗余码校验)原理及集成混合信号片上系统单片机C8051F的新特性,推导获得以字节为单位的数据序列CRC码递推算法,利用C8051F单片机的自带CAN2.0B总线接口控制器可以很方便

2019-12-17 16:09:41 17

17 UART作为RS232协议的控制接口得到了广泛的应用,将UART的功能集成到FPGA芯片中,可使整个系统更为灵活、紧凑,减小整个电路的体积,提高系统的可靠性和稳定性。提出了一种基于FPGA

2020-07-07 15:51:05 7

7 UART作为RS232协议的控制接口得到了广泛的应用,将UART的功能集成到FPGA芯片中,可使整个系统更为灵活、紧凑,减小整个电路的体积,提高系统的可靠性和稳定性。提出了一种基于FPGA的UART

2020-07-07 17:28:03 10

10 为了实现军航管制系统中雷达数据的可靠传输,根据HDLC协议的帧结构和循环冗余校验(CRC)原理,提出了一种新型的基于并行机制的HDLC协议控制器,讨论采用FPGA新威廉希尔官方网站

实现HDLC协议帧的构成

2020-11-04 18:04:10 15

15 出了四核心嵌入式并行处理器FPEP的结构设计并建立了FPGA验证平台.为了对多核处理器平台性能进行评测,提出了基于OpenMP的3种可行的图像处理领域的经典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 在数据通信中, 提高数据在通信中的可靠性,以及快速的数据处理能力一直是人们所追求的,循环冗余校验CRC就是一种广泛采用的差错控制方法,也是一种最常用的信道编码方法。在介绍CRC码原理之后,以经典

2021-03-10 15:50:00 14

14 的高速CRC并行吏现递推公式,可适用于并行处理位宽小于等于生成多项式阶数和大于生成多项式阶数条件下的并行帧校验应用。最后分别设计了这2种条件下的硬件实现电路,电路的综台结果表明,该方法具有更步的资源占用量和更高的工作

2021-03-23 15:44:59 13

13 CRC校验的实现基于串行位移寄存器,如果要处理并行数据,需要对电路进行改进。本文介绍了一种并行CRC电路HDL代码的快速生成钟算法,只需要带入不同的参数,可自动生成不同长度以及并行度的并行CRC电路的HDL代码。

2021-03-28 09:29:50 15

15 文章介绍了用于 USB 总线数据传输的CRC 校验的原理和算法,并且采用并行电路实现 USB2.0 中的 CRC产生和CRC校验,与传统的串行电路实现相比,并行电路实现方法虽然在芯片面积上大于串行电路实现, 但由于降低了时钟频率,电路更容易综合实现,并且大大降低了功耗,有利于低功耗电路设计。

2021-03-28 09:32:27 11

11 用软件实现 CRC 校验码计算很难满足高速数据通信的要求 ,基于硬件的实现方法中 ,有串行经典算法 LFSR 电路 以及由软件算法推导出来的其它各种并行计算方法。以经典的LFSR 电路为基础 ,研究

2021-03-28 09:34:24 30

30 EE-296:在SHARC®处理器上使用UART端口控制器

2021-04-26 10:19:17 2

2 CRC校验算法原理及c语言实现

2021-11-30 10:04:07 8

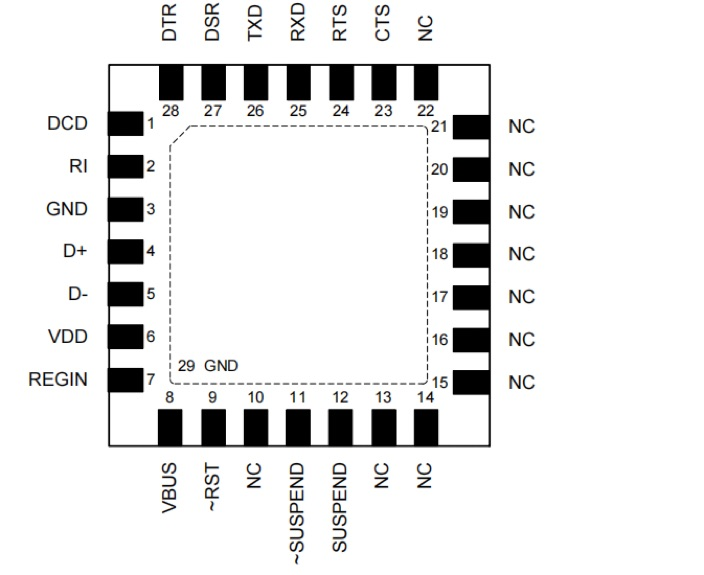

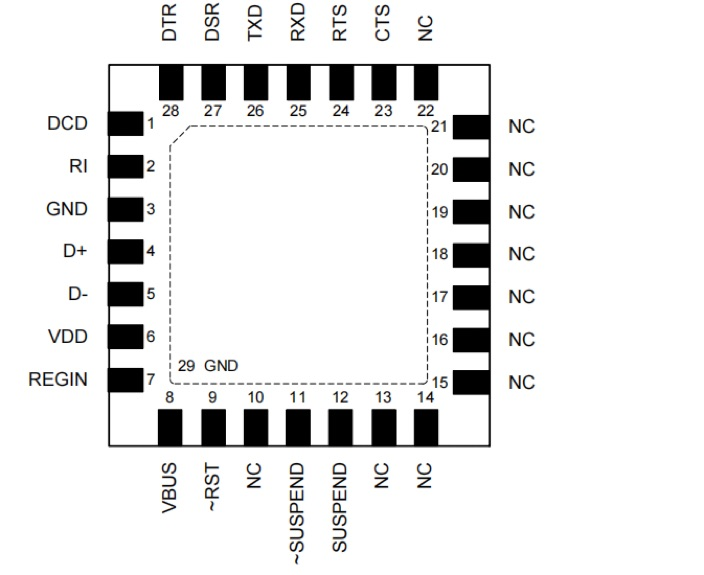

8 DPU02是一个高度集成的USB转UART的桥接控制器,可将RS-232设计更新为USB设计,并简化PCB组件空间。

2022-12-16 11:53:14 716

716

摘要:本文从一已提出的通用数学表达式出发,研究了一种并行循环冗余校验(CRC)计算的新算法,该算法是一种迭代算法,可以逐步更新校验序列,适用于CRC计算的各种参数选择。这一算法适合硬件实现。其仿真

2023-02-21 09:45:49 0

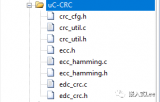

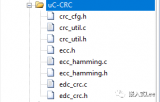

0 我们这一篇来讲讲Micrium全家桶的uC-CRC。该代码库提供了CRC算法进行错误检测EDC,使用HAMMING算法实现ECC错误纠正。

2023-05-04 10:47:44 509

509

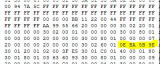

CRC循环冗余逆向算法顾名思义就是将左边的数据看作低位,右边的数据看作高位。这样的话需要在g的左边加m个0,h也要逆向,例如正向CRC-16算法h=0x4c11db8,逆向CRC-16算法

2023-05-06 14:33:39 397

397 常用的校验方法,用于检测和校正数据传输中的错误。在FPGA设计中,CRC故障指的是与CRC相关的错误或问题。 首先,让我们了解CRC是什么以及它在数据传输中的作用。CRC是一种基于二进制算法的校验

2024-01-04 11:06:15 308

308 FPGA 在比特流被加载时计算 CRC 值,然后该值与在比特流加载结束时预期的 CRC 值进行比较。如果两个值匹配,则FPGA 成功加载。

2024-02-28 14:58:34 99

99

电子发烧友App

电子发烧友App

评论