针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

8153 本文描述了复位的定义,分类及不同复位设计的影响,并讨论了针对FPGA和CPLD的内部自复位方案。

2016-07-11 14:33:49 6228

6228

大家好,博主最近有事忙了几天,没有更新,今天正式回来了。那么又到了每日学习的时间了,今天咱们来聊一聊 简谈FPGA的上电复位,欢迎大家一起交流学习。 在基于verilog的FPGA设计中,我们常常

2018-06-18 19:24:11 19894

19894

随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。 我们的复位

2019-02-20 10:40:44 1068

1068

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 1461

1461

前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数

2020-11-16 11:42:00 7655

7655

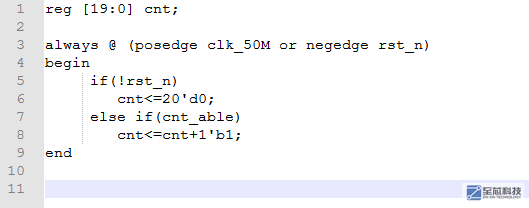

: ① 首先,上电后肯定是要复位一下,不然仿真时会出现没有初值的情况; ② 最好有个复位的按键,在调试时按一下复位键就可以全局复位了; ③ 也许是同步复位,也许是异步复位,不同的工程师可能有不同的方案

2020-11-18 17:32:38 3110

3110 作者:NingHeChuan Get Smart About Reset: Think Local, Not Global。 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间

2020-12-25 12:08:10 2303

2303

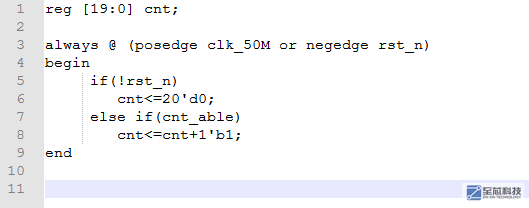

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 1679

1679

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 1701

1701

6月12日,日经新闻引述未具名消息人士报导,合肥长鑫已经重新设计了其DRAM芯片,以尽量减少对美国原产威廉希尔官方网站

的使用。 日经:长鑫已重新设计DRAM芯片,尽量避免使用美国原产威廉希尔官方网站

据日经新闻亚洲评论报导

2019-06-13 18:30:03 3232

3232 为硬件电路

二:代码优化技巧

1.使用“<=”代替“.=”,后者会生成组合逻辑,前者只生成时序逻辑,减小功耗

2.尽量避免同步复位,如有需要可以使用异步复位

3.避免使用不必要的中间变量

2023-11-08 15:25:25

大家好!又到了每日学习的时间了,今天我们聊一聊FPGA做开发的时候,有哪些设计规范,从文档到工程建立等,聊一聊也许你会学到很多东西,少走很多弯路哦!在团队项目开发中,为了使开发的高效性、一致性

2018-02-24 15:58:03

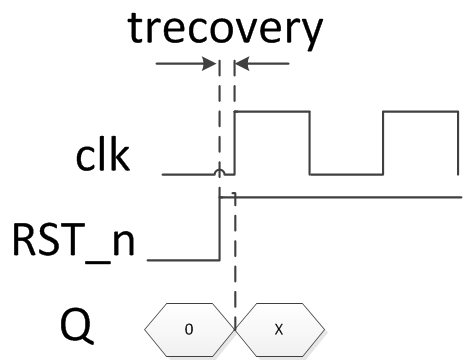

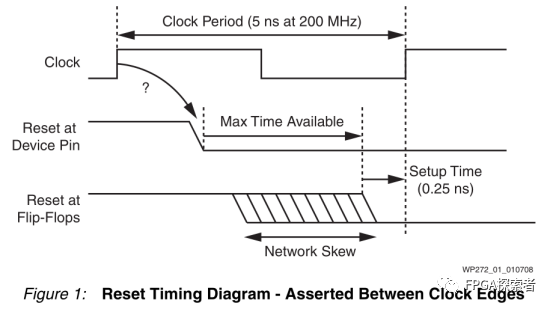

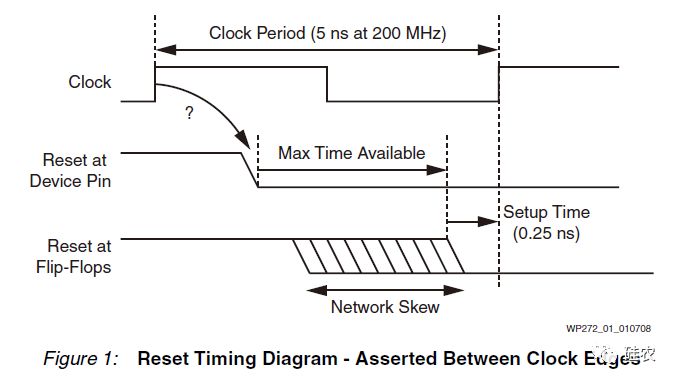

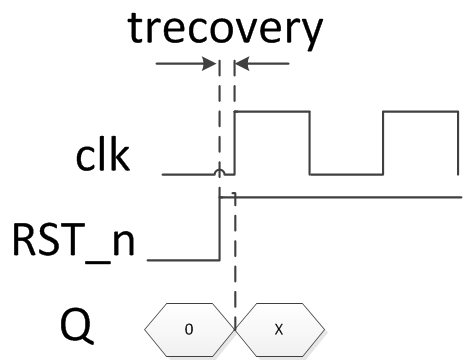

在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器

2020-10-22 11:42:16

FPGA的全局时钟是什么?什么是第二全局时钟?在FPGA的主配置模式中,CCLK信号是如何产生的?

2021-11-01 07:26:34

和removal时序检查;异步复位同步撤离(推荐使用) 优点:能避免纯异步或纯同步复位的潜在问题。它是FPGA设计中最受欢迎的复位,Altera建议使用这种复位方法。这种复位在使用前需要同步到各个使用时

2014-03-20 21:57:25

设计中充分利用资源 ,因为 大部分 FPGA 器件都为时钟、复位、预置等信号提供特殊的全局布线资源,要充分利用这些资源。

6、在设计中 不论是控制信号还是地址总线信号、数据总线信号,都要采用另外的寄存器

2024-02-21 16:26:56

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

FPGA的任意一个管脚都可以作为时钟输入端口,但是FPGA专门设计了全局时钟,全局时钟总线是一条专用总线,到达片内各部分触发器的时间最短,所以用全局时钟芯片工作最可靠,但是如果你设计的时候时钟太多

2012-02-29 09:46:00

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们也

2019-04-12 06:35:31

应的: a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。 b、设计相对简单。 c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。 缺点: a、在复位

2011-11-04 14:26:17

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们

2015-04-10 13:59:23

,通过这些专用引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA

2015-04-24 08:17:00

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输出关联的系统产生不良影响,FPGA上电后要进行复位,且为了消除电源开关过程中引起的抖动影响,复位

2021-06-30 07:00:00

一些组合逻辑的优化;例如对于A|B我们可以将A直接与触发器的输入端相连,而B与触发器的置位段相连,这样就节省了一个或门。6.对于面积要求比较紧的电路应尽量避免复位和置位。`

2014-12-04 13:52:40

一些注意事项:全局变量和局部变量重名以后,根据就近原则,打印会显示局部变量的值,可在变量前加入::代表全部变量;应减少不必要的全部变量,尽量利用其他变量去替代;变量在声明时初始化可以减少程序

2021-12-15 06:10:42

之内,触发器的输出端的值将是不确定的,可能是高电平,可能是低电平,可能处于高低电平之间,也可能处于震荡状态),并且在未知的时刻会固定到高电平或低电平。这种状态就称为亚稳态。反映到仿真模型中,输出端的值

2012-01-12 10:45:12

亚稳态概述01 亚稳态发生原因在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足

2020-10-19 10:03:17

1、在FPGA中实现串口协议的设计在FPGA中实现串口协议,通过Anlogic_FPGA开发板上的“UART2USB”口接收从计算机发来的数据。实验设计思路UART串口是一种类似于USB、VGA

2022-07-19 11:09:48

产生的问题是在FPGA上电启动时这部分引脚总是会快速的闪过一次高电平才恢复低电平,请问应该怎么做才能使避免高电平会闪一次的这种情况?程序中因为需要复位时保持输出结果,所以不能使用复位信号,关键代码

2023-04-23 14:53:05

在FPGA的开发中,如何对inout信号进行赋值?

2023-04-23 14:25:00

通过SYS_INT_.ble()函数禁用全局中断。我的设备有一个LCD显示器,它通过EBI连接,并且通过DMA进程不断更新。此时,当执行NVM块写入操作时,LCD闪烁(一次)。我们希望避免在显示器上出现

2019-09-24 13:36:26

教大家一个如何在头文件中定义全局变量的方法 通常情况下,都是在C文件中定义全局变量,在头文件中声明,但是,如果我们定义的全局变量需要被很多的C文件使用的话,那么将全局变量定义在头文件里面会方便

2018-07-04 08:34:47

教大家一个如何在头文件中定义全局变量的方法 通常情况下,都是在C文件中定义全局变量,在头文件中声明,但是,如果我们定义的全局变量需要被很多的C文件使用的话,那么将全局变量定义在头文件里面会方便

2018-07-09 09:25:50

用什么代替全局变量传递参数

2023-11-02 07:35:00

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-11 06:06:08

一般来说,编程时我们应该尽量减少使用全局变量,但是在DSP程序中,我们是不是应该也要尽量减少使用全局变量?

2018-12-11 13:50:55

间序列中,专用的全局复位GSR将复位FPGA中的所有寄存器。众所周知,GSR是不可见的,不能在用户的VHDL代码中使用。那么我们如何在VHDL代码中分配寄存器信号的起始值。我的意思是在正常情况下我们使用这样的重置信号:过程(clk,rst)开始 如果rst ='1'那么 regs

2019-05-22 11:40:55

本帖最后由 eehome 于 2013-1-5 09:52 编辑

MATLAB在FPGA开发中的应用

2012-03-06 17:37:48

射频、高速数字电路:禁止锐角、尽量避免直角 如果是射频线,在转角的地方如果是直角,则有不连续性,而不连续性将易导致高次模的产生,对辐射和传导性能都有影响。RF信号线如果走直角,拐角处的有效线宽

2018-09-21 11:48:34

STM8的独立看门狗在使用的过程中怎么避免复位

2023-10-11 07:32:15

您好Xilinx社区,有人能否就Spartan-6 FPGA是否需要设计中的上电复位电路给出明确的答案?在附图中,我们的设计中有这个上电复位电路。然而,我们遇到了电路问题,并决定在我们的设计中将

2019-04-18 10:15:45

可能就应尽量在设计项目中采用全局时钟。 CPLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。 在许多应用中只将异步信号同步化还是

2012-03-05 14:29:00

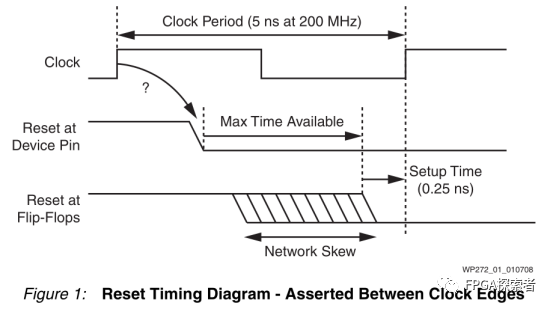

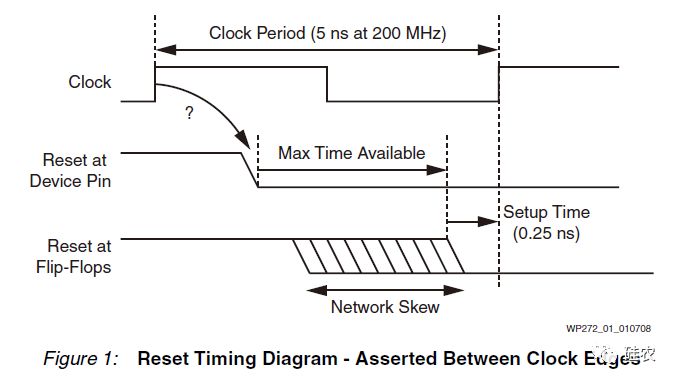

尽管复位方案极其重要,可是却是最被忽视的部分之一,许多设计人员认为FPGA的全局复位资源将会完全解决问题,这是完全不正确的。至于为何说复位的重要性极高,是因为复位方案不好会引起不可重复的错误,而不可

2012-12-05 17:09:26

同步单元的起始状态或者将要返回的状态是一个已知状态(罗辑‘1’或者‘0’)就显得非常重要。在程序中,往往都在端口定义中使用同一个rst_n信号,通常的同步电路通常是由两种复位方式来进行电路的复位,即

2015-06-07 20:39:43

延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们也需要注意以下几个要点:● 尽可能

2016-07-25 15:19:04

引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位

2016-08-08 17:31:40

复位与时钟电路示意图 如图2.10所示,原理图上示意,我们所使用的FPGA器件共有8个专用时钟输入引脚,在不做时钟输入引脚功能使用时,这些引脚也可以作为普通I/O引脚。如我们的电路中,只使用了

2017-10-23 20:37:22

FPGA:xc7v585tffg1761就像时钟一样,有很多GCLK引脚。我不知道它是否有全局复位引脚。谢谢

2020-06-17 08:07:03

根据一些WP文档,最佳编码实践不是尽可能使用全局重置?这里有一个问题,如果没有复位引脚,如何复位FPGA,每次想要复位时都要关闭FPGA!以上来自于谷歌翻译以下为原文According

2019-04-18 14:19:27

任务的特殊网络 - 全局设置/重置。配置完成后,该线路被置低,以允许FPGA开始其新编程的功能。假设这是正确的,那么我理解。在我的VHDL中,如果我有一个简单的顶级模型,其中一个进程对时钟和复位信号很

2019-05-17 11:24:19

=11.818181991577148px]2、对于有些系列的FPGA的LE 有 同步复位,同步置位端,这种情况使用同步复/置位,比较省资源,但是对于没有同步复位端的FPGA,在程序中使用同步复/置位

2014-08-13 16:07:34

信号列表中列出所有的输入信号。

(8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

(9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式

2023-05-23 18:15:44

尽量用局部变量替代全局变量。如果用局部变量能实现功能,最好用局部变量。在函数仅仅只是要用到某个全局变量,而无需改动时,就将全局变量通过形参传递进来,变成局部变量使用。并在定义时使用const。这是

2022-02-28 06:22:20

,SDIO 引脚 10K电阻 拉低 ,Reset 引脚 10K 电阻 拉低,且四个引脚均与FPGA 相连接),上电瞬间,对其进行复位操作,本身使用芯片的normalmode, 但多次上电中,会有几次

2018-07-27 06:14:03

PCB板子已经发给厂家了,改不回来了,真是怪自己还没优化好程序,就急急忙忙的把板子发出去了。 复位信号必须接到Libero soc支持的芯片的全局引脚,我接到了个普通IO,在开发环境中分配引脚

2018-01-07 22:31:39

斑梨电子FPGA CycloneII EP2C5T144 学习板 开发板产品参数1. 采用ALTERA公司的CyclonellEP2C5T144芯片作为核心最小系统,将FPGA

2023-02-03 15:14:29

Intel Agilex® F系列FPGA开发套件Intel Agilex® F系列FPGA开发套件设计用于使用兼容PCI-SIG的开发板开发和测试PCIe 4.0设计。该开发套件还可通过硬核处理器

2024-02-27 11:51:58

FPGA的全局动态可重配置威廉希尔官方网站

主要是指对运行中的FPGA器件的全部逻辑资源实现在系统的功能变换,从而实现硬件的时分复用。提出了一种基于System ACE的全局动态可重配置设计方法,

2011-01-04 17:06:01 54

54 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 电源、时钟和复位电路图(Altera FPGA开发板)如图所示:

2012-08-15 14:42:33 9398

9398

好消息是,在绝大多数设计中(白皮书说是超过99.99%?应该是老外写文档的习惯吧),复位信号的时序是无关紧要的——通常情况下,大部分电路都能够正常工作。

2017-02-11 11:07:33 356

356

在某种意义上讲,这是一个上电之后的“终极的”全局复位操作,因为它不仅仅是对所有的触发器进行了复位操作,还初始化了所有的RAM单元。

2017-02-11 11:09:11 484

484

在FPGA设计中,我们往往习惯在HDL文件的端口声明中加入一个reset信号,却忽略了它所带来的资源消耗。仔细分析一下,竟会有如此之多的影响:

2017-02-11 11:09:11 951

951 最近几天读了Xilinx网站上一个很有意思的白皮书(white paper,wp272.pdf),名字叫《Get Smart About Reset:Think Local, Not Global》,在此分享一下心得,包括以前设计中很少注意到的一些细节。

2017-02-11 11:45:36 1254

1254 在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 10969

10969 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 10154

10154 xilinx推荐尽量不复位,利用上电初始化,如果使用过程中需要复位,采用同步高复位。

2019-02-14 14:29:49 5419

5419 复位信号设计的原则是尽量不包含不需要的复位信号,如果需要,考虑使用局部复位和同步复位。

2019-10-27 10:09:53 1735

1735

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

FPGA开发中,一种最常用的复位威廉希尔官方网站

就是“异步复位同步释放”,这个威廉希尔官方网站

比较难以理解,很多资料对其说得并不透彻,没有讲到本质,但是它又很重要,所以对它必须理解,这里给出我的看法。

2020-08-18 13:56:00 1114

1114

DFF 都有异步复位端口,因此采用异步复位可以节约资源。 ⑵设计相对简单。 ⑶异步复位信号识别方便,而且可以很方便地使用 fpga 的全局复位端口。 缺点:⑴在复位信号释放时容易出现问题,亚稳态。 ⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原

2020-10-30 12:17:55 323

323 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11527

11527

接触FPGA的朋友们都知道“复位”,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题。

2021-04-03 09:34:00 7995

7995 基于FPGA的小波滤波抑制复位噪声方法

2021-07-01 14:42:09 24

24 。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-06 09:20:57 20

20 在这些情况下,复位信号的变化与FGPA芯片内部信号相比看起来是及其缓慢的,例如,复位按钮产生的复位信号的周期至少是在毫秒级别的,而我们FPGA内部信号往往是纳米或者微秒级别的。

2022-05-06 10:48:45 2462

2462 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 1585

1585 FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 806

806 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 3347

3347

SoC设计中通常会有“全局”同步复位,这将影响到整个设计中的大多数的时序设计模块,并在同一时钟沿同步释放复位。

2023-05-18 09:55:33 145

145

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。

2023-05-22 14:21:08 577

577

本文将探讨在 FPGA 设计中添加复位输入的一些后果。 本文将回顾使用复位输入对给定功能进行编码的一些基本注意事项。设计人员可能会忽略使用复位输入的后果,但不正确的复位策略很容易造成重罚。复位

2023-05-25 00:30:01 483

483 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 2110

2110

尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

2023-06-21 09:55:33 1337

1337

对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。

2023-06-21 10:39:25 651

651

能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值

2023-06-28 14:44:46 526

526

电子发烧友App

电子发烧友App

评论