DDR31.DDR3概述DDR3内存控制器主要用于以JESD79-3C标准做SDRAM设备的外部存储接口。支持的内存类型有DDR1 SDRAM,SDRSDRAM, SBSRAM。DDR3内存控制器

2018-01-18 22:04:33

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:50:27

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:55:45

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条,笔记本

2009-08-17 23:00:19

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

。为了充分利用和发挥DDR3存储器的优点,使用一个高效且易于使用的DDR3存储器接口控制器是非常重要的。视屏处理应用就是一个很好的示例,说明了DDR3存储器系统的主要需求以及在类似数据流处理系统中

2019-05-24 05:00:34

DDR3存储器接口控制器是什么?有什么优势?

2021-04-30 06:57:16

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

4的JEDEC标准DDR4接口的变体,它包含了对完整系统支持所需的独特功能。本文将帮助工程师了解Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2021-01-15 06:08:20

modelsim仿真DDR3时,出现下面错误。Instantiation of 'B_MCB' failed. The design unit was not found.并没有用ISE联合仿真

2016-01-21 10:12:40

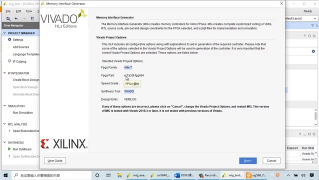

”。13.点击“Generate”生成MIG控制器。四、生成文档点击“Generate”,生成MIG控制器相关的设计文档。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置过程。

2019-12-19 14:36:01

看完保证你会做DDR3的仿真

2015-09-18 14:33:11

xilinx平台DDR3设计教程之仿真篇

2020-03-12 08:54:20

xilinx平台DDR3设计教程之设计篇_中文版教程3

2023-08-05 18:39:58

“你能不能实现一个理想情况下应该在每个时间片开始时执行的监控任务,并确定前一个时间片的利用率。如果利用率过高,则应发出警告。如果我们可以使用空闲时间,那么我们就可以衡量利用率。为了设置这个监视器

2022-12-06 06:00:31

要计算当前CUP利用率,是不是就使能OS_TASK_STAT_EN就可以了,并不要单独建立一个任务去执行OSTaskStat(),是这样吗?参看战舰例程,没有找到哪里执行了OSTaskStat()!

2020-05-18 22:05:37

(flight-time skew)来降低共同切换噪声(SSN)。走线摆率可以达到0.8tCK,这个宽度导致无法确定在哪两个时钟周期获取数据,因此,JEDEC为DDR3定义了校准功能,它可以使控制器

2019-04-22 07:00:08

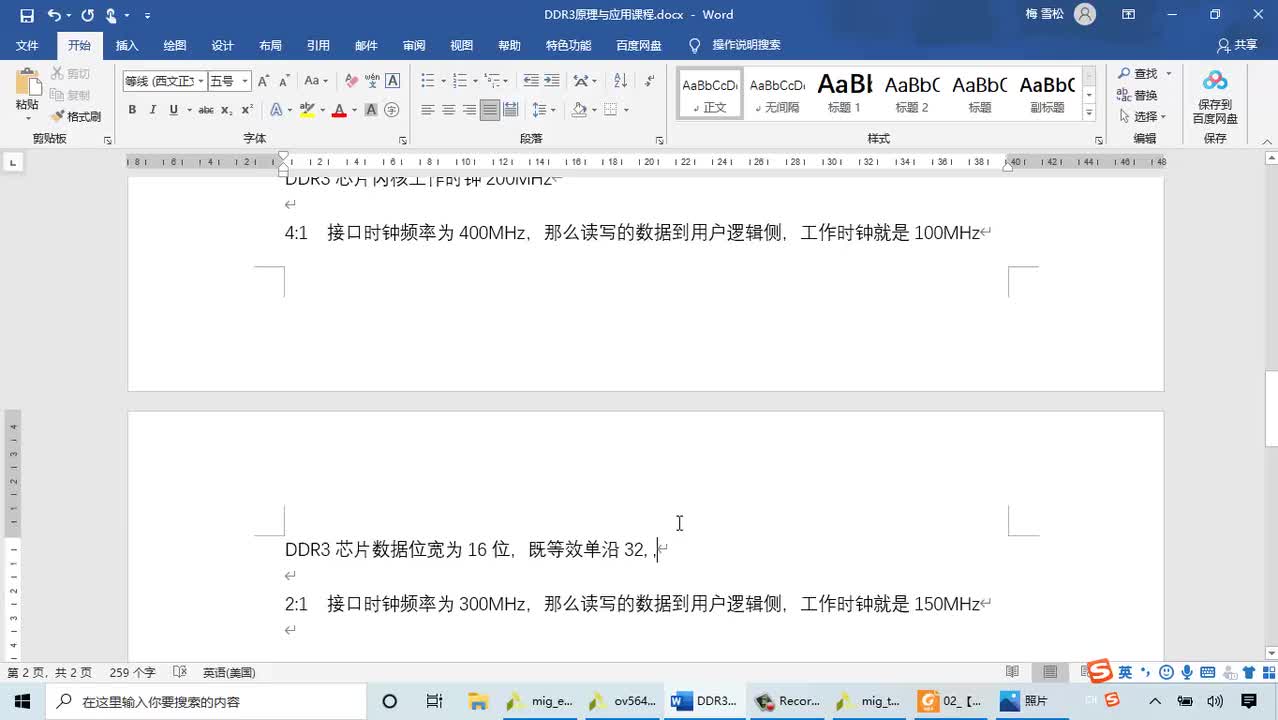

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

嗨,Post综合后的利用率只不过是实施后的利用率......?谢谢娜文G K.

2020-05-12 08:57:23

空闲线程中做运算,即利用率视为0%影响计算精度的问题:调度锁只把调度器关了,中断依然可以正常抢占,如systick会1ms打断一次,如果一个线程执行时间超过1ms,则会被systick打断,那么本次计算

2022-05-13 15:27:45

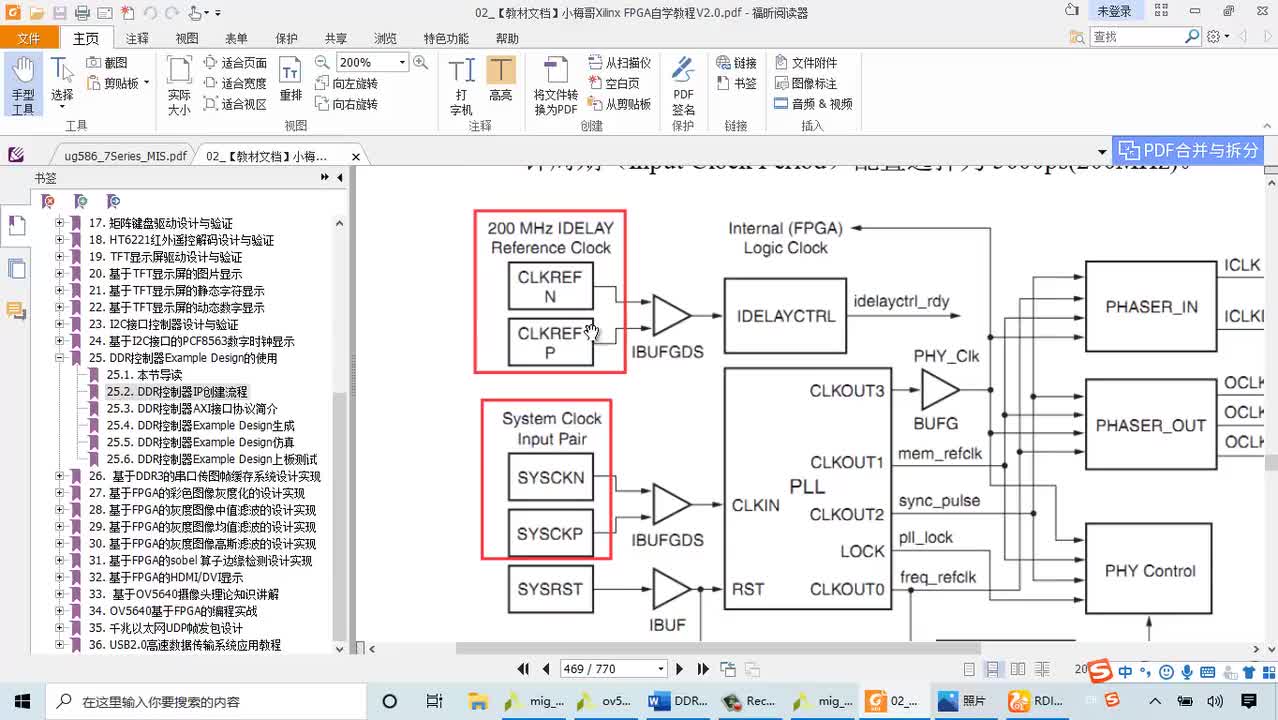

6655时钟PLL配置与DDR3的配置1 时钟概述PLL与PLL控制器的逻辑组成和处理流程如图1所示。PLL控制器能够通过PLLDIV1到PLLDIV16这些分频器灵活便利的配置和修改内部的时钟信号

2018-01-24 21:27:10

整机功耗过高风险,需实时监测功耗变化,进行针对性的功耗压制。L3/MB 控制:当前底层硬件提供了 L3 缓存和内存带宽隔离能力,但仍需软件动态控制,以实现干扰控制和资源利用率的平衡。「资源隔离

2022-07-06 09:54:19

你好,我使用的是Vc707板,14.5 ISE DS。在XPS项目的开发过程中,我遇到了ddr3内存接口的问题。在我的XPS设计中(基于Xilinx网站上提供的参考vc707 BIST项目)软件

2019-09-09 10:20:26

你好。我最近第一次对待Vivado。我想使用DDR3内存和IDELAYE2。该设备是Kintex-7。当我一起使用DDR3控制器和IDELAYE2时发生错误,并且无法形成位文件。当我丢失

2020-08-20 09:40:23

& 14用于DDR3内存接口,但由于我使用的是3.3V的fash存储器IC,我必须使用bank 14进行闪存存储器接口。原因是需要的资源仅在Bank 14中可用.DDR3存储器连接的bank应该工作在

2020-04-17 07:54:29

。为了充分利用和发挥DDR3存储器的优点,使用一个高效且易于使用的DDR3存储器接口控制器是非常重要的。视屏处理应用就是一个很好的示例,说明了DDR3存储器系统的主要需求以及在类似数据流处理系统中

2019-05-27 05:00:02

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

设计,简化了DDR3多通道读写的复杂度,随着有效数据周期的提升,最高端口速率可达5.0 GB/s以上,带宽利用率可达80%以上。1 总体设计架构本文所设计的六通道读写防冲突总体架构如图1所示,主要包括通道判

2018-08-02 09:32:45

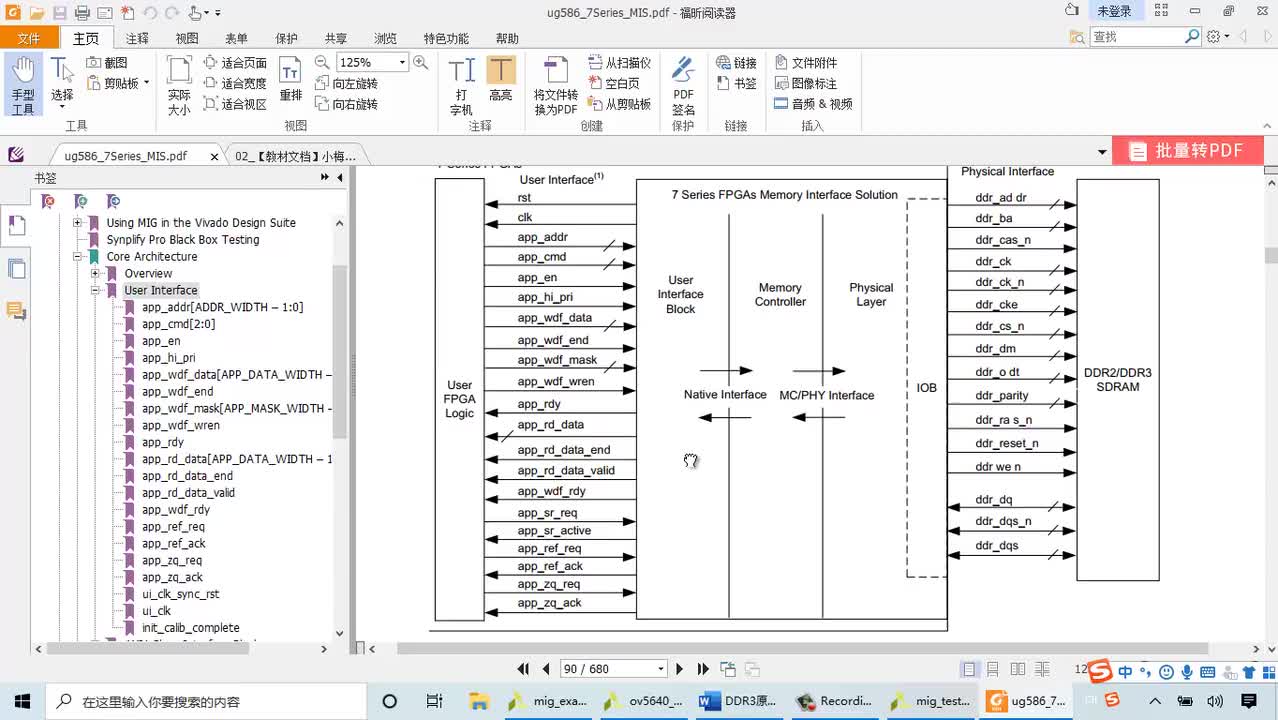

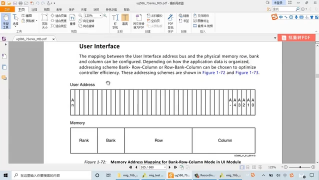

1 DDR3存储管理系统设计框图DDR3存储器控制模块采用Xilinx公司的MIG[4](Memory Interface Generator)方案,通过用户接口建立FPGA内部控制逻辑到DDR3

2018-08-02 11:23:24

12位,扩展成16位后进行存储,DDR3内部以1067M处理速度,32位的处理带宽进行存储,写数据时从地址全0写到地址全1,读数据时也从地址全0读到全1,经对比无误,说明该控制器能够较好地进行高速读写操作。`

2018-08-30 09:59:01

冒昧的问一下各路大神,假如我们利用UCOSII中的统计任务 OS_TaskStat()知道了CPU利用率100%,则应该怎样操作,把利用率降下来?另外,利用率太高的话会不会不太好?

2019-07-12 04:36:16

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

,ddr3的带宽利用率也只有20%-30%左右。这里就觉得比较纠结。burst length太大,frame buffer的输出端当要对输入的视频帧进行截取一部分的时候会变相降低DDR3带宽利用率,这样

2015-08-27 14:47:57

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

嗨,我已将Xilinx CDMA(中央DMA控制器)连接到EDK项目。现在我需要使用SDK中的C程序来测试它。我的项目中有DDR3和BRAM。如何编写C程序通过CDMA将DDR3数据写入BRAM

2019-02-18 09:57:56

如何获取栈利用率?

2022-02-16 07:34:32

旁边的数字意味着什么的文档和资源的指针?具体来说:1)它们各自意味着什么?,2)它们是在VHDL代码中明确使用的,还是选择了ISE(例如DSP48的数量)来实现我的设计?3)如果我的设计在上面100%的资源利用率,如何更改我的VHDL代码以依次减少每个资源的使用?谢谢!

2020-03-24 10:14:15

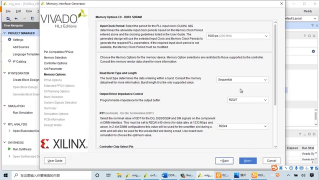

大家好,我试图通过vivado v14.3生成DDR3控制器。我正在选择DDR3 SODIMM模块“MT8KSF1G72HZ-1G6”。该工具支持该器件,最高频率可达666.66MHz,但该模块的数据表明最高频率可达800MHz。请帮我确定问题所在。感谢致敬Tarang JIndal

2020-07-31 06:07:43

你好我们计划使用XC7Z020 PS部分的DDR3内置控制器将其连接到2个芯片[MT41K128M16] -32位数据宽度。我们计划再使用一个DDR3组件来支持ECC。请告知我们XC7Z020 PS中DDR3控制器引脚的详细信息,包括ECC引脚详细信息。谢谢Pench

2020-03-24 09:34:32

嗨,大家好,我遇到了Xilinx ISE映射过程的棘手问题。当我综合我的设计时,我得到了一些FPGA资源的利用。虽然在映射过程中映射到FPGA上的LUT时,所有利用率都会达到0%。他很可能是由于

2020-06-13 09:57:50

目前有一个项目需要使用DDR3作为显示缓存,VGA作为显示器,FPGA作为主控器,来刷图片到VGA上。VGA部分已经完成,唯独这个DDR3以前没有使用过,时序又比较复杂,所以短时间内难以完成,希望做过DDR3控制器的大神指点一二。急求!!!!

2015-11-16 09:18:59

影响无线信道利用率的因素有哪些?无线利用率与网络质量间的关系是什么?调整和提高无线信道利用率的建议有哪些?

2021-05-27 06:46:55

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 要:本应用笔记说明了如何计算DS31256 HDLC控制器的总线带宽。并展示了一个实验室实测的结果。同时演示了一个总线利用率速算表,该速算表如果需要可以索要。

2009-04-18 11:24:11 1181

1181

Xilinx FPGA工程例子源码:Xilinx DDR3最新VHDL代码(通过调试)

2016-06-07 14:54:57 77

77 基于协议控制器的DDR3访存控制器的设计及优化_陈胜刚

2017-01-07 19:00:39 15

15 描述:单Bank内行切换时,每次打开一个Row,进行一次写操作以后,必须重新打开另外一个Row,才能进行该Row的写操作。两个Row打开操作有时间间隙要求,打开Row到写操作也有时间间隙要求。

2017-02-11 01:41:07 2360

2360

描述:在此项测试中,每个Bank只访问一次,接着依次访问其它Bank。DDR3有限制在一定时间内可以输入的Bank打开指令个数,即在一定时间内只允许输入最多4个Bank打开命令。

2017-02-11 01:46:30 4005

4005

为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 19504

19504

为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取

2017-11-17 14:26:43 24269

24269

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 6412

6412

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,运行速度高于1866 Mbps数据速率。

2018-11-30 06:21:00 5277

5277

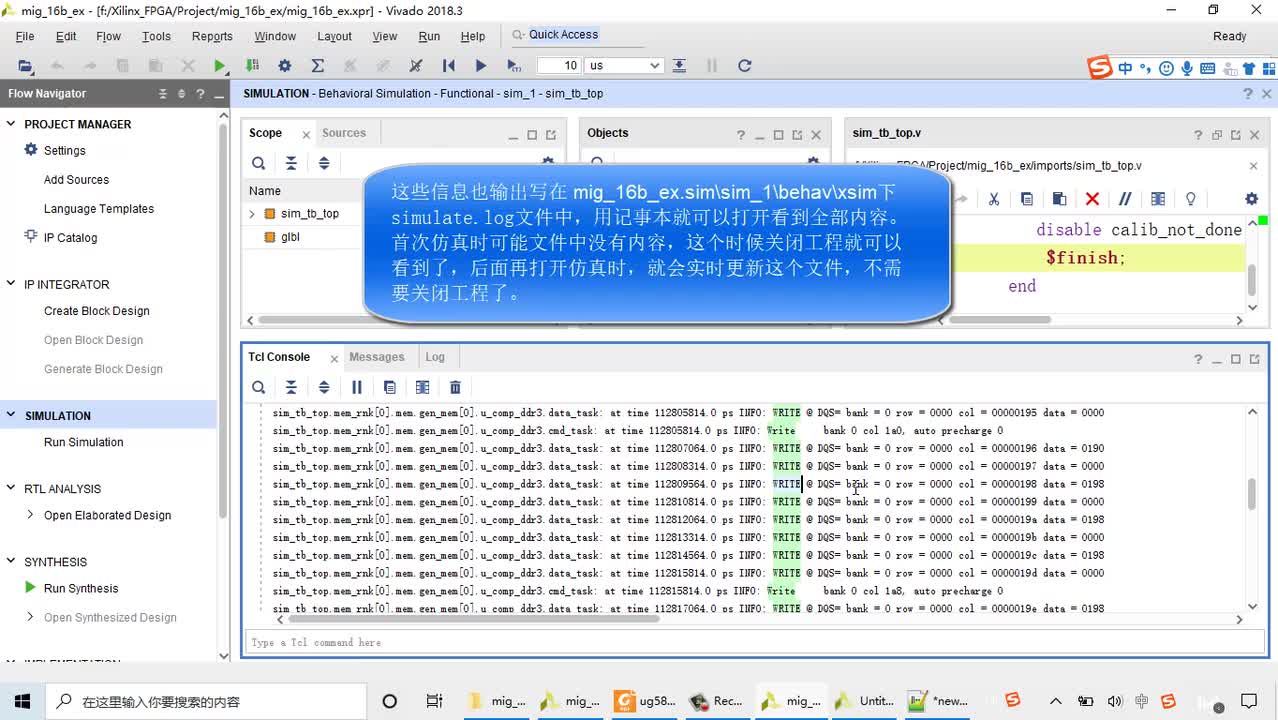

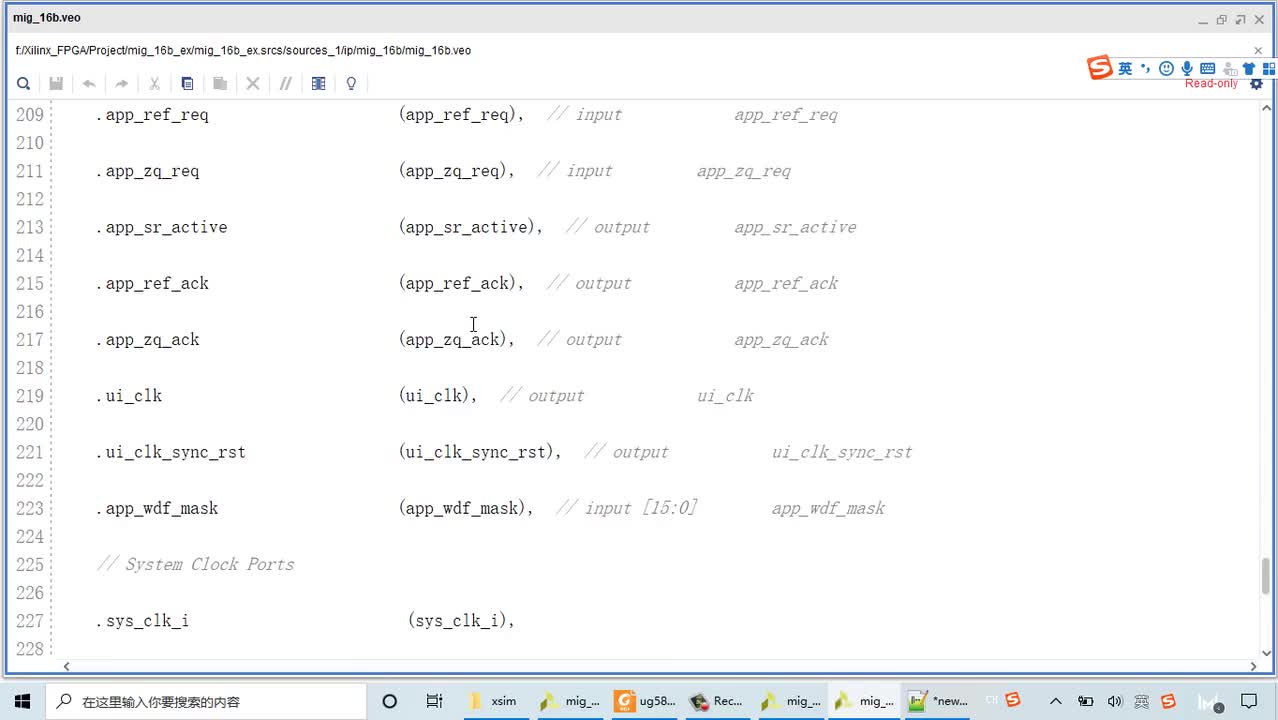

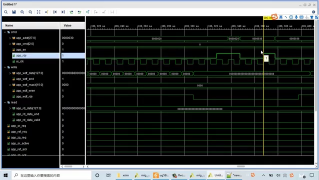

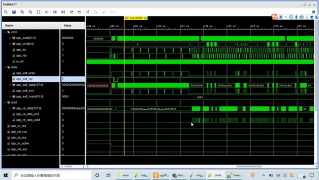

DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

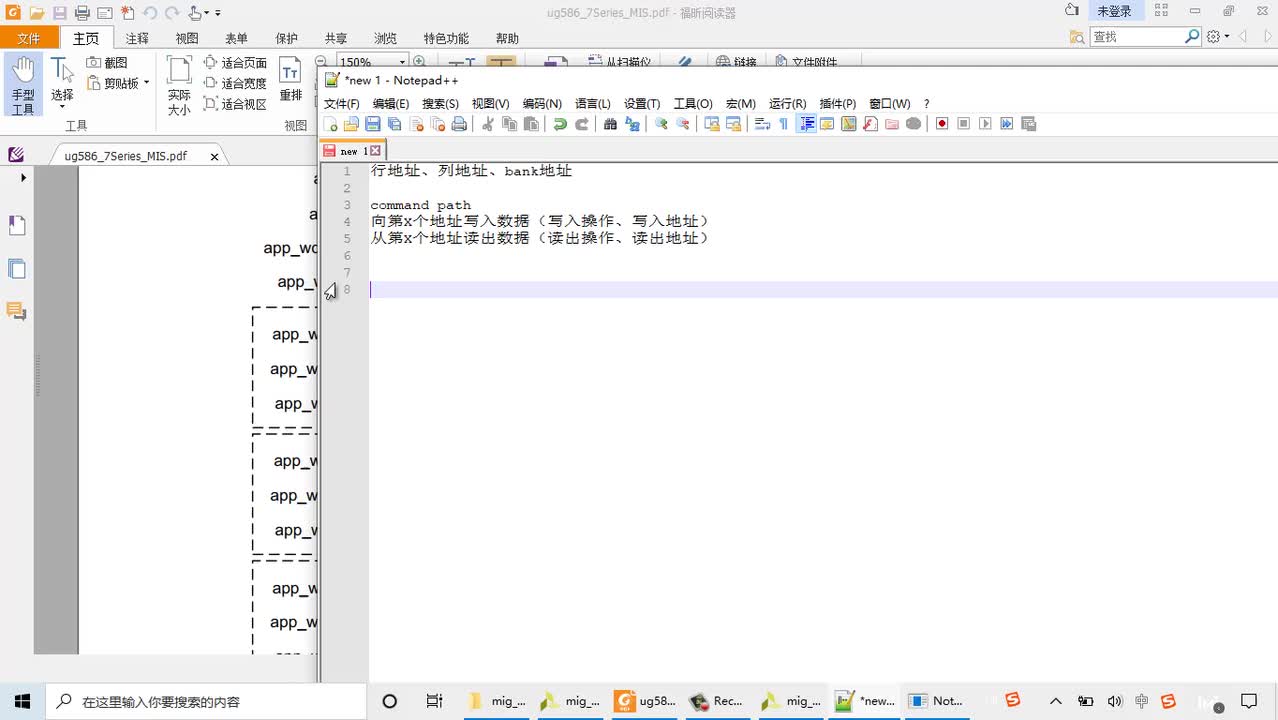

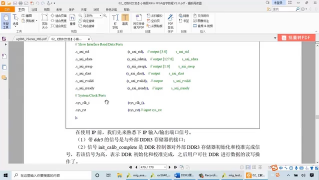

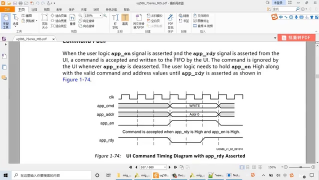

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据 Xilinx 官方提供的威廉希尔官方网站

参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28:58 1241

1241 本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1896

1896

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0

电子发烧友App

电子发烧友App

评论