本设计以FPGA为控制核心,采用直接数字频率合成(DDS)设计了一款信号可调的信号发生器,采用的FPGA是Altera公司研发的的Cyclnoe II系列,所选用的型号是EP4C6F17C8,外围

2021-10-28 16:49:26

FPGA数字信号发生器,怎么弄啊……跪求各路大神……

2013-04-18 13:38:22

时钟周期,占空比为1/2,并且在每次输出完整脉冲后输出一个系统时钟脉宽的提示信号,可见波特率发生器的工作完全满足设计的要求。图5-11波特率时钟实现原理使用测试参数仿真正常后,可以使用实际的参数进行测试。

2018-10-19 09:47:38

求助,这个信号发生器电路的设计原理是什么

2022-06-21 20:40:00

信号发生器和DA转换 FPGA案例教程

2019-08-17 09:01:48

信号发生器是是什么?信号发生器分为哪几类?

2021-05-13 06:03:51

开始加入信号发生器的大家族。 信号发生器的指标 信号发生器的工作频率范围、频率稳定度、频率精度、信号频谱纯度都与频率产生单元有关,也是信号发生器性能的重要指标。 文章来源于:日图科技 阿里巴巴直通车:深圳市日图科技有限公司 微信:Ritu-17微博:日图科技Ritu

2016-02-23 14:52:52

本文主要介绍信号发生器的基础知识,首先介绍通用的信号发生器有哪些分类,并简要说明了各种信号源的特点和作用,另外重点讲解了信号发生器的主要指标,介绍了现有信号发生器一些特殊功能。关键词:任意波形发生器、函数信号发生器、频率分辨率、存储深度

2019-06-04 07:52:41

基于labview的数字信号发生器设计

2012-05-18 19:01:42

DDS直接数字频率合成器、信号发生器、函数发生器1.DDS直接数字频率合成器、信号发生器、函数发生器他们之间有哪些异同?2.目前只发现ADI有相关的产品,国产有哪些品牌可以推荐3.如果要输出的频率和功率是实时可调的,用MCU控制DDS芯片是否可以实现?

2022-03-24 18:10:02

数字LVDS信号后,直接输入液晶屏,以避免信号传输过程产生的失真与损耗。关键词:液晶显示;信号发生器;FPGA;LVDS

2019-06-21 06:23:52

申请理由:项目描述:基于MCU的信号发生器的设计,通过此开发套件来制作一个简易信号发生器,实现正弦波、三角波、方波、锯齿波等常用波形的产生,为进一步学习电子威廉希尔官方网站

奠定基础~

2016-11-25 17:53:53

调谐的可变增益放大器(VGA)。这种设计以20MHz 的性能为目标,幅度为22.4 V(+39 dBm),负载为50 Ω。图2. 更小、更简单的信号发生器输出级新型紧凑式输出级初始信号可能来自数模转换器

2019-10-19 08:00:00

正弦波、方波、三角波、锯齿波发生器,幅度、频率动态调整,用FPGA实现

2013-05-14 21:24:25

利用FPGA实现信号发生器

2016-08-24 16:24:24

增益应设计为1.6V/V。整体电路配置如图3所示,其可在22.4V(39dBm)幅度和50Ω负载下实现20MHz带宽。 图3:采用分立设计的信号发生器输出级的简化电路。 通过大功率的VGA

2020-12-09 14:16:51

存储一定容量的图像信息,丰富的I/O资源可以随即扩展外接大容量存储器的特性,因此由 FPGA完成对图像数据的处理及产生行场扫描时序信号。很好地实现了图象数据处理的实时性和稳定性,达到了性能与价格的完美

2019-07-17 07:12:48

信号发生器又称为波形发生器是一种常用的信号源并且广泛应用于电子电路、通信、控制和教学实验等领域的重要仪器之一。为了降低传统函数信号发生器成本,改善信号发生器低频稳定性。

2019-09-05 07:22:51

信号发生器种类很多,按是否利用频率合成威廉希尔官方网站

来分,可分为非频率合成式信号发生器与频率合成式信号发生器。其中频率合成式信号发生器的频率准确度和稳定度都很高,且频率连续可调,是信号发生器的发展方向。频率

2019-09-26 06:45:26

求一个基于FPGA的DDS信号发生器设计,最好有DA模块和相位累加器模块的代码。

2019-03-18 22:09:03

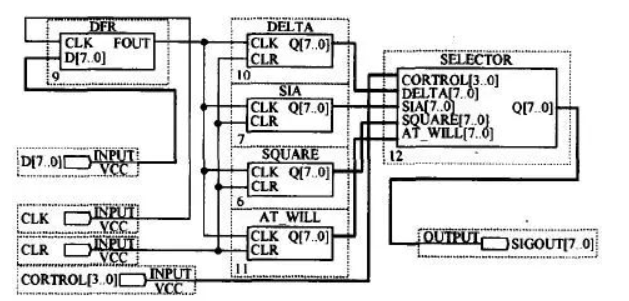

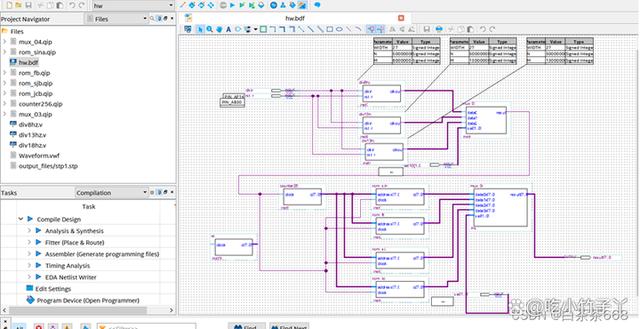

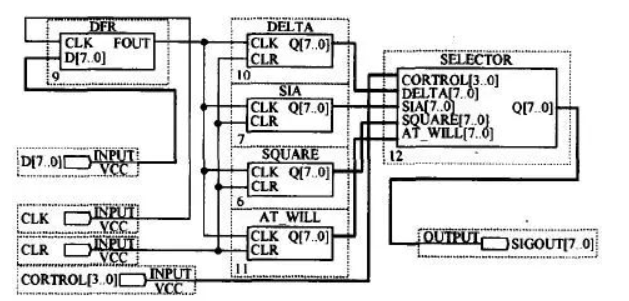

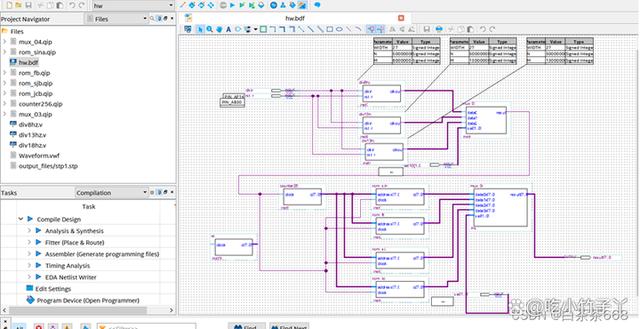

三种信号,正弦波、方波、三角波,数据存储部分存储三种信号的波形数据。 FPGA软件设计采用顶层原理图模式,正弦波、三角波、矩形波信号发生器的顶层模块原理图,块内是用Verilog语言编写的程序

2018-08-23 15:32:05

基于ALTERA实现的DDS信号发生器设计

2017-05-12 15:08:10

基于labview和fpga的信号发生器要求:【1】正弦波、方波、锯齿波、三角波。【2】频率、幅值、相位可调,调节步进值:频率0.1,幅值0.1,相位1;【3】频率最高:20k;峰值最高:3.3

2022-01-18 07:35:42

如何实现简易正弦信号发生器的设计?单片正弦信号发生芯片ML2035具有哪些特点?ML2035的基本原理是什么?主要由哪些部分组成?

2021-04-14 06:51:25

DDS电路的工作原理是什么如何利用FPGA和DDS威廉希尔官方网站

实现正弦信号发生器的设计

2021-04-28 06:35:23

DDS的工作原理和基本结构基于FPGA的DDS信号发生器的设计如何建立顶层模块?

2021-04-09 06:46:42

信号发生器又称信号源或振荡器,在生产实践和科技领域中有 着广泛的应用。能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

2019-11-11 08:07:57

模拟雷达信号发生器的结构是怎样组成的?如何设计并实现模拟雷达信号发生器?

2021-04-29 07:20:27

看了挺多文献了,现在仅仅有一点VerilogHDL的知识,之前了解过一点FPGA的设计,但是还是有很多地方看不懂。想问一下DDS信号发生器和函数信号发生器的区别。

2020-02-19 21:25:01

怎么实现信号发生器系统的FPGA设计?

2021-09-30 06:35:31

m序列信号发生器由那几部分组成?怎么实现m序列信号发生器的设计?

2021-05-10 06:09:23

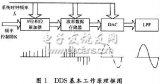

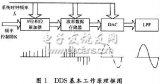

介绍了DDS的发展历史及其两种实现方法的特点,论述了DDS的基本原理,并提出一种基于FPGA的DDS信号发生器的设计方法,使DDS信号发生器具有调频、调相的功能,最后对其性能进行了分析。实验表明该系统具有设计合理、可靠性高、结构简单等特点,具有很好的实用价值。

2021-05-11 06:58:58

DDFS的原理和特点是什么?基于CPLD的函数信号发生器设计

2021-05-08 08:44:40

为了比较DSP和SOPC威廉希尔官方网站

在电子设计领域的应用,采用泰勒展开法和DDFS威廉希尔官方网站

,分别给出设计方案的硬件电路结构和软件流程图,并通过集成开发环境CCS和DE2开发板实现正弦信号发生器。结果表明,采用

2021-05-12 06:15:43

本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS的信号发生器。

2021-05-06 09:54:10

)。DDS是开环系统,无反馈环节,输出响应速度快,频率稳定度高。因此直接数字频率合成威廉希尔官方网站

是目前频率合成的主要威廉希尔官方网站

之一。文中的主要内容是采用FPGA结合虚拟仪器威廉希尔官方网站

,进行DDS信号发生器的开发。

2019-09-29 08:08:12

怎样去设计一种基于FPGA的正弦信号发生器?如何对基于FPGA的正弦信号发生器进行仿真?

2021-09-28 06:31:34

连续线性 dB 调谐的可变增益放大器(VGA)。这种设计以 20MHz 的性能为目标,幅度为 22.4 V(+39 dBm),负载为 50 Ω。 图 2. 更小、更简单的信号发生器输出级 新型紧凑式

2020-07-18 07:00:00

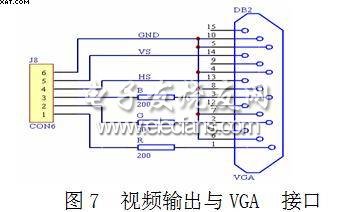

VGA图象信号发生器的工作原理是什么?VGA图象信号发生器该如何去设计?

2021-04-28 06:06:40

以前学习过一段时间stm32,算是入门了,现在又学了点fpga,想要做一个基于32和fpga的信号发生器,但是不知道从何下手,在网上查资料也是说得很笼统,不能给我以明示,不知道这里有没有哪位做个或会做的,希望能指点一下

2019-04-22 23:05:44

信号发生器电路图

2019-10-09 09:11:01

本文介绍一种多通道虚拟信号发生器的设计和实现方法,该信号发生器采用“计算机+PC 总线模板+软件”的模式进行设计,拥有众多的信号通道,便于在需多信号源的测控系统

2009-06-17 11:24:51 65

65 本文介绍基于FPGA 和DDFS 威廉希尔官方网站

,应用Altera 公司的FPGA 开发工具DSP Builder 设计数字移相信号发生器,该数字移相信号发生器的频率、相位、幅度均可预置,分辨率高,精确可调。且可分

2009-12-18 11:59:54 44

44 根据直接数字合成器的基本原理,给出了基于FPGA 的直接数字合成器的设计与实现,利用FPGA有效地扩展了输出波形的频率范围,实现了数字移相信号发生器。该信号发器主要采用了

2009-12-26 16:34:58 36

36 基于FPGA的DDS信号源设计与实现

利用DDS和 FPGA 威廉希尔官方网站

设计一种信号发生器.介绍了该信号发生器的工作原理、 设计思路及实现方法.在 FPGA 器件上实现了基于 DDS技

2010-02-11 08:48:05 223

223 本实验是基于EasyFPGA030的波形发生器设计,用EasyFPGA030开发套件实现频率可以受按键控制调节的,矩形波和三角波发生器。

2010-03-11 15:35:15 61

61 根据直接数字合成器的基本原理,给出了基于FPGA的直接数字合成器的设计与实现,利用FPGA有效地扩展了输出波形的频率范围,实现了数字移相信号发生器。该信号发生器主要采用了直接

2010-07-21 17:30:47 69

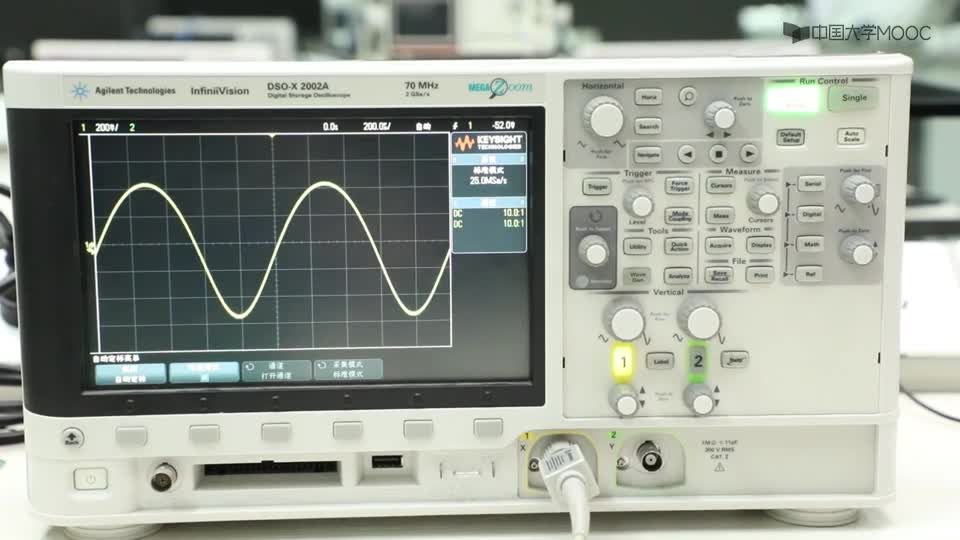

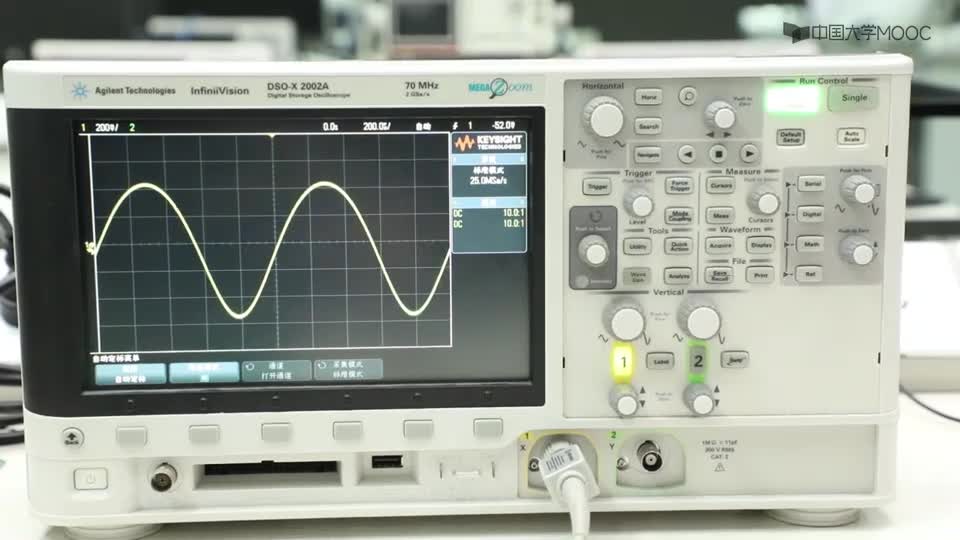

69 FPGA实现智能函数发生器设计介绍了一种基于 FPGA 的智能函数发生器的设计.采用EDA威廉希尔官方网站

对此设计进行功能仿真和时序仿真,在EDA/SOPC系统开发平台上实现程序下载,同时在示波器上观察波形

2011-07-25 11:00:53 55

55 为配合地震计电磁信息采集系统对地震计进行标定,设计一款基于FPGA的地震计标定 信号发生器 。以Altera EP2C8T144C8型 FPGA和16位串行DAC芯片DAC8560为核心,利用直接数字频率合成威廉希尔官方网站

、m序

2011-08-05 14:33:47 49

49 本文在介绍差分跳频G函数算法原理基础之上,对短波差分跳频信号发生器进行了基于FPGA的整体系统优化设计,并分别在软件和硬件环境下进行了仿真与实现。

2011-08-13 15:04:11 1535

1535

以FPGA芯片为载体,通过QuartusII的LPM_ROM模块和VHDL语言为核心设计一个多功能 信号发生器 ,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5种信号,通

2011-08-15 11:00:59 83

83 用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(

2011-09-06 11:59:48 5280

5280

函数信号发生器的实现方法通常是采用分立元件或单片专用集成芯片,但其频率不高,稳定性较差,且不易调试,开发和使用上都受到较大限制。随着可编程逻辑器件(FPGA)的不断发展,

2011-09-19 17:08:53 32578

32578

以FPGA 芯片为载体, 通过QuartusII 的LPM_ROM 模块和VHDL 语言为核心设计一个多功能信号发生器,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5 种信号,

2011-09-26 14:05:54 8050

8050

为了降低传统函数信号发生器成本,改善函数信号发生器低频稳定性,本文结合FPGA和51单片机设计并实现了产生以0.596Hz频率精度各种函数信号。函数信号频率、波形、幅度由51单片机控

2012-03-22 12:08:01 125

125 VGA图像信号发生器的设计涉及到图像数据的处理,对电路的工作速度和性能要求较高,VGA工业标准要求的时钟频率高达25MHz,使用传统的电子电路设计方法是难以实现的。采用专用的视频

2012-05-25 10:29:16 2350

2350

设计采用Altera公司CycloneII系列EP2C5Q208作为核心器件,采用直接数字频率合成威廉希尔官方网站

实现了一个频率、相位可控的基本信号发生器。该信号发生器可以产生正弦波、方波、三角波和锯齿波四种波形。仿真及硬件验证的结果表明,该信号发生器精度高,抗干扰性好,此设计方案具有一定的实用性。

2013-01-22 14:45:33 472

472 为了提高数字调制信号发生器的频率准确度和稳定度,并使其相关威廉希尔官方网站

参数灵活可调,提出了基于FPGA和DDS威廉希尔官方网站

的数字调制信号发生器设计方法。利用Matlab/Simulink、DSP Builder、QuartusⅡ 3个

2013-04-27 16:50:59 183

183 基于FPGA的正弦信号发生器的 威廉希尔官方网站

论文

2015-10-30 10:39:05 20

20 基于FPGA的多功能图像目标发生器的设计与实现

2016-08-30 15:10:14 6

6 VGA信号发生器制作资料

2017-10-16 09:04:40 28

28 脉冲信号发生器是 信号发生器的一种。信号发生器按信号源有很多种分类方法,其中一种方法可分为混和信号源和逻辑信号源两种。其中混和信号源主要输出模拟波形;逻辑信号源输出数字码形。混和信号源又可分为函数

2017-10-26 17:09:54 20777

20777

FPGA和51单片机信号发生器设计

2017-10-31 09:15:37 22

22 基于运放的信号发生器精度低且稳定性和可调节性差,而基于DDS的信号发生器则成本高、电路复杂。为此提出了基于FPGA+PWM的多路信号发生器设计方法。该方法硬件上无需DAC与多路模拟开关,由FPGA产生调制输出波形信号所需的PWM脉冲波,经二阶低通滤波和放大电路后即可得到所需波形信号。

2017-11-18 09:42:01 6332

6332

信号发生器的实现方法通常有以下几种: 方案一:用分立元件组成的函数发生器:通常是单函数发生器且频率不高,其工作不很稳定,不易调试。 方案二:可以由晶体管、运放IC等通用器件制作,更多的则是用专门

2017-12-10 11:08:50 32

32 本文档内容介绍了基于fpga实现信号发生器,供参考

2018-04-20 15:23:35 65

65 针对信号发生器对输出频率精度高和幅值可调的要求,采用直接数字频率合成(DDS)威廉希尔官方网站

,提出一种基于FPGA的幅值、频率均可调的、高分辨率、高稳定度的信号发生器设计方案。采用AT89S52单片机为控制器

2018-11-06 19:35:28 21

21 数字信号发生器是数字信号处理中不可缺少的调试设备,在生产生活中的应用非常广泛。本文所设计的内容就是基于AItera公司的现场可编程门阵列(FPGA)实现数字信号发生器的设计,本设计中应用VHDL硬件描述语言进行描述,使该数字信号发生器可以产生正弦波、方波、三角波、锯齿波四个独立的波形。

2018-11-13 16:40:59 33

33 实现基于 FPGA 的多通道可调信号发生器,其中频率、相位以及幅值均可通过 PC 端串口发送数据对应调节,并可实现 4 路信号的同步。

2020-08-13 08:00:00 29

29 论述了DDS的基本原理,给出了利用FPGA实现基于DDS的2ASK/2FSK信号发生器的设计方法,重点介绍了其原理和电路,最后给出了基于.FPGA设计的实验结果.

2021-03-24 09:12:00 19

19 FPGA实现基于ROM的正弦波发生器(嵌入式开发系统)-该文档为FPGA实现基于ROM的正弦波发生器总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 11:45:41 32

32 基于CPLD的多波形信号发生器实现了各种波形的产生,尤其是实现了传统的函数信号发生器不具有的一些波形的产生。

2022-06-20 17:35:29 5446

5446

脉冲发生器: 顾名思义,脉冲发生器是一种产生脉冲的信号发生器。这些信号发生器通常采用逻辑脉冲发生器的形式,可以产生具有可变延迟的脉冲,有些甚至提供可变上升和下降时间。

2022-08-02 15:48:42 3762

3762 本设计以FPGA为控制核心,采用直接数字频率合成(DDS)设计了一款信号可调的信号发生器,采用的FPGA是Altera公司研发的的Cyclnoe II系列,所选用的型号是EP4C6F17C8,外围

2022-12-22 11:08:05 5

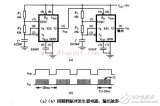

5 多功能信号发生器的原理框图如图所示。其中,CLKGEN是分频器,提供的50MHz的主频率进行分频,以得到满足多功能信号发生器设计需要的时钟频率。

2023-08-25 16:34:51 1292

1292

函数信号发生器怎么使用?函数信号发生器实现方法通常有哪几种? 函数信号发生器是一种用于产生不同类型、频率和幅度信号的仪器。它在各个领域的测试、研究和教学中都有广泛的应用。接下来我将详细介绍函数信号

2023-11-20 16:16:42 1831

1831

电子发烧友App

电子发烧友App

评论