频率合成威廉希尔官方网站

是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。分频器是集成电路中最基础也是最常用的电路。整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。本文利用VerilogHDL硬件描述语言的设计方式,通过ModelSimSE开发软件进行仿真,设计基于FPGA的双模前置小数分频器。随着超大规模集成电路的发展,利用FPGA小数分频合成威廉希尔官方网站

解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1 双模前置小数分频原理

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:![]()

式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。另一方面,分频比又可以写成:![]()

式中:M为分频器输入脉冲数;P为输出脉冲数。![]()

令P=10n,则:![]()

以上是小数分频器的一种实现方法,即在进行10n次N分频时,设法多输入X个脉冲。

2 电路组成

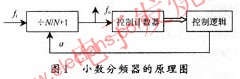

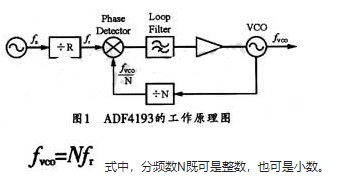

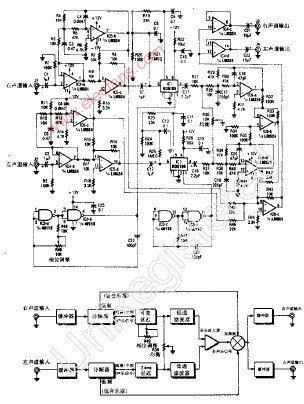

每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

3 小数分频器的Verilog-HDL设计

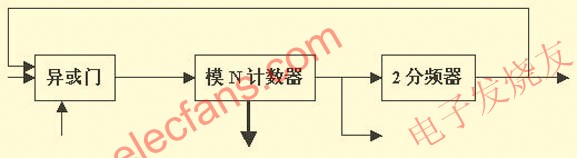

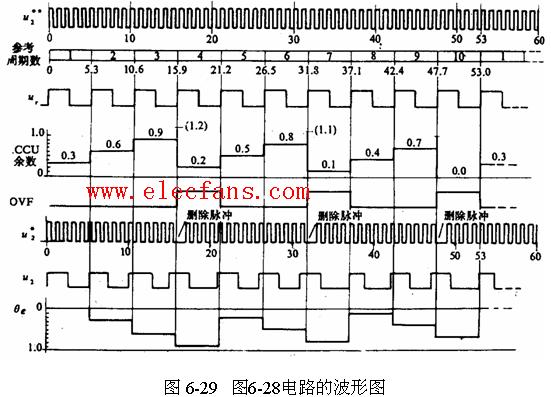

现通过设计一个分频系数为8.7的分频器来给出使用VerilogHDL语言设计数字逻辑电路的一般设计方法。这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。由于从N分频切换到N+1分频和从N+1分频切换到N分频都会产生一个随时间增长的相位移,如果简单的先进行3次8分频后做7次9分频将会产生很大的相位波动。考虑到该小数分频器要进行多次8分频和9分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的分频过程。

若分频系数后为两位小数,则用100减去分频系数的小数部分。用VerilogHDL设计÷8/9双模前置分频器的描述程序如下:

4 波形仿真

上述的÷8/9双模前置分频器的描述程序经ModelSim编译、时序interwetten与威廉的赔率体系

后,得到的波形如图2所示。

由图2可见,当reset为0时,分频器复位,当a为1时,进行8分频,当a为0时则进行9分频。

如图3所示,在前3个时钟,a值为0,则进行9分频,其后一个时钟a为1,进行8分频,后两个脉冲,又进行9分频,后进行一次8分频,然后又进行两次9分频,最后进行一次8分频。

5 电路实现

FPGA现场可编程门阵列(FieldProgrammableGateArray)是20世纪80年代中期出现的高密度可编程逻辑器件。FPGA及其软件系统是开发数字电路的最新威廉希尔官方网站

。他利用EDA威廉希尔官方网站

,以电路原理图、硬件描述语言、状态机等形式输入设计逻辑;他提供功能模拟、时序仿真等模拟手段,在功能模拟和时序仿真度满足要求后,经过一系列的变换,将输入逻辑转换成FPGA器件的编程文件,以实现专用集成电路。本设计选用Xilinx公司推出的90nm工艺制造的现场可编程门陈列Spartan-3来设计小数分频器,体积减小,可靠性提高。

6 结语

采用前置双频分频器设计的小数分频器,小数分频器的精度受控制计数器的影响,当n值为100时,小数分频的精度达到1/100;当n值为1000时,小数分频的精度达到1/1000;依此类推。FPGA有相当丰富的硬件资源,因此可以用FPGA设计高精度的小数分频器。采用FPGA组成的数字频率合成器,单环鉴相频率达100MHz以上,分辨率可达10-6。这种小数分频器得到了广泛的应用,例如,对图象采集系统中的行分频和列分频的设计,就可以应用本分频器电路作为时钟发生器。欲了解更多信息请登录电子发烧友网(//www.obk20.com)

基于FPGA的双模前置小数分频器的设计

- FPGA(591969)

- 小数分频器(5881)

相关推荐

基于VHDL和FPGA的多种分频的实现方法

分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有

2010-09-03 17:04:20 2442

2442

2442

2442

基于FPGA的通用数控分频器设计方案

本文首先介绍了各种分频器的实现原理,并在FPGA开发平台上通过VHDL文本输入和原理图输入相结合的方式,编程给出了仿真结果。最后通过对各种分频的分析,利用层次化设计思想,综合设计出了一种基于FPGA的通用数控分频器,通过对可控端口的调节就能够实现不同倍数及占空比的分频器。

2015-05-07 09:43:16 4685

4685

4685

4685

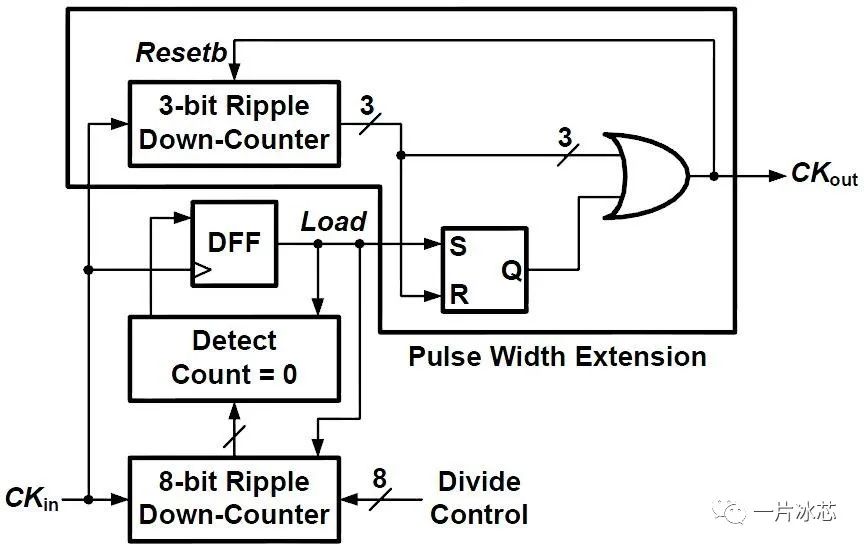

Sigma-Delta小数分频PLL中的分频器该怎么做?

文献给出的分频器结构如图1所示。该分频器最高输入频率(f~in~)为16.3GHz,也就是一个周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

2023-10-31 12:54:56 767

767

767

767

1.2V 6GHz 1.19mW 32/33前置分频器的设计

基于4/5双模SCL分频结构设计了一个高速、低压、低功耗的32/33双模前置分频器。该设计基于TSMC90nm1P9M CMOS工艺,利用Mentor Graphics Eldo工具仿真,结果表明该

2010-05-28 13:37:48

FPGA众多分频资料,不容错过

`基于FPGA+的任意小数分频器的设计基于FPGA的多种分频设计与实现基于FPGA的小数分频器的实用Verilog 实现基于FPGA 的通用分频用Verilog+HDL实现基于FPGA的通用分频器

2012-02-03 15:02:31

CH34X系列USB转串口芯片的波特率分频方式只有整数分频?还是有小数?

咨询一个问题:CH34X系列USB转串口芯片的波特率分频方式只有整数分频?还是有小数分频?例如CP210x芯片的波特率生成只有整数分频,为48 MHz/(2 × Prescale × n),生成

2022-07-07 07:09:19

低通滤波器的FPGA设计及仿真

主要任务:1.熟悉低通滤波器的原理及应用2.熟悉FPGA的硬件描述3.FPGA如何实现小数分频器4.用MATLAB对低通滤波器的验证预期成果或目标:FPGA对低通滤波器的Verilog(或VHDL

2013-04-04 22:16:11

基于FPGA的任意分频器设计

本帖最后由 weihu_lu 于 2014-6-19 16:25 编辑

作者:卢威虎1、前言 分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如

2014-06-19 16:15:28

基于FPGA的任意数值分频器的设计

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

基于FPGA的数字分频器该怎么设计?

中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺威廉希尔官方网站

的进步,FPGA器件的英国威廉希尔公司网站

取得了飞跃发展及突破。分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数

2019-10-08 10:08:10

如何利用CPLD/FPGA设计多功能分频器?

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。利用CPLD/FPGA设计多功能分频器,我们具体该怎么做呢?

2019-08-12 07:50:25

怎么把小数分频控制字与整数分频控制字结合起来去控制可编程分频器?

要设计小数分频PLL,基本架构已经确定:使用基于MASH111的DSM,双模预分频器+PScounter实现。现在遇到的问题是,不知道怎么把小数分频控制字经过DSM后的输出与整数分频控制字结合起来去控制(双模分频器+PScounter)可编程分频器此前没做过小数分频PLL,求助大佬们点拨一二

2021-06-24 07:20:38

用VHDL怎样设计数控半整数分频器

使用VHDL语言怎样实现数控半整数分频器,就当输入为3时,就实现3.5分频,当输入为4时,就实现4.5分频,同时要求占空比为50%。

2014-12-02 18:28:57

请问ADI分频器的类型有什么不同?

我想对2GHz的正弦波(相位噪声很低)进行16分频,分频出来的125M信号输入给FPGA,想选用ADi的分频器实现分频功能,我有以下几个问题:1.我查了ADi的分频器,分为(1)时钟分频器,(2

2019-01-11 13:39:43

需要讲解一个占空比50%的奇数分频器的原理

本帖最后由 haozix521 于 2013-10-4 20:42 编辑

想做一个占空比50%的奇数分频器,但是不是很了解这其中的意思。网上的资料都是这样讲的“对于实现占空比为50%的N倍奇数分频

2013-10-04 20:35:11

用Verilog实现基于FPGA的通用分频器

在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78

78

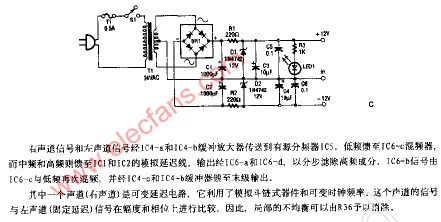

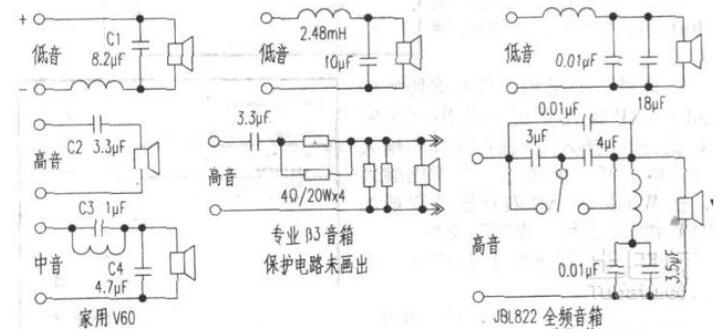

78Hi-Fi三路有源分频器

Hi-Fi三路有源分频器:此立体声三路有源分频器与三路扬声器系统配用,可避免无源分频网络的缺点,使扬声器获得最佳的功率电平。什么是有源分频器?为什么需要有源分频器 绝大多

2009-11-27 16:36:03 919

919

919

919定阻型功率分频器的设计与制作(四)-分频器元器件的选取与制作

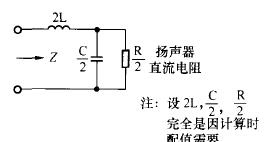

定阻型功率分频器的设计与制作(四)-分频器元器件的选取与制作:制作分频器所需的电阻,一律用金属膜电阻为宜,但要根据不同的需要适当选取相应大小的额定功率。2 电容器的

2009-12-02 15:46:59 71

71

71

71基于FPGA的通用分频器设计

本文介绍了一种能够完成半整数和各种占空比的奇/偶数和的通用的分频器设计,并给出了本设计在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中实现后的测试数据和设计硬件的测

2009-12-19 16:25:09 65

65

65

65基于FPGA 的等占空比任意整数分频器的设计

基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

39

39

39分频器设计与制作 (电子书)

分频器设计与制作 (电子书):分频器的基本原理,分频器设计,分频频率和截止带衰减率的选择与使用,元件的选配及要求等内容,电感线圈的设计与制作。

2010-03-29 10:53:02 702

702

702

702一种通用的可编程双模分频器

提出了一种通用的可编程双模分频器,电路主要由3 部分组成: 9/8 预分频器,8 位可编程计数器和ΣΔ调制器构成。通过打开或者关断ΣΔ 调制器的输出来实现分数和整数分频两种工作

2010-04-23 08:39:35 30

30

30

30基于CPLD、FPGA的半整数分频器的设计

简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36

36

36UXN14M32K预分频器 15 GHz、32位有效分频器

UXN14M32K预分频器15 GHz、32位有效分频器UXN14M32KSuperDivider是一款DC-15 GHz、高度瞬时的整数分频器,顶部1和4,294,967,295

2024-02-29 13:59:41

基于CPLD/FPGA的半整数分频器的设计

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 869

869

869

869

小数分频合成器

锁相频率合成器的基本特性是,每当可编程分频器的分频比改变1时,得到输出频率增量为参考频率fr。为提高频率的分辨力就需减小参考频率fr,这对转换时间等性

2008-04-21 14:35:20 872

872

872

872

基于FPGA的多种形式分频的设计与实现

摘 要: 本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描

2009-06-20 12:43:07 562

562

562

562

基于CPLD/FPGA的半整数分频器的设计

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 627

627

627

627

基于CPLD/FPGA的多功能分频器的设计与实现

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1139

1139

1139

1139

适用于WLAN IEEE80211a标准的双模前置分频器设计

本文采用动态TSPC结构,利用TSMC 90nm 1P9M 1.2VCMOS工艺,设计了一个适用于WLAN IEEE802.11a标准的双模前置分频器,具有高速、低压、低功耗的特点。

2011-03-29 10:56:07 1401

1401

1401

1401

TD-SCDMA射频前置分频器的设计

前置分频器是PLL中重要的部分。本文在研究和分析国内外3G系统结构基础上,选定零中频结构收发信机中本振PLL反馈回路上分频模块作为研究对象,实现射频模式下准确小数级分频。

2011-06-15 09:56:02 2511

2511

2511

2511

应用于倍频电路的预置可逆分频器设计

分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍

2011-08-17 16:50:45 1896

1896

1896

1896

低噪声小数N分频锁相环实现方案

该电路是低噪声微波小数N分频PLL的完整实现方案,以 ADF4156 作为核心的小数N分频PLL器件。使用 ADF5001 外部预分频器将PLL频率范围扩展至18 GHz。

2011-10-26 15:02:22 1333

1333

1333

1333

基于FPGA的小数分频实现方法

提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121

121

121基于Verilog的FPGA分频设计

给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355

355

355什么是分频器_分频器的主要参数(分频点、路、阶)

什么是分频器 分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放。在高质量声音重放时,需要进行电子分频处理。 分频器是音箱内的一种电路装置,用以将输入的模拟

2017-11-18 11:49:30 46430

46430

46430

46430动态有比D触发器结构的双模前置分频器设计分析

摘要:基于目前流行的TSPC高速电路,利用TSMC90nm 1.P9M 1.2V CMOS工艺设计了高速、低压、低功耗32/33双模前置分频器,其适用于WLAN IEEE802.1la通信标准。运用

2017-11-25 11:20:01 3624

3624

3624

3624基于CMOS工艺适用于WLAN IEEE802.11a标准的双模前置分频器设计

中,压控振荡器(VCO)和前置分频器(Prescaler)是工作在最高频率的两个模块,它们是限制 PLL工作频率的主要瓶颈,因此提高前置分频器的工作速度是解决限制PLL工作频率上限的一个关键因素。

2017-12-10 03:30:01 1726

1726

1726

1726

分频器有哪些_分频器分类

分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

2018-01-10 15:36:20 10795

10795

10795

10795小数分频频率合成器的实现方法

Σ-Δ小数分频频率合成器相位噪声源到输出端的传递函数除VCO相位噪声传递函数为高通滤波传递函数外,其余噪声源到输出端的传递函数均为低通滤波传递函数。本文着重分析Σ-Δ量化噪声对输出相位噪声的影响。

2018-03-21 08:58:26 7996

7996

7996

7996

音箱分频器怎么接线_音箱分频器接线图解

本文开始介绍了音箱分频器原理,其次介绍了音箱分频器分类与特点以及音箱分频器电路及作用,最后介绍了音箱分频器接线方法图解。

2018-04-13 09:32:27 110675

110675

110675

110675一文解析主动分频器和被动分频器的优缺点

本文首先介绍了分频器的分类及电子分频器的工作原理,其次介绍了主动分频器的优缺点,最后介绍了被动分频器的优缺点,具体的跟随小编一起来了解一下。

2018-05-28 14:52:31 47204

47204

47204

47204FPGA学习系列:13. 任意分频器设计

设计背景: 分频在 fpga的设计中一直都担任着很重要的角色,而说到分频,我相信很多人都已经想到了利用计算器来计算达到想要的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果我需要

2018-06-13 11:21:48 12390

12390

12390

12390

小数分频威廉希尔官方网站 与ADF4193快速开关频率合成器的研究

小数分频是频率合成中的一项新威廉希尔官方网站

。这种威廉希尔官方网站

的特点是使单环锁相频率合成器的平均分频比变为小数。通过使分频比变为小数,可获得任意小的频率间隔,实现高频率分辨力的频率合成,利用小数分频威廉希尔官方网站

完成的小数分频频率合成器,不仅频率分辨力高,而且频率转换速度快,还可使频谱改善、线路简化、体积缩小、程控方便、集成容易。

2019-05-24 08:05:00 1639

1639

1639

1639

分频器的作用是什么 半整数分频器原理图分析

分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

2019-02-01 01:28:00 15719

15719

15719

15719

实现任意整数分频的原理与方法讲解

分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

2019-11-20 07:05:00 6652

6652

6652

6652如何使用FPGA进行任意小数分频器的设计

论文分析了双模前置小数分频器的分频原理和电路实现。结合脉冲删除威廉希尔官方网站

,提出了一种适于硬件电路实现的任意小数分频的设计方案 ,用 VerilogHDL语 言编程 ,在 QuartusII下对 此方案进 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片来 实 现 。

2019-08-02 08:00:00 5

5

5

5基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计

在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 825

825

825

825

奇数分频器的介绍和实现

因为偶数分频器过于简单,所以我们从奇数分频器开始说起8 01 奇数分频器 假设我们要实现一个2N+1分频的分频器,就需要高电平占N+0.5个周期,低电平占N+0.5个周期,这样进行处理的最小

2021-03-12 15:44:54 5614

5614

5614

5614

CPLD/FPGA的半整数分频器设计

简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53 10

10

10

10基于FPGA的CPLD半整数分频器设计方案

简要介绍了 CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和15的分频器的设计为例,介绍了在 Maxplusll开发软件下,利用ⅤHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-22 16:52:15 5

5

5

5偶数分频器的设计

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 948

948

948

948

偶数分频、奇数分频、半整数分频和小数分频详解

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数分频以及小数分频进行简单的总结。

2023-03-29 11:38:40 3108

3108

3108

3108

基于Verilog的分数分频电路设计

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1028

1028

1028

1028

FPGA学习-分频器设计

是用于满足设计的需求。 分频:产生比板载时钟小的时钟。 倍频:产生比板载时钟大的时钟。 二:分频器的种类 对于分频电路来说,可以分为整数分频和小数分频。 整数分频:偶数分频和奇数分频。 小数分频:半整数分频和非半整数分频。 三:分频器的思想 采用计数器的思想实

2023-11-03 15:55:02 471

471

471

471

锁相环整数分频和小数分频的区别是什么?

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种威廉希尔官方网站

。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 312

312

312

312分频器的作用 分频器的功率是不是越大越好

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

2024-02-01 11:19:51 461

461

461

461 电子发烧友App

电子发烧友App

评论