如何实现高速时钟信号的差分布线

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2009-04-15 00:26:37 3051

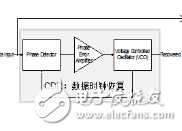

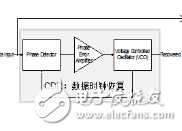

3051 可以通过不同架构实现时钟恢复,测量设备中最常用的是基于锁相环(PLL)的方法。根据在数据中看到的跳变,使用恢复电路导出与输入数据同步的时钟,这取决于看到数据中的跳变。

2011-01-24 08:55:50 1938

1938

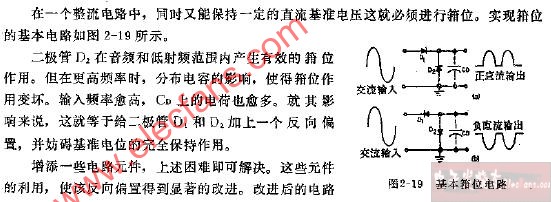

通过使用 OPA615 高带宽、直流恢复电路,此参考设计可为各种应用提供高带宽、高精度采样保持电路。该电路具有整套设计指南支持,可以针对给定应用方便地调整。

2013-11-20 11:26:29 4145

4145

)的时钟资料恢复电路,从而取得突破性的进展:在具有RS-FEC误码校正和使用OM4光纤的条件下,传输距离达400米,在没有RS-FEC条件下则达300米,并已通过多重检验测试,再次彰显昂纳在行内领先位置

2017-12-12 11:21:20 6789

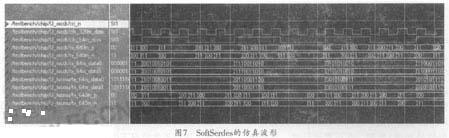

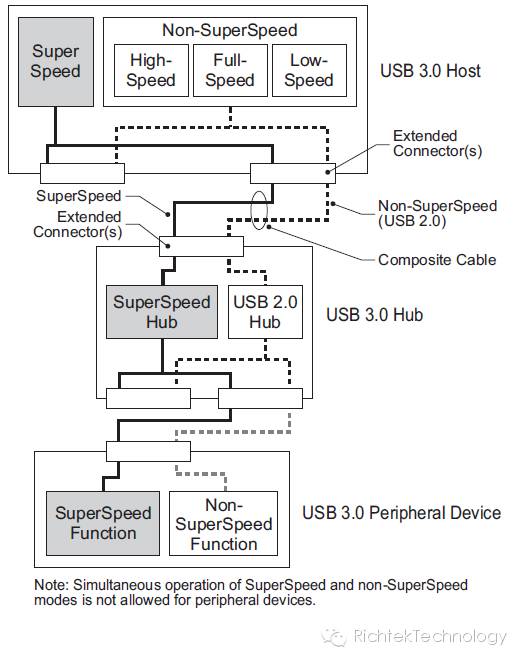

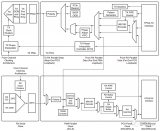

6789 SERDES恢复出的数据进入FPGA有一个解复用和时钟域转换的问题,Stratix GX包含了专用电路可以完成8/10bit数据到8/10/20bit数据的Mux/Demux,另外SERDES收端到FPGA内部通用逻辑资源之间还有FIFO可以完成数据接口同步,其电路结构如图所示。

2018-04-08 08:46:50 9421

9421 时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4795

4795

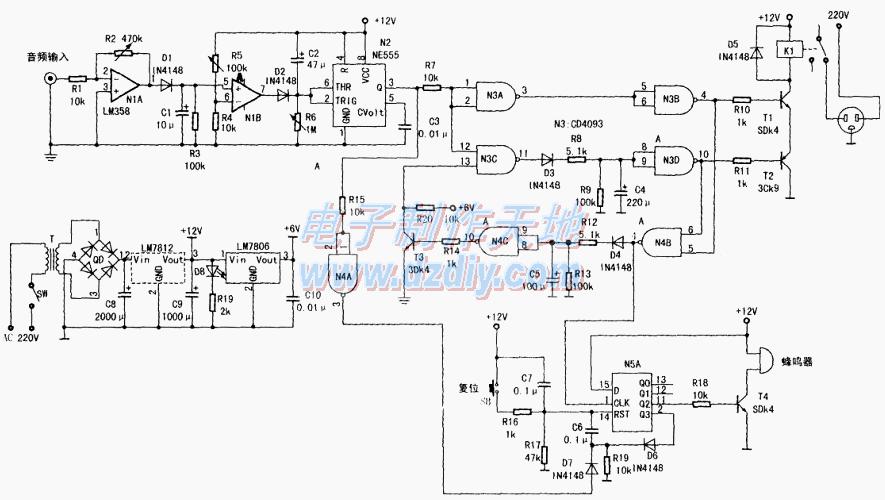

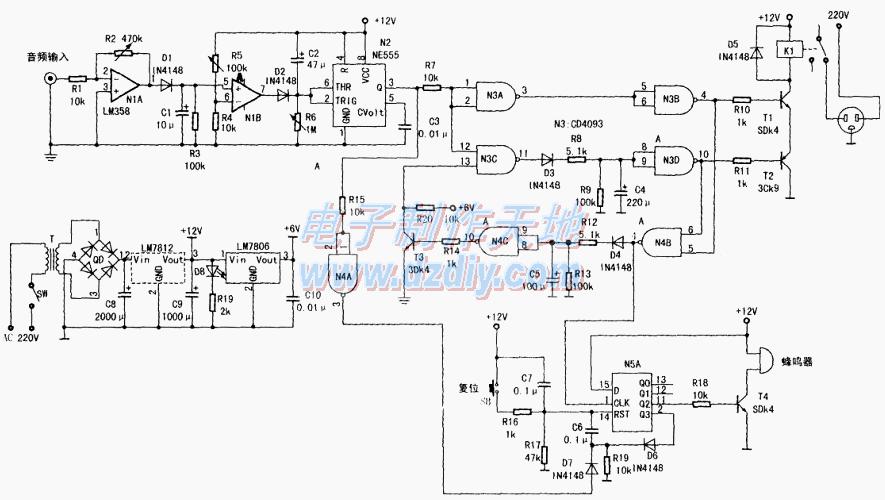

求三次延时芯片我们设计中以前用到的是无限次延时恢复电路,用的NE555的芯片,现在想把无限次延时改为三次延时(只延时恢复三次,第四次就不再恢复),只想换个芯片,不想改动原先的线路,请问大侠能做到吗?

2009-12-13 09:43:25

灵思All Programmable FPGA 和 SoC 实现高速无线电设计( Enabling High-Speed Radio Designs with Xilinx All

2017-02-10 17:10:32

流水方式对复数数据实现了加窗、FFT、求模平方三种运算。整个设计采用流水与并行方式尽量避免瓶颈的出现,提高系统时钟频率,达到高速处理。实验表明此处理器既有专用ASIC电路的快速性,又有DSP器件的灵活性的特点,适合用于高速数字信号处理。

2012-08-12 11:49:01

、什么是JESD204B协议该标准描述的是转换器与其所连接的器件(一般为FPGA和ASIC)之间的数GB级串行数据链路,实质上,具有高速并串转换的作用。2、使用JESD204B接口的原因a.不用再使用数据接口时钟

2019-12-04 10:11:26

,具有高速并串转换的作用。2、使用JESD204B接口的原因a.不用再使用数据接口时钟(时钟嵌入在比特流中,利用恢复时钟威廉希尔官方网站

CDR)b.不用担心信道偏移(信道对齐可修复此问题,RX端FIFO缓冲器)c.

2019-12-03 17:32:13

的,都是时钟双沿触发的DDR数据,并且每次传输的数据个数都是4个长字(即128bit)的整数倍。鉴于以上两种芯片链路口数据的共同点,所以采用FPGA与两类芯片通信时,接收和发送的数据缓存部分的设计应该是

2019-06-19 05:00:08

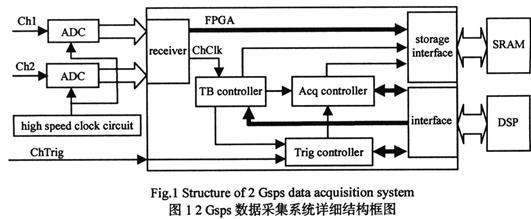

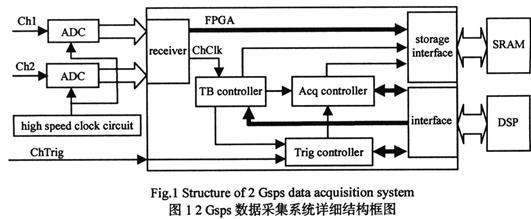

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬件完成,而且速度快,组成形式灵活,并可以集成外围控制、译码和接口电路。更最主要

2019-11-01 07:40:10

比较器将网线传输过来的差分信号转为单端信号,该信号时钟频率为100M,电平标准能满足FPGA的输入电平标准,波形质量尚可。单端信号直接连接到FPGA,现在如果想用FPGA直接采集,应该怎么处理呢,是当作异步信号直接打拍吗,过采样的话时钟频率不够。时钟恢复目前来不及实现。

2020-03-07 16:01:37

高速专用GFP处理器的FPGA实现采用 实现了非标准用户数据接入 网络时,进行数据 封装和解封装的处理器电路在处理器电路中引入了缓冲区管理器,使得电路能够有效处理突发到达 瞬时速率较高的客户数据

2012-08-11 11:51:11

的Board Layout。直流恢复系统使用图615和图41恢复两个系统。图41实现了作为单位增益放大器的直流恢复功能。从它的名字可以预期,这个直流恢复电路不提供任何放大。在需要放大的应用中,考虑使用图40

2020-10-20 15:58:35

视频信号(包括数据与时钟,其中数据位宽16位,时钟1位,最高工作频率148.5MHZ).2.遇到的问题时钟相对于数据的延时,也就是信号的建立与保持时间在经过FPGA后出现偏移。造成后端的DA不能正确的采集到数据。

2014-02-10 16:08:02

以AC/DC Boost开关电源为例,如图1所示,主电路中输人整流桥二极管产生的反向恢复电流的di/dt远比输出二极管D反向恢复电流的|di/dt|要小得多。图2是图1开关电源中输人整流桥二极管

2021-06-30 16:37:09

`例说FPGA连载17:时钟与复位电路设计特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc FPGA的时钟输入都有专用引脚,通过这些专用

2016-08-08 17:31:40

文献说该图是可变增益主放大器主要由极零相消电路、微分电路、2 级积分放大电路,1 级跟随放大和基线恢复电路组成,其原理图如图

2017-04-06 17:10:08

的电压输出信号进一步放大,并维持在一个正确的范围,以为后续的时钟恢复和数据裁决电路服务。主放大器要求能处理高速信号,并且具有高增益和较大的动态输入范围。 判决器和时钟恢复电路对信号进行再生。在发送端

2022-04-15 21:01:49

介绍了一种基于现场可编程门阵列(FPGA)和第二代双倍数据率同步动态随机存取记忆体(DDR2)的高速模数转换(ADC)采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA中如何实现高速同步

2010-04-26 16:12:39

、野外试验以及生产应用,证明结合FPGA威廉希尔官方网站

,时钟恢复和系统同步威廉希尔官方网站

在地震勘探仪器中具有独到的优势,其精度可达us级,而且稳定,实现方便。地震勘探仪器是一个高度集成的网络采集系统,在这些地震勘探仪器中

2019-06-18 08:15:35

输出,或通过FPGA的端口LVDS循环存储于高速缓存中,再由低速接口输出。其中,FPGA主要完成对外接口管理、高速缓存的控制和管理。时钟控制电路对A/D数据转换器和可编程门阵列FPGA起同步和均衡作用

2018-12-18 10:22:18

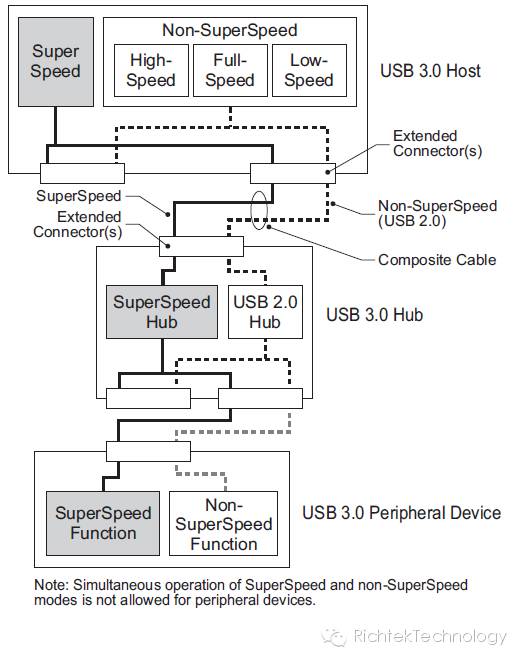

目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统对速度要求;后者虽然可以实现

2019-09-05 07:22:57

AD接口:时钟对齐、根据帧同步实现串转并数据对齐.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的内置SERDES模块,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

中优势明显。FPGA资源丰富、速度快、开发方便快捷,因此在高速数据通信中应用广泛。DDS频率合成威廉希尔官方网站

通过频率控制字、相位控制字及参考时钟的控制来实现输出信号的调频调相,并且输出信号具有频率转换快、频率

2012-09-06 12:40:54

描述 通过使用 OPA615 高带宽、直流恢复电路,此参考设计可为各种应用提供高带宽、高精度采样保持电路。该电路具有整套设计指南支持,可以针对给定应用方便地调整。

2019-07-23 08:15:29

基线恢复电路经过电容c32后脉冲信号消失,我模拟的经过电容后信号无太大变化

2017-08-03 11:58:01

基线恢复电路后原本放大5倍的信号,又减小到了放大之前。本来应该是信号幅度相差不多的

2017-11-30 19:39:35

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

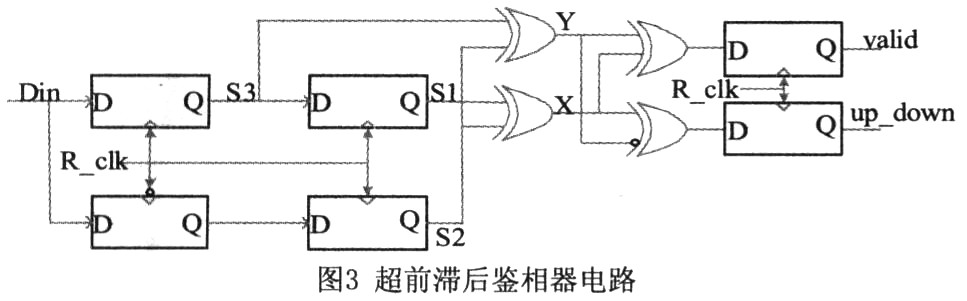

本文利用时钟切换的方法,在低端AlteraEP2C5T144C6上实现了204.8MHZ的时钟数据恢复电路,并通过了硬件验证。

2021-04-30 07:00:16

的射频标签由于工作距离远,天线尺寸小等优点越来越受到重视。射频标签芯片的射频接口模块包括电源恢复电路、稳压电路和解调整形电路。射频接口的设计直接影响到射频标签的关键性能指标。本文对射频标签能量供应原理进行了详细的理论分析,并完成了电源恢复电路、稳压电路和解调整形电路的设计。

2019-07-26 06:33:08

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

的解调电路很复杂,本系统为了使解调电路简单化,采取基带信号速率与扩频码元周期同步同速的特殊措施,省去了解调电路中复杂的载波恢复电路。1 本扩频系统的调频解调原理本系统的载波,PN码和基带信号的速率

2019-08-07 06:41:58

:PRBS或自定义等格式),信号调理前端(输出电平控制等),时钟信号前端(输出时钟电平控制等)。2)误码接收机:包括:时钟恢复电路(有的BERT没有CDR),码型判决电路(从信号中判断出码型数据),错误码

2019-07-01 06:06:01

试题,学员可通过高压电工模拟考试题库全真模拟,进行高压电工自测。1、【单选题】 配电装置中,电气设备的网状遮栏高度不低于()m,底部离地不应超过0.1m。(B)A、1.3B、1.7C、1.52、【单选题】 电路中负荷为()时,触头间恢复电压等于电源电压,有利于电弧熄灭。(C...

2021-09-02 06:52:27

本文介绍了负偏压温度不稳定性的恢复电路和恢复方法。

2021-05-07 06:32:09

的控制核心。但利用中低端FPGA还没有可以达到100MHz以上的时钟数据恢复电路。由于上面的原因,许多利用FPGA实现的高速通信系统中必须使用额外的专用时钟数据恢复IC,这样不仅增加了成本,而且裸露

2009-10-24 08:38:08

采用一种新的时钟增强方案并配合双区折射率耦合激光器实现非归零码信号的全光时钟恢复,通过数学仿真研究了此时钟恢复系统在64 Gb/s非归零码系统中的性能表现。仿真结果表

2009-03-04 10:38:27 19

19 精密参考时钟在时钟与数据恢复电路中的应用

2009-05-04 13:36:44 35

35 采用IL2E2 TDI CCD 做为传感器,与计算机构成了成像系统,并在计算机CRT 上显示出图像。主要介绍高速CCD 相机的工作时钟产生电路的设计,采用大规模集成电路FPGA 实现了该工作时钟驱动

2009-07-04 16:02:55 44

44 本文介绍了一种应用FPGA 器件完成高速数字传输的方法,利用这种方法实现无线收发芯片nRF2401A 的高速数据接口。为进一步提高信息的传输速率,这里还对待传输的数据进行了压缩处

2009-08-04 09:16:20 9

9 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 本文设计了一种以 FPGA 为数据压缩和数据缓存单元的高速数据采集系统,其主要特点是对高速采集的数据进行实时压缩,再将压缩后的数据进行缓冲存储。该设计利用数据比较模

2009-11-30 15:32:36 20

20 10Gbps XFP光模块系统数字诊断功能需要进行信号丢失(LOS)监控。通过监控光功率是否过低,可探测到导致误码率劣化的系统故障。MAX3991限幅放大器IC时钟和数据恢复电路针对XFP模块

2009-12-09 16:26:29 22

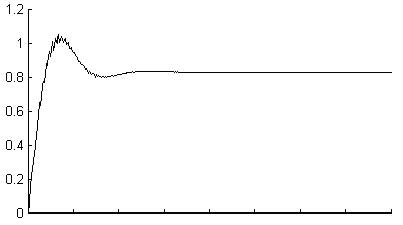

22 10Gb/s时钟数据恢复电路行为级模型研究:研究了超高速(10Gb/s) NRZ 码时钟数据恢复电路的行为级建模,并采用TSMC 0.18μm CMOS 工艺进行了电路级仿真。关键词: 时钟数据恢复;锁

2009-12-14 09:25:19 18

18 本文针对超高频无源RFID 标签芯片的设计,给出了一些关键电路的设计考虑。文章从UHF RFID标签的基本组成结构入手,先介绍了四种电源恢复电路结构,以及在标准CMOS 工艺下制作肖

2009-12-14 10:36:47 59

59 本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50 摘要:通过锁定检测器控制,初期极性相位判决算法对载波进行频率上的快速锁定,随后带加权的DD算法减少频率抖动并最终实现相位恢复。通过Matlab仿真验证,对于64QAM电路在5000个

2010-05-13 09:06:25 19

19 9.1亮度通道及矩阵输出电路9.2 色度通道9.3 彩色副载波恢复电路9.4 PALD色度解码电路实例 亮度通道的任务是将亮度信号Y从彩色全电视信号中分离出来, 经过放大

2010-10-01 10:50:55 85

85 摘要:CMX469A是CML公司推出的FFSK/MSK全双工MODEM芯片,它内部集成了载波检测、RX时钟恢复电路和振荡电路,并具有很好的信噪比以及低电压、低功耗等特性,能够接

2011-06-01 17:07:42 2941

2941

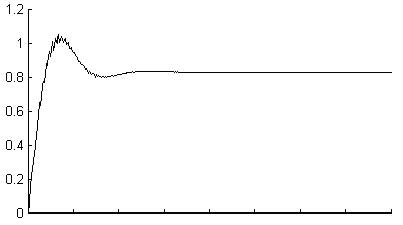

应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下

2008-10-16 08:59:42 1034

1034

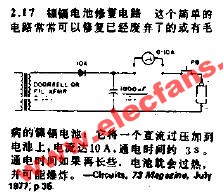

镍镉电池修复电路图

2009-01-10 12:22:49 3310

3310

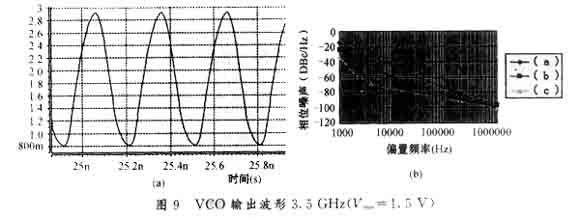

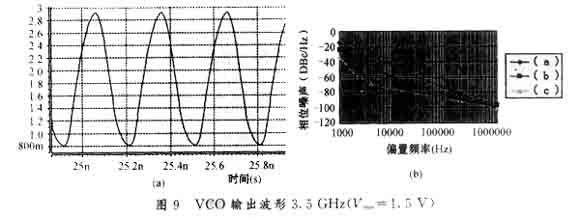

压控振荡器已经成为当今时钟恢复电路和频率合成电路中不可缺少的组成部分。本文分别从压控振荡器的振荡频率和相位噪声两个角度,详细阐述影响VCO性能的因素,并提出相应

2009-05-09 12:29:42 2515

2515

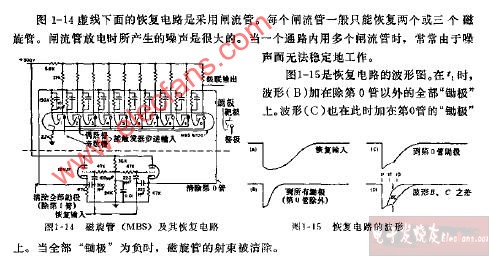

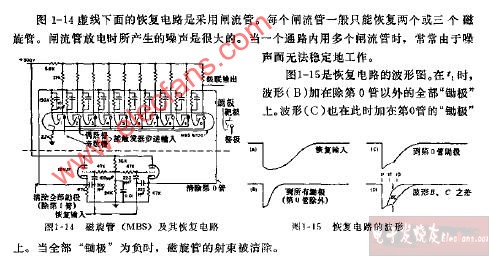

恢复电路的波形电路图

2009-06-20 11:09:55 465

465

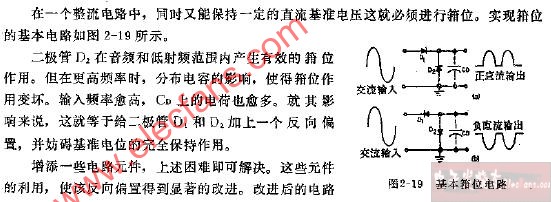

高频有增益的直流恢复电路图

2009-06-23 11:46:47 450

450

无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖

2009-07-06 18:37:55 449

449

基于FPGA的SoftSerdes设计与实现

0 引言

在高速源同步应用中,时钟数据恢复是基本的方法。最普遍的时钟恢复方法是利用数字时钟模块(DCM)

2009-12-28 09:23:40 920

920

FPGA芯片在高速数据采集缓存系统中的应用

概 述在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬

2010-03-30 10:51:15 881

881

FPGA设计的高速FIFO电路威廉希尔官方网站

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2226

2226

为利用简单的线缆收发器,实现中等数据率的串行数据传输,提出了一种基于电荷泵式PLL的时钟数据恢复的方法。鉴相器由FPGA实现,用固定延时单元构成一条等间隔的延时链,将输入信号经过每级延时单元后的多个输出用本地的VCO时钟锁存,输入信号的沿变在延时链

2011-03-15 12:39:34 90

90 本内容提供了反相恢复电路

2011-05-19 17:18:55 49

49 利用光电耦合器的通断与否进行控制。电压正常时,光电耦合器几乎无输出,VT管被反偏而截止。若故障消除,电压随之正常,该电路立即退出工作,恢复电路供电。

2011-07-04 17:16:18 11582

11582

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 178

178 一种5Gb_s双信道并行时钟数据恢复电路_李志贞

2017-01-08 10:18:57 0

0 6_25Gb_s快速锁定时钟数据恢复电路_钟威

2017-01-08 10:24:07 0

0 采用FPGA实现对AD 输出数据的高速采集

2017-08-30 17:16:02 35

35 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2017-11-16 01:01:29 20783

20783

介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片英国威廉希尔公司网站

,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该威廉希尔官方网站

,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 1840

1840

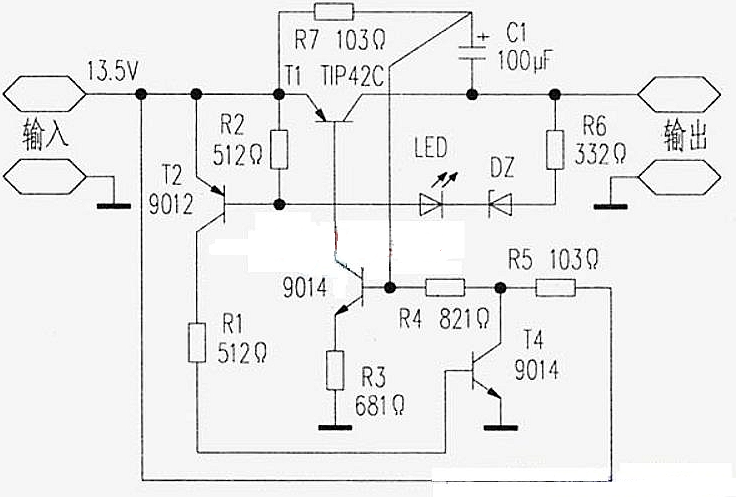

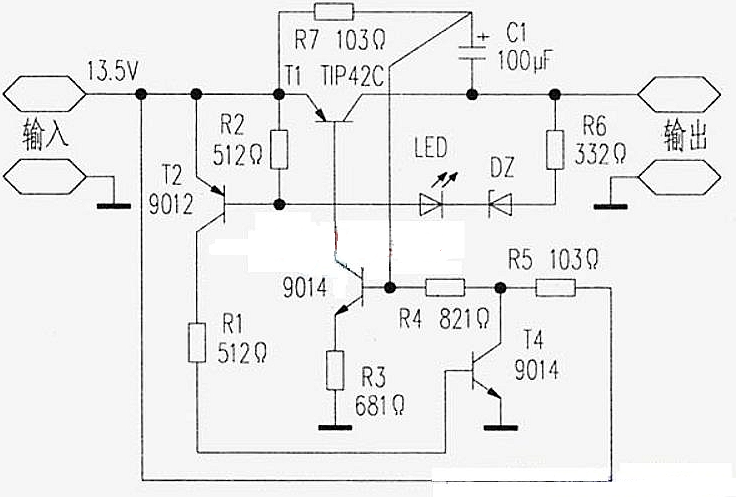

本文主要介绍了过流保护自恢复电路图大全(六款模拟电路设计原理图详解)。具有自恢复功能的过流保护电路这款无电流取样的过流保护电路具有短路点撤除后能自动恢复输出的特点,保护时较工作时电流要小得多,即使长时间短路,也不会损坏电源。

2018-02-01 14:58:10 142672

142672

本文设计了一种新颖的单片集成、适用于高速串行通信接口接收端和数据恢复电路的等间距高精度五相时钟发生电路.基于负反馈动态调整原理和数字化的模拟电路英国威廉希尔公司网站

,电路采用TSMC( Taiwan

2018-03-15 16:44:13 8

8 文中基于2.5 GB/s的高速型数据收发器模型,采用SMIC 0.18 um双半速率CMOS时钟进行数据的恢复处理。设计CMOS时钟主要包含:提供数据恢复所需等相位间隔参考时钟的1.25 GHz

2018-04-09 11:04:02 2

2 在许多高速数据采集系统中,数据正确锁存是设计者必须要面对的问题。特别是在内部时钟与外部时钟采用同一个时钟源的基于FPGA的高速数据采集系统中,由于走线延时、器件延时、FPGA输入管脚延时,导致

2018-08-02 16:03:00 1858

1858

本文采用ADC+高频时钟电路+FPGA+DSP的结构模式,设计了一种实时采样率为2 Gsps的数字存储示波器数据采集系统,为国内高速高分辨率的数据采集系统的研制提供了一个参考方案。

2019-05-03 09:19:00 5271

5271

该电路采取先切断接收机供电电源再通电的方法,使卫星接收机自动恢复正常工作,整个处理过程不需要人工干预。

2018-09-27 14:54:00 3017

3017

介绍了一种用FPGA实现对高速A/D转换芯片的控制电路,讨论了这一控制电路设计思想,提出了更好地解决高速A/D采样与较慢速的单片机数据处理间矛盾的链接方法。

2018-09-21 17:00:29 26

26 的信息是很重要的,它正好对应着信号发生变化的地方,接收端的数据时钟恢复电路利用此信息将与发端同步的时钟恢复出来,然后再延迟一点时间后读入状态信息,就可以得到与发端相同的J/K数据流,再经过反向的NRZI编码,原始数据就可以被恢复出来了。

2019-10-10 09:02:01 7234

7234

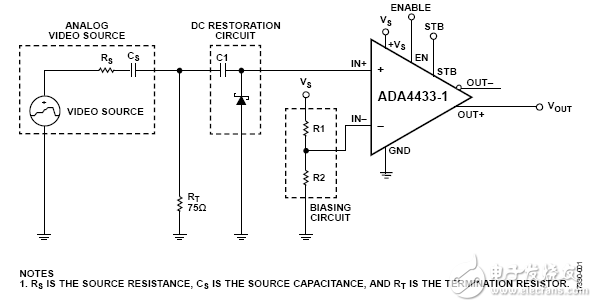

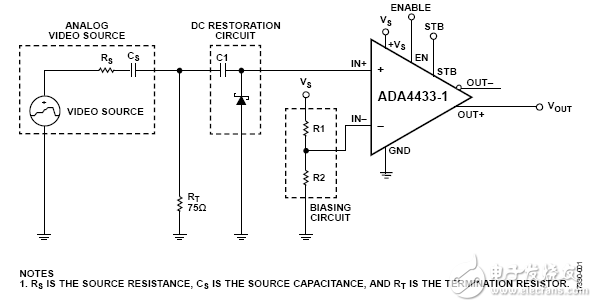

驱动电路是典型的交流耦合信号,以对器件提供隔直处理。视频信号的直流电平代表黑色的显示等级,该电平必须恒定才能适应视频处理电路。 本应用笔记说明恢复复合视频信号的正确直流电平的方法。 图 1. 使用 ADA4433-1 的直流恢复电路原理图 复合视频信号说明 复合视频信号也

2019-08-22 12:53:31 2935

2935

介绍了一种基于四相关器结构的2.5gb/s 15 mW时钟恢复电路的设计。该电路采用鉴相和鉴频相结合的方法,将微分、全波整流、混频等高速运算结合在一起,降低了功耗。此外,采用两级压控振荡器,该振荡器

2020-06-29 08:00:00 1

1 无源 UHF RFID 芯片的设计难点是围绕着如何提高芯片的读写距离、降低标签的制造成本展开的。因此,提高电源恢复电路 的效率,降低整体芯片的功耗,并且工作可靠仍然是 RFID 标签芯片设计主要的挑战。

2020-12-29 18:47:29 25

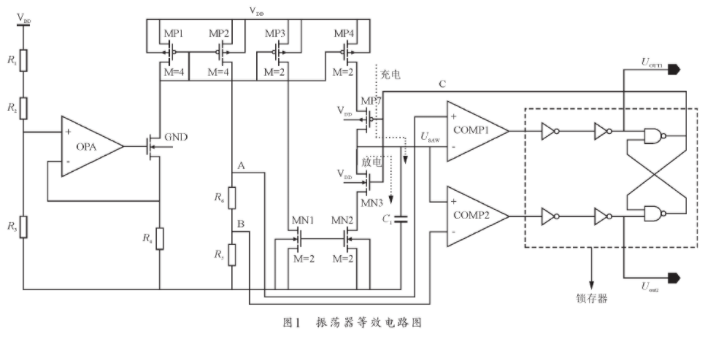

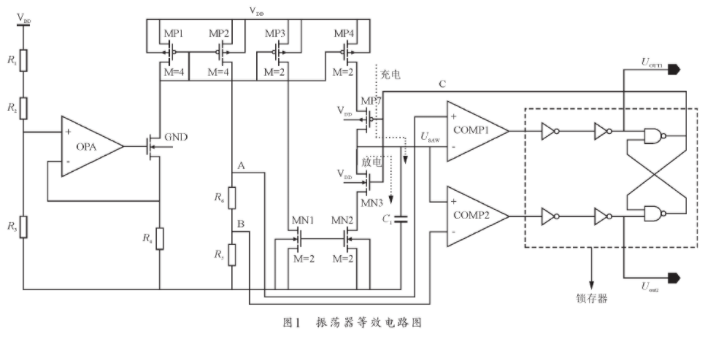

25 振荡器作为现代电子系统的重要组成部分,被广泛应用于时钟同步电路、无线通信收发器中的频率综合器、光通信中的时钟恢复电路(CRC,clock recovery circuit),以及多相位采样电路中。振荡器按实现电路元件分为RC振荡器、LC振荡器和石英晶体振荡器。

2020-12-07 08:46:00 1307

1307

介绍一种基于Actel公司Fusion StartKit FPGA的线阵CCD图像数据采集系统。以FPGA作为图像数据的控制和处理核心,通过采用高速A/D、异步FIFO、UART以及电平转换、放大

2021-02-02 17:12:32 5

5 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

2022-02-09 10:43:43 6

6 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2022-02-11 15:05:26 8

8 本文讨论从GSM到OC-192及更高版本的高速串行通信的时钟数据恢复(CRD)。它解释了如何通过典型链接转换和重新捕获数据。本文还研究了不同的CDR方案以及参考振荡器在通信链路发射端和接收端的作用。

2023-06-10 14:49:44 940

940

Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路

2023-07-29 16:47:04 468

468

域时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。 FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路

2023-10-18 15:23:51 578

578 器件损坏。为了保护二极管不受反向击穿的影响,可以使用二极管反向恢复电路。 二极管反向恢复电路是一种用于减小反向恢复电流的电路,通常由二极管和电感器构成。当二极管处于正向导通状态时,电感器存储了能量;当二极管从导

2023-12-18 11:23:57 597

597

电子发烧友App

电子发烧友App

评论