随着EDA威廉希尔官方网站

的高速发展, 以大规模和超大规模器件FPGA/CPLD为载体、以VHDL(硬件描述语言)为工具的电子系统设计越来越广泛。有限状态机(简称状态机)作为数字系统控制单元的重

2010-09-07 18:07:56 1999

1999

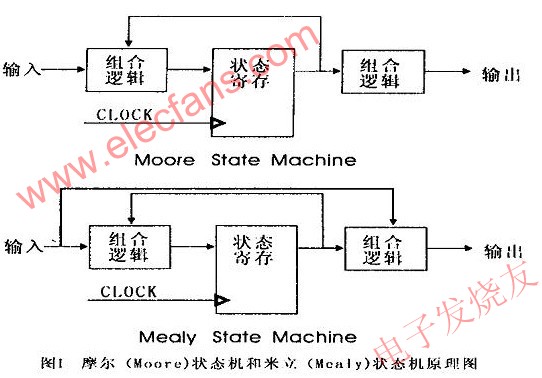

安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。本文主要介绍如何在FPGA中实现状态机

2013-03-29 15:02:57 12361

12361

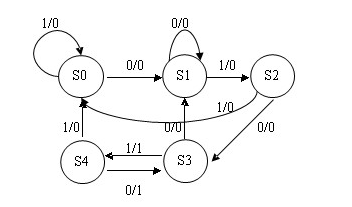

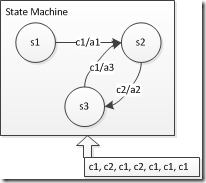

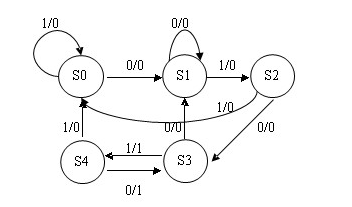

首先可以确定采用米利型状态机设计该电路。因为该电路在连续收到信号0101时,输出为1,其他情况下输出为0,所以采用米利型状态机。

2020-09-08 14:06:59 7422

7422

状态机建模是使用状态图和方程式的手段,创建基于混合信号的有限状态机模型的一种建模工具。

2023-12-05 09:51:02 430

430

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

2024-02-12 19:07:39 1818

1818

CPLD威廉希尔官方网站

在微机保护装置中应用的优越性CPLD状态机抗干扰控制原理是什么微机保护控制接口装置的CPLD抗干扰设计

2021-04-29 06:45:33

关于有限状态机的总结资料,比较全面,特别分享下。

2016-04-16 13:22:10

关系,因而在状态图中每条转移边需要包含输入和输出的信息。状态编码 数字逻辑系统状态机设计中常见的编码方式有:二进制码(Binary码)、格雷码(Gray码)、独热码(One-hot码)以及二一十进制码(BCD

2012-03-09 10:04:18

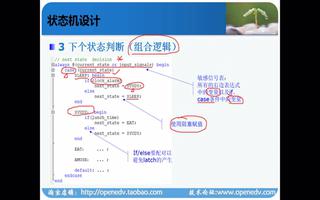

今天给大侠带来如何写好状态机,状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以很多公司在硬件工程师及逻辑工程师面试中,状态机设计几乎是必选题目。本篇在引入状态机设计思想

2020-09-28 10:29:23

(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA威廉希尔官方网站

的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无处不在.在FPGA/CPLD设计中,状态机是最典型

2012-01-12 10:48:26

FPGA状态机的文书资料

2014-09-14 19:01:20

(41)FPGA状态机一段式1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA状态机一段式5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 06:45:18

1.1 FPGA状态机跑飞原因分析1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA状态机跑飞原因分析;5)结束语。1.1.2 本节引言“不积跬步,无以至千里;不积小流

2021-07-29 06:15:53

FPGA状态机为什么会跑飞呢?FPGA状态机跑飞的原因是什么?

2021-11-01 07:52:44

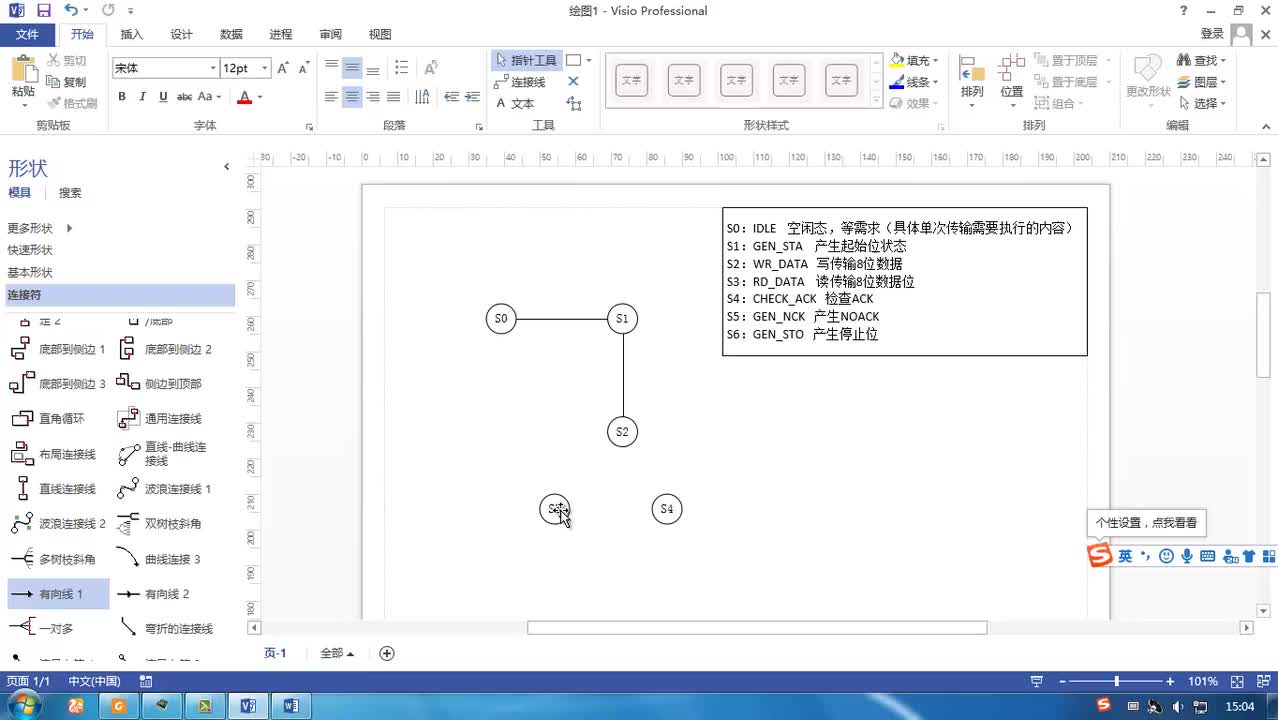

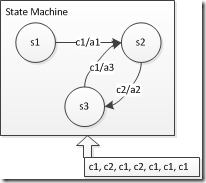

刚学习状态机,跟着视频教程来的,但是图中最后一个状态出现两个圈,但教程里面没有,我不知道内部的那个圈代表什么意思,群里问没人回答,只好发帖了,懂的大神帮回答一下,谢谢

2017-11-13 10:35:30

FPGA有限状态机

2013-09-08 08:45:17

主要是状态机如何的运用,有啥经验可以分享的?

2015-09-15 20:06:06

刚开始学fpga,读资料,有些名词不太理解,比如状态机,我只知道fpga就是由查找表和触发器构成的,状态机这个概念是怎么提出来的,干什么使得,求大神讲解,什么情况下用到

2013-04-25 18:35:55

也可能伴随着状态的转移。在状态机中,时间序列也是非常重要的一个因素,从硬件的角度看,时间序列如同一个触发脉冲序列或同步信号,而从软件的角度看,时间序列就是一个定时器。状态机由时间序列同步触发,定时检测

2008-07-10 18:00:24

状态机设计指导

2012-08-20 23:45:55

本帖最后由 eehome 于 2013-1-5 09:56 编辑

状态机设计的例子

2012-08-19 23:01:07

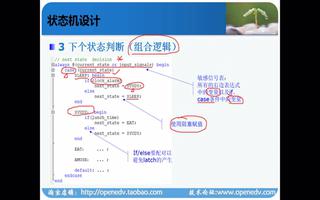

状态机设计中always @(*) beginnext = 2'bx;case (state)idle: next=s1;s1: next=s2;s2: next=idle;end以上代码先给

2021-10-06 18:49:10

大家熟悉在CPLD/FPGA 开发中一个关键的威廉希尔官方网站

——状态机,并且简单介绍了一下RTL 视图的使用。第三讲:加/减计数器例程,讲解了计数器的VHDL 语言的设计过程,以及硬件下载的方法,并且可以通过

2020-05-14 14:50:30

本帖最后由 afnuaa 于 2017-5-24 11:22 编辑

状态机是一种普遍而有效的架构,我们可以利用状态机设计模式来实现状态图或流程图的算法。State Machines

2017-05-23 17:11:34

事件+事件结构今天和大家分享的是前两个状态机在实战中的应用!大致项目要求:1.能在指定位置(可更改)读取csv文件。2.获取csv文件中多个位置的值(0或1),都为1是显示结果PASS,否则FAIL3.

2018-12-25 16:53:35

。一般推荐在CPLD中由于提供较多的组合逻辑资源多使用前者,FPGA中提供较多的时序逻辑而多用后者。状态机描述方式,可分为一段式、两段式以及三段式。一段式,整个状态机写到一个always模块里面,在该

2016-12-26 00:17:38

笔试时也很常见。[例1] 一个简单的状态机设计--序列检测器序列检测器是时序数字电路设计中经典的教学范例,下面我们将用Verilog HDL语言来描述、仿真、并实现它。序列检测器的逻辑功能...

2022-02-16 07:29:49

最近在CPLD里面做了一个4通道的模块,每个模块内都有一个状态机,开始我是用的一段式状态机写发,资源不够,然后我将状态机的写法改为3段式,(将状态转换一段,输出一段)发现资源降低了很多,问下,一段和三段式的状态机为什么对占用资源会有影响?或者谈谈一段和三段的综合情况?

2015-01-21 14:07:40

产生新代码,只会在状态机中设置不同的寄存器状态。 正是由于这样的过程,数字电源的功能仍然由数字电源控制器IC的数据手册规定,没有任何软件或代码需要验证。 图形用户界面和状态机的组合可简化数字电源领域

2018-10-09 10:36:37

所示。这些更改不会为微控制器产生新代码,只会在状态机中设置不同的寄存器状态。正是由于这样的过程,数字电源的功能仍然由数字电源控制器IC的数据手册规定,没有任何软件或代码需要验证。图形用户界面和状态机

2018-10-18 11:25:17

,只会在状态机中设置不同的寄存器状态。正是由于这样的过程,数字电源的功能仍然由数字电源控制器IC的数据手册规定,没有任何软件或代码需要验证。图2. 基于状态机的ADP1055框图图形用户界面和状态机的组合

2018-10-16 12:56:53

单片机易于与SRAM或ROM接口。这种方式首先由FPGA/CPLD与接口的高速A/D等器件进行高速数据采样并将数据暂存于SRAM中。采样结束后通过切换使单片机与SRAM以总线方式进行数据通信以便发挥

2018-12-10 10:18:34

的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入状态机设计思 想的基础上,重点讨论如何写好状态机。 本文主要内容如下: 状态机的基本概念; 如何写好状态机; 使用 Synplify Pro 分析 FSM。[hide] [/hide]

2011-10-24 11:43:11

本文给出了采用这些威廉希尔官方网站

的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。

2021-04-30 06:12:56

1.状态机设计原则2.状态机练习13.状态机练习1答案4.波形对比方法5.状态机练习26.状态机练习2答案7.状态机练习38.状态机练习3答案9.状态机练习410.状态机练习4答案11.状态机练习

2015-10-31 13:52:12

的下降沿诱发数据传输,而在上升沿指明只有一个数据或只剩下一个数据;(6)读操作比写操作多一个中间准备过程。 3 基于CPLD的状态机设计3.1 状态机的构造根据对上述时序图的分析,完成一个简易PCI总线

2019-06-17 05:00:11

`书上说这是设计复杂状态机的方法,但是我分析一下,这种状态机设计的方法和一般用always和case设计的状态机的结果是不一样的,那么这种状态机有没有实际应用的价值,毕竟他和正常的状态机不一样,另外

2015-01-17 17:42:40

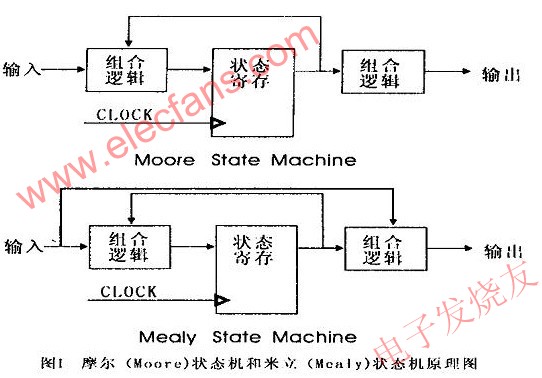

越办越好!今天我们来写状态机。关于状态机呢,想必大家应该都接触过,通俗的讲就是数电里我们学的状态转换图。状态机分为两中类型,一种叫Mealy型,一种叫Moore型。前者就是说时序逻辑的输出不仅取决于

2015-04-07 17:21:32

本帖最后由 eehome 于 2013-1-5 09:56 编辑

高效安全的状态机设计

2012-08-13 17:53:44

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

2009-06-14 19:24:49 96

96 状态机设计:8.1.1 数据类型定义语句TYPE语句的用法如下:TYPE 数据类型名IS 数据类型定义OF 基本数据类型;或TYPE 数据类型名IS 数据类型定义;TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_L

2009-08-09 23:07:03 36

36 通过分析工控系统的特性,提出采用状态机的思想进行工控软件设计。详细论述了高速状态机的错步问题以及控制层中状态机的状态划分问题。结合具体的应用实例,给出了基于状

2009-08-10 14:26:08 30

30 状态机举例

你可以指定状态寄存器和状态机的状态。以下是一个有四种状态的普通状态机。 // These are the symbolic names for states// 定义状态的符号名称parameter [1

2009-03-28 15:18:28 893

893 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA威廉希尔官方网站

的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无

2010-09-10 17:30:27 1272

1272

有限状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数,传统的电路图输入法通过直接设计寄存器组来实现各个状态之间的转换, 而用硬件描述语言来描述有限

2011-11-11 09:49:28 1886

1886

本文给出了采用这些威廉希尔官方网站

的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。

2011-12-16 10:09:43 1296

1296

为了能够更简洁严谨地描述MTM总线的主模块有限状态机的状态转换,同时减少FPGA芯片功耗,提高系统稳定性,文中在分析MTM总线结构和主模块有限状态机模型的基础上,基于VHDL语言采

2012-05-29 15:39:09 20

20 状态机代码生成工具状态机代码生成工具状态机代码生成工具状态机代码生成工具

2015-11-19 15:12:16 9

9 状态机原理及用法状态机原理及用法状态机原理及用法

2016-03-15 15:25:49 0

0 本文详 细论述了高速状态机的错步问题以及控制层中状态机的状态划分问题,结合具体的应用实例,给出了基于状态机的实现方法。

2016-03-22 15:48:30 3

3 本文提出一种优秀 、高效的 Verilog HDL 描述方式来进行有限状态机设计 介绍了 有限状态机的建模原则 并通过一个可综合的实例 验证了 该方法设计的有限状态机在面积和功耗上的优势。

2016-03-22 15:19:41 1

1 EDA的有限状态机,广义而言是指只要涉及触发器的电路,无论电路大小都可以归结为状态机。有限状态机设计在学习EDA时是很重要的一章。

2016-06-08 16:46:10 3

3 FPGA学习资料教程——华清远见FPGA代码-状态机

2016-10-27 18:07:54 9

9 练习九.利用状态机的嵌套实现层次结构化设计目的:1.运用主状态机与子状态机产生层次化的逻辑设计;

2017-02-11 05:52:50 3126

3126

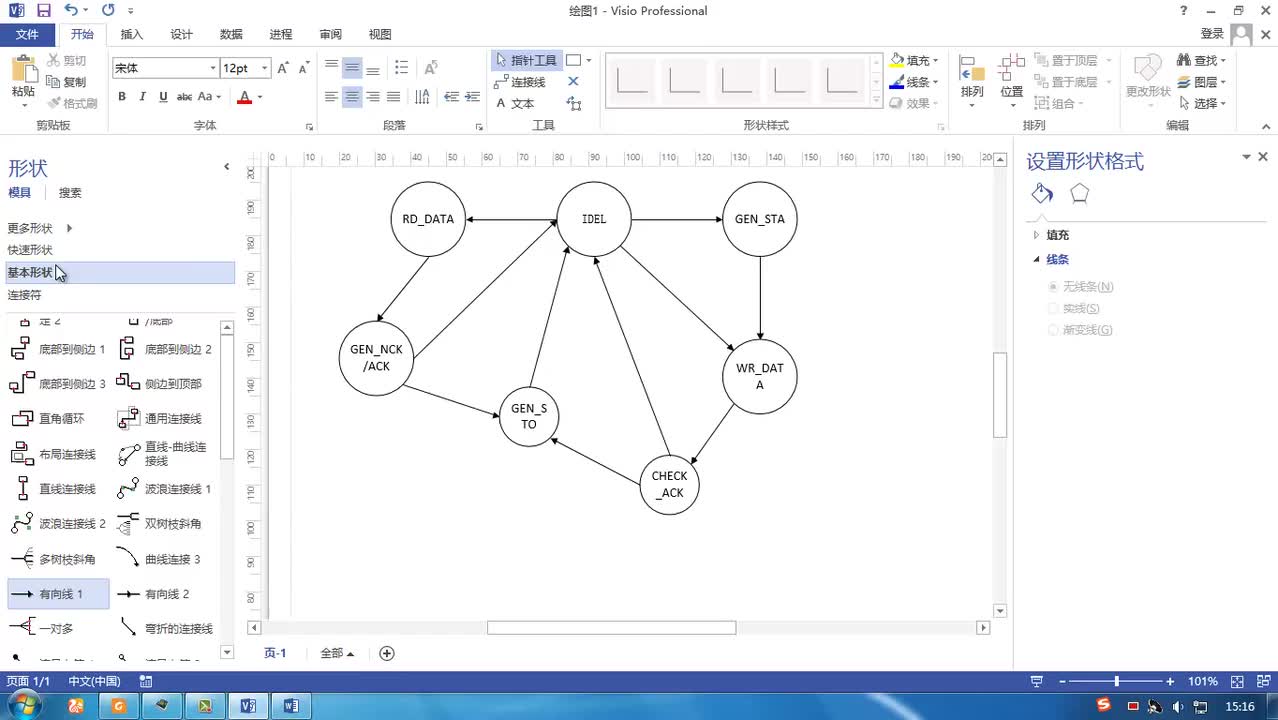

状态机,并通过解析各阶段数据状态变化,验证了各节点通信数据的正确性。实验结果表明,基于上述状态机的FPGA实现EtherCAT从站基本通信链路是完全可行的。

2017-11-15 12:04:01 17163

17163

在FPGA/CPLD设计中频繁使用的状态机,常出现一些稳定性问题,本文提出了一些解决方法,实验表明该方法有效地提高了综合效率. 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件

2017-11-24 20:59:08 2364

2364

设计背景: 状态机是描述各种复杂时序的时序行为,是使用 HDL进行数学逻辑设计中非常重要的方法之一,状态机分为摩尔机和米粒机,当输出只和状态有关系的话称为摩尔机,当输出不仅和状态有关系也和输入信号

2018-06-01 16:59:43 6979

6979

如何使用QII状态机向导创建一个状态机

2018-06-20 00:11:00 3940

3940

本篇文章包括状态机的基本概述以及通过简单的实例理解状态机

2019-01-02 18:03:31 9928

9928

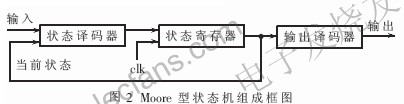

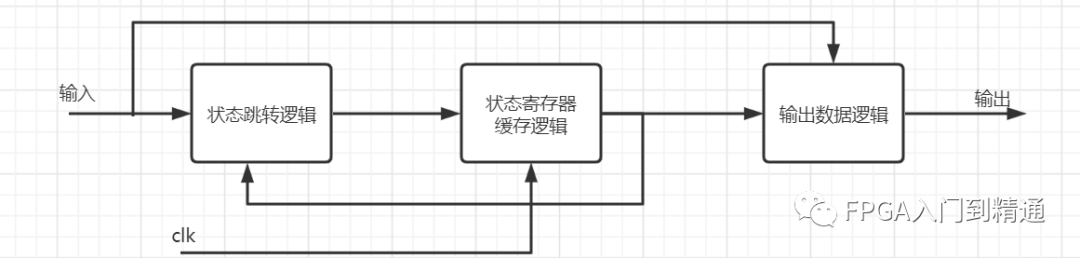

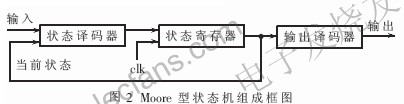

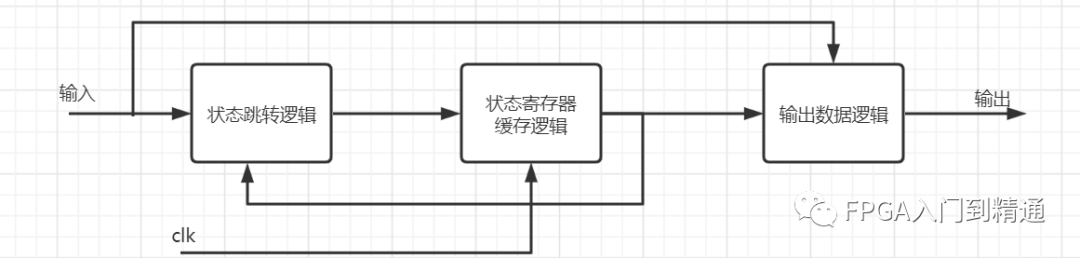

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-09-19 07:00:00 2178

2178

状态机可以用两种方法实现:竖着写(在状态中判断事件)和横着写( 在事件中判断状态)。这两种实现在本质上是完全等效的,但在实际操作中,效果却截然 不同。

2019-10-09 07:09:00 2304

2304 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-10-09 07:07:00 3198

3198 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:06:00 2234

2234 关于状态机的一个极度确切的描述是它是一个有向图形,由一组节点和一组相应的转移函数组成。状态机通过响应一系列事件而“运行”。每个事件都在属于“当前” 节点的转移函数的控制范围内,其中函数的范围是节点

2019-10-09 07:05:00 3387

3387 状态机有三种描述方式:一段式状态机、两段式状态机、三段式状态机。下面就用一个小例子来看看三种方式是如何实现的。

2019-08-29 06:09:00 2514

2514

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-12-04 07:04:00 2900

2900

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:02:00 2137

2137 状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。“现态”和“条件”是因,“动作”和“次态”是果。

2019-10-09 07:04:00 1879

1879 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-05-28 07:03:49 2648

2648 状态机 1、状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。 2、根据状态机的输出

2020-11-16 17:39:00 24811

24811 是FPGA设计中一种非常重要、非常根基的设计思想,堪称FPGA的灵魂,贯穿FPGA设计的始终。 02. 状态机简介 什么是状态机:状态机通过不同的状态迁移来完成特定的逻辑操作(时序操作)状态机是许多数字系统的核心部件, 是一类重要的时序逻辑电路。通常包括三个部分: 下一个

2020-11-05 17:58:47 6145

6145

本文档的主要内容详细介绍的是如何使用Moore状态机设计一序列检测计实验的工程文件免费下载

2020-12-04 16:46:23 9

9 有限状态机的设计是HDL Designer Series™工具的关键应用。 尽可能地对于设计人员编写导致状态机性能不佳的VHDL,可以使用HDL Designer用于生成VHDL的Series™工具

2021-04-08 10:05:23 3

3 玩单片机还可以,各个外设也都会驱动,但是如果让你完整的写一套代码时,却无逻辑与框架可言。这说明编程还处于比较低的水平,你需要学会一种好的编程框架或者一种编程思想!比如模块化编程、状态机编程、分层思想

2021-07-27 11:23:22 19223

19223

经典双进程状态机的FPGA实现(含testbeach)(肇庆理士电源威廉希尔官方网站

有限公司图片)-该文档为经典双进程状态机的FPGA实现(含testbeach)总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-31 13:26:52 3

3 用状态机设计A_D转换器ADC0809的采样控制电路实验(通信电源威廉希尔官方网站

期刊版面费)-用状态机设计A_D转换器ADC0809的采样控制电路.适合新手学习参考

2021-09-16 12:05:05 28

28 以前写状态机,比较常用的方式是用 if-else 或 switch-case,高级的一点是函数指针列表。最近,看了一文章《c语言设计模式–状态模式(状态机)》(来源:embed linux

2021-12-16 16:53:04 7

7 (41)FPGA状态机一段式1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA状态机一段式5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:59 0

0 FSM有限状态机,序列产生,序列检测,是FPGA和数字IC相关岗位必须要掌握的知识点,在笔试和面试中都非常常见。

2022-03-14 17:42:09 12857

12857 今天还是更新状态机,状态机基本是整个HDL中的核心,合理、高效地使用状态机,是数字电路中的重要技能。

2023-02-12 10:21:05 542

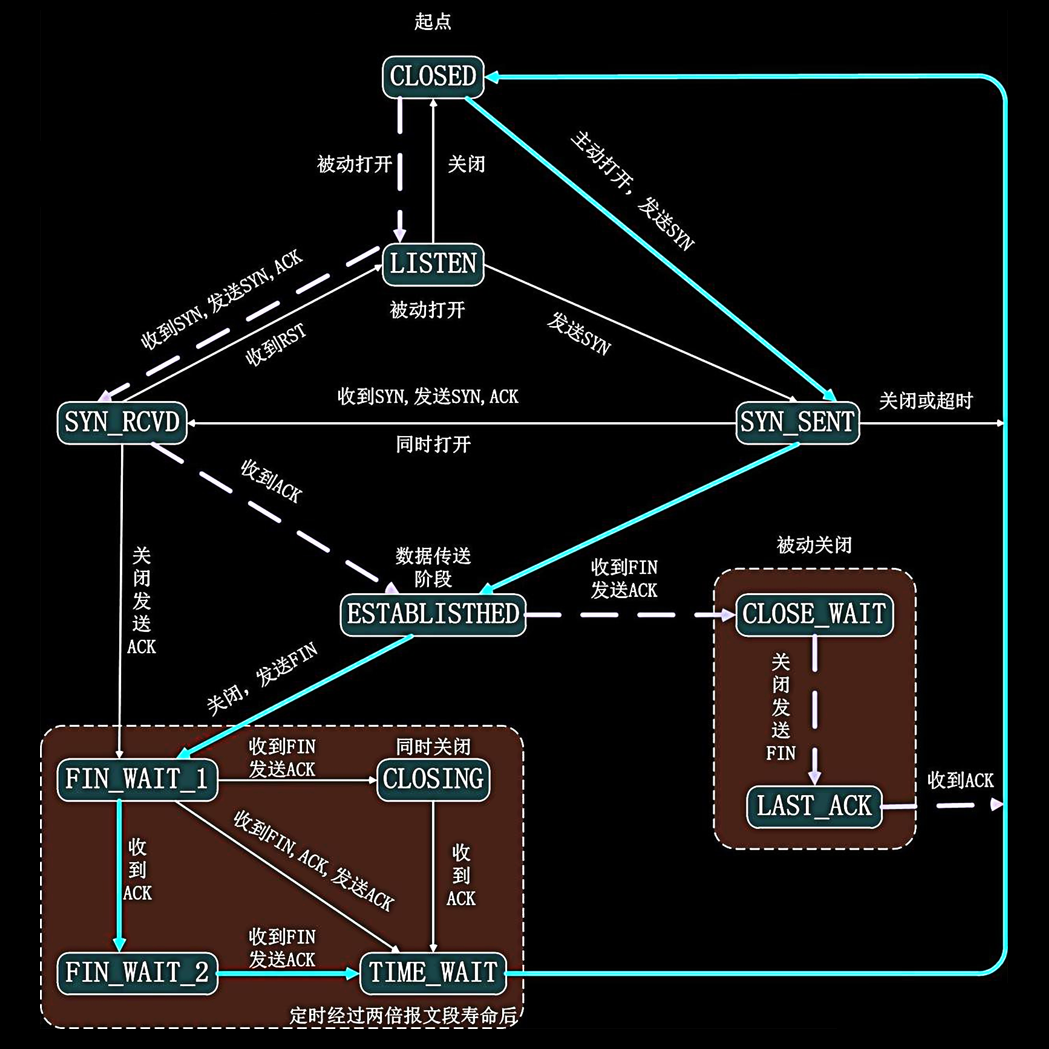

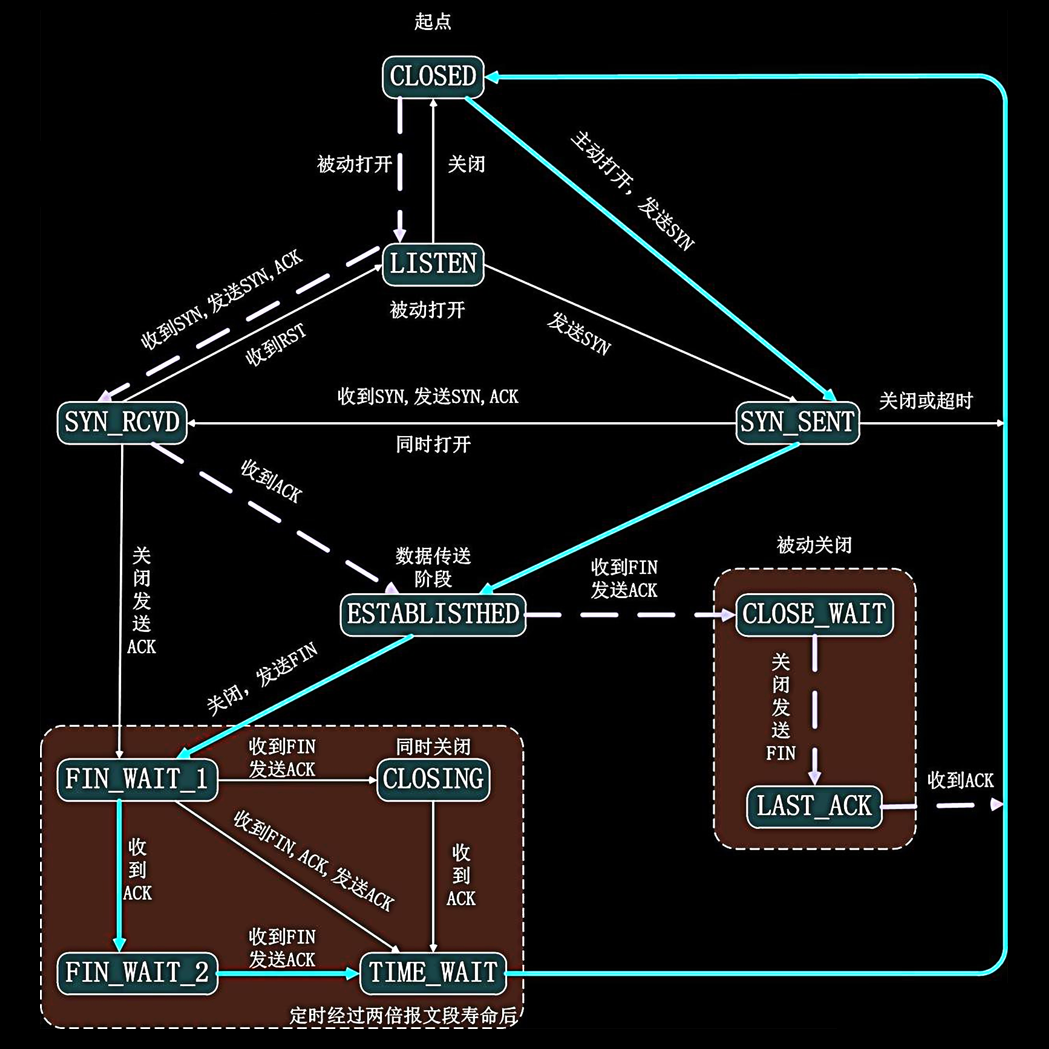

542 TCP状态机是TCP连接的变化过程。TCP在三次握手和四次挥手的过程,就是一个TCP的状态说明,由于TCP是一个面向连接的,可靠的传输,每一次的传输都会经历连接,传输,关闭的过程,无论是哪个方向的传输,必须建立连接才行,在双方通信的过程中,TCP的状态是不一样的

2023-04-21 11:47:57 1005

1005

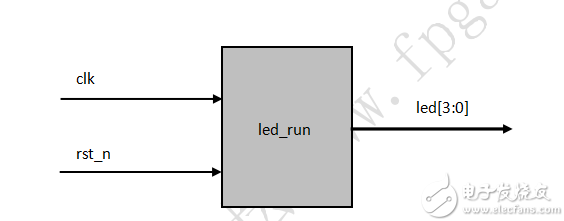

FPGA的特点是并行执行,但如果需要处理一些具有前后顺序的事件,就需要使用状态机。

2023-05-22 14:24:12 559

559

状态机模式是一种行为模式,通过多态实现不同状态的调转行为的确是一种很好的方法,只可惜在嵌入式环境下,有时只能写纯C代码,并且还需要考虑代码的重入和多任务请求跳转等情形,因此实现起来着实需要一番考虑

2023-06-22 14:26:00 411

411

状态机往往是FPGA 开发的主力。选择合适的架构和实现方法将确保您获得一款最佳解决方案。 FPGA 常常用于执行基于序列和控制的行动, 比如实现一个简单的通信协议。对于设计人员来说,满足这些行动

2023-07-18 16:05:01 499

499

状态机的基础知识依然强烈推荐mooc上华科的数字电路与逻辑设计,yyds!但是数电基础一定要和实际应用结合起来,理论才能发挥真正的价值。我们知道FPGA是并行执行的,如果我们想要处理具有前后顺序的事件就需要引入状态机。

2023-07-28 10:02:04 456

456

有限状态机,简称状态机,通俗的说,就是把全部的情况分成几个场景,这些场景的工作方式明显不同。简单来说就是如下所示的状态转移图

2023-08-31 15:30:49 585

585

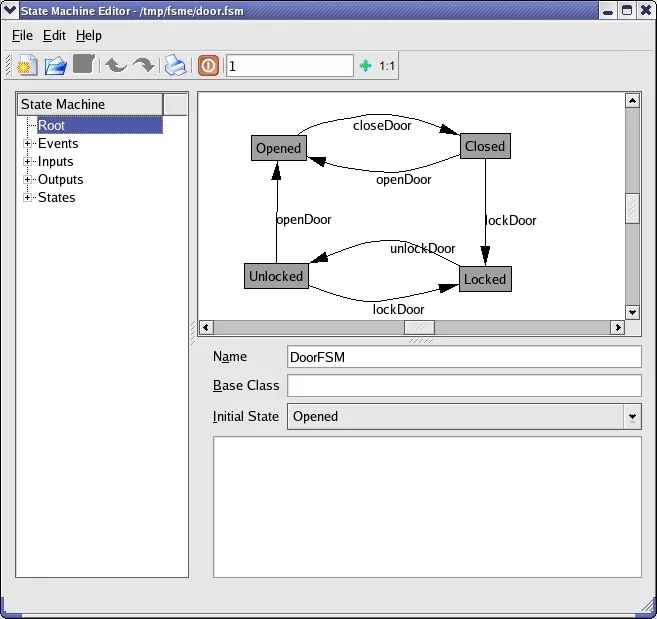

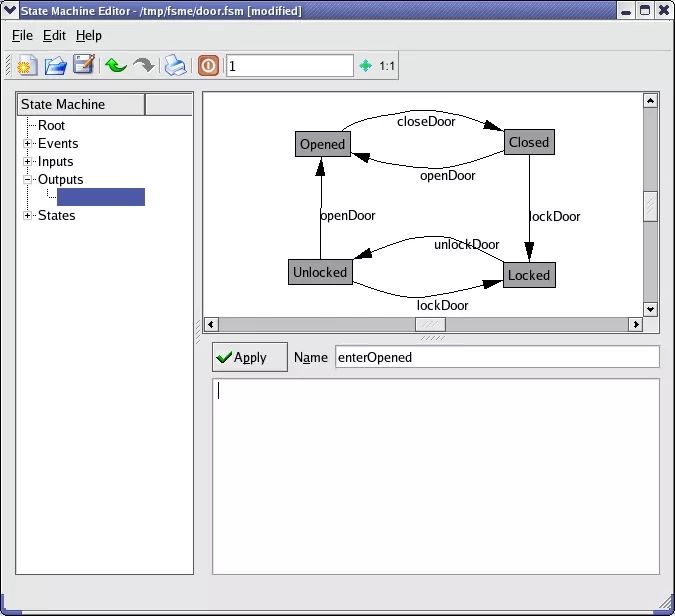

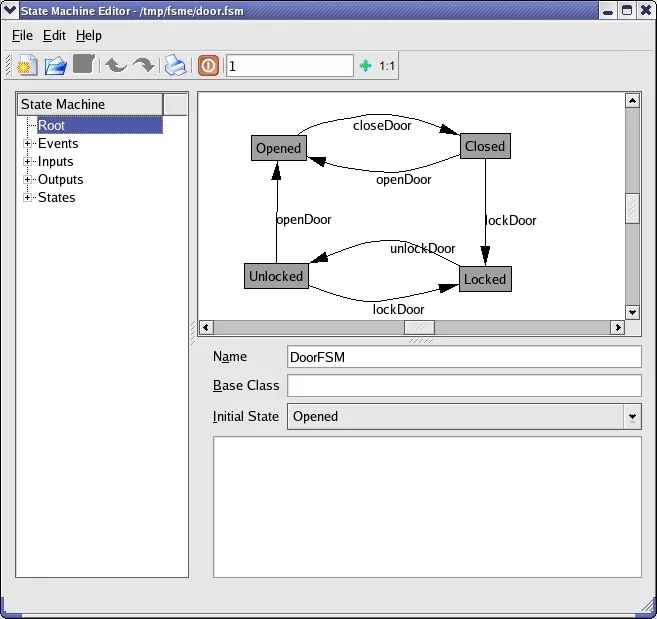

生成状态机框架 使用FSME不仅能够进行可视化的状态机建模,更重要的是它还可以根据得到的模型自动生成用C++或者Python实现的状态机框架。首先在FSME界面左边的树形列表中选择"Root

2023-09-13 16:54:15 618

618

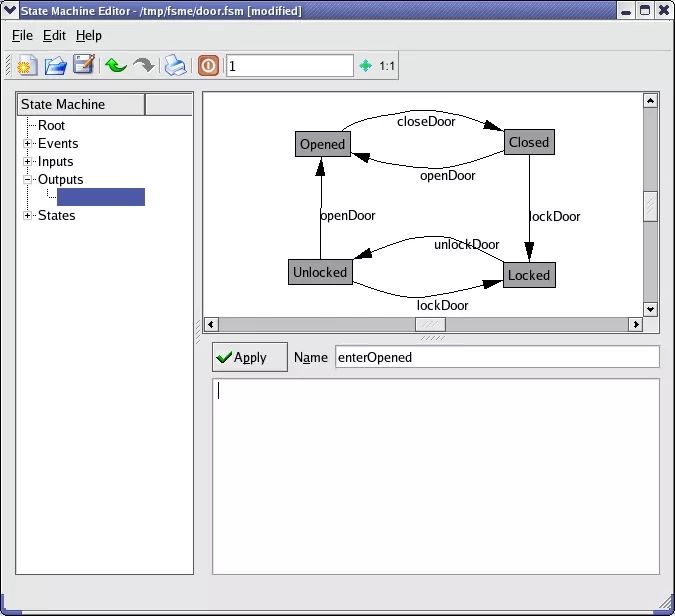

定制状态机 目前得到的状态机已经能够响应来自外部的各种事件,并适当地调整自己当前所处的状态,也就是说已经实现了状态机引擎的功能,接下来要做的就是根据应用的具体需求来进行定制,为状态机加入与软件系统

2023-09-13 16:57:37 821

821

有限状态机分割设计,其实质就是一个状态机分割成多个状态机

2023-10-09 10:47:06 330

330 状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,状态机被广泛应用于各种场景,如CPU指令集、内存控制器、总线控制器等。

2023-10-19 10:27:55 3405

3405

电子发烧友App

电子发烧友App

评论