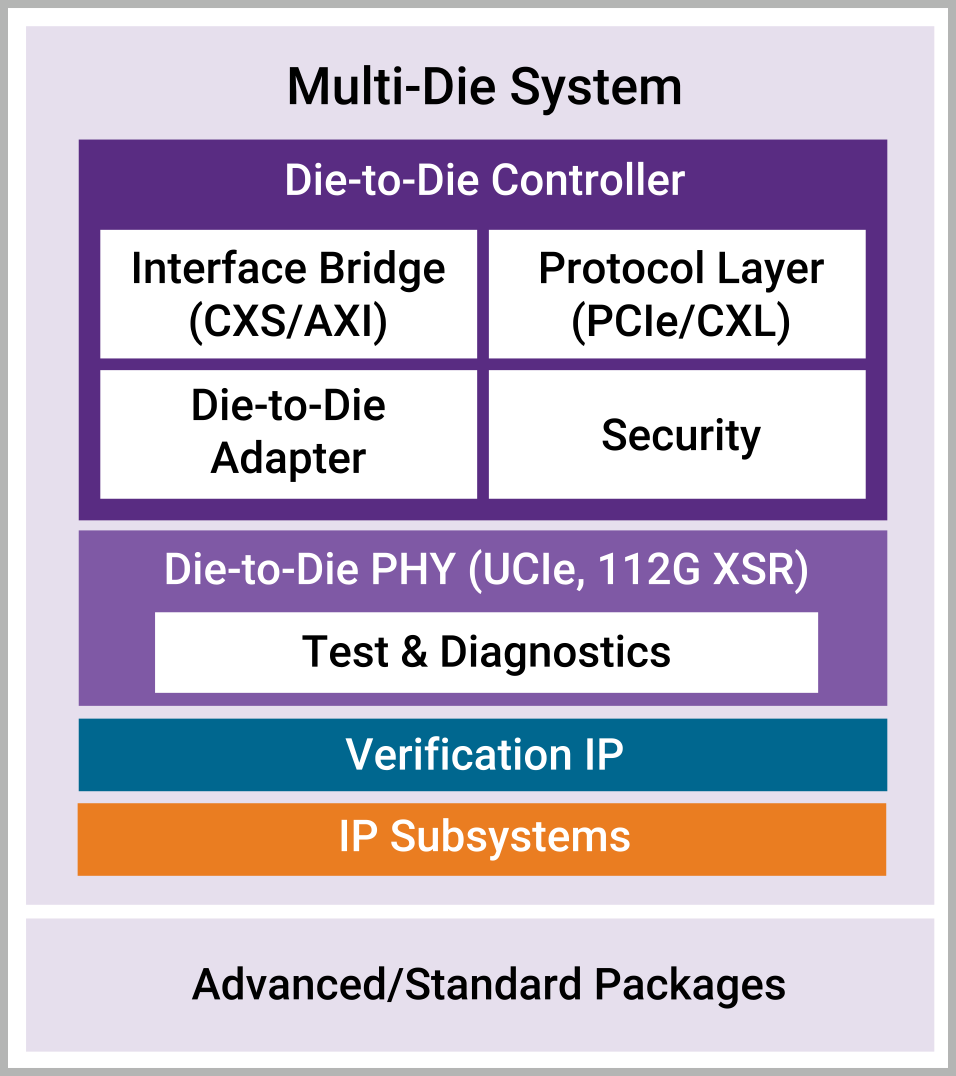

针对Chiplet威廉希尔官方网站 ,去年英特尔、日月光半导体(ASE)、AMD、Arm、谷歌云、Meta、微软、高通、三星和台积电为了统一相关的威廉希尔官方网站 标准组建了UCIe(通用芯粒高速互连)联盟。该联盟推出的UCIe标准对封装内芯粒(Chiplet)之间的互连进行了规范和约束,以实现封装层级的开放芯粒生态系统和普遍的互连。 其中UCIe联盟成员共分为三个级别分别是发起人、贡献者、采用者。发起人由董事会组成并具有领导作用,贡献者和发起者公司可以参与工作组,而采用者只能看到最终规范并获得知识产权保护。 目前UCIe联盟已经拥有了超过100名成员,阿里巴巴、芯耀辉、芯动科技、芯云凌、长鑫存储、长电科技等多家国内企业也加入了该联盟,***正式进入到了Chiplet时代。那么Chiplet能否成为***弯道超车的希望?

01 “***”

说起***弯道超车,我想起了最近的一个新闻。

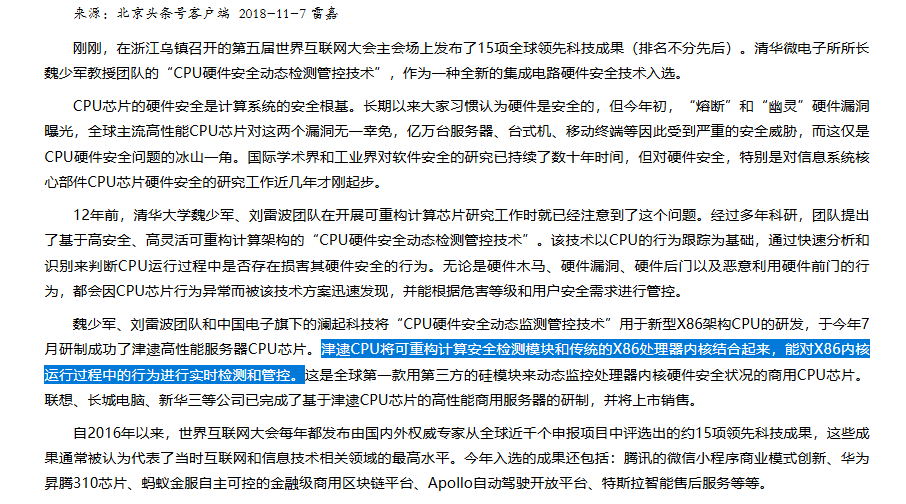

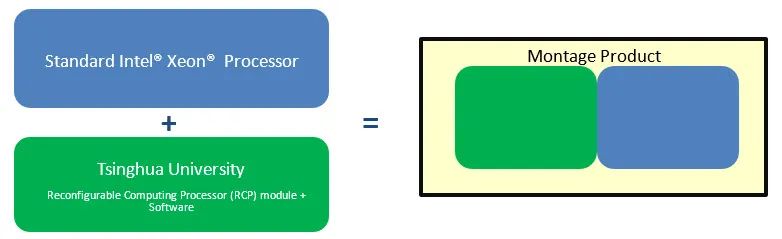

今年1月12日,澜起科技发布了第四代津逮CPU。随后有一些分析文章认为国产处理器追上了英特尔x86处理器。如果单看这个新闻可能有些人会认为我们的***或者说国产CPU“达到了国际先进水平”。但是这其中有很多事情是需要说明的。澜起科技官方是这样描述第四代津逮CPU的: “澜起科技第四代津逮CPU,以英特尔第四代至强可扩展处理器(代号:Sapphire Rapids)为内核,通过了澜起科技安全预检测(PrC)测试,是面向本土市场的x86架构服务器处理器。相较上一代产品,第四代津逮CPU采用先进的Intel 7制程工艺,其最大核心数为48核,最高睿频频率为4.2GHz,最大共享缓存为105MB,关键性能指标大幅提升。” 可能有些读者不太理解“以英特尔处理器为内核,通过了PrC测试”是什么意思。这里我们可以结合清华大学官网上的一篇文章一起分析一下。

这篇文章中指出“津逮CPU将可重构计算安全检测模块和传统的X86处理器内核结合起来,能对X86内核运行过程中的行为进行实时检测和管控。”

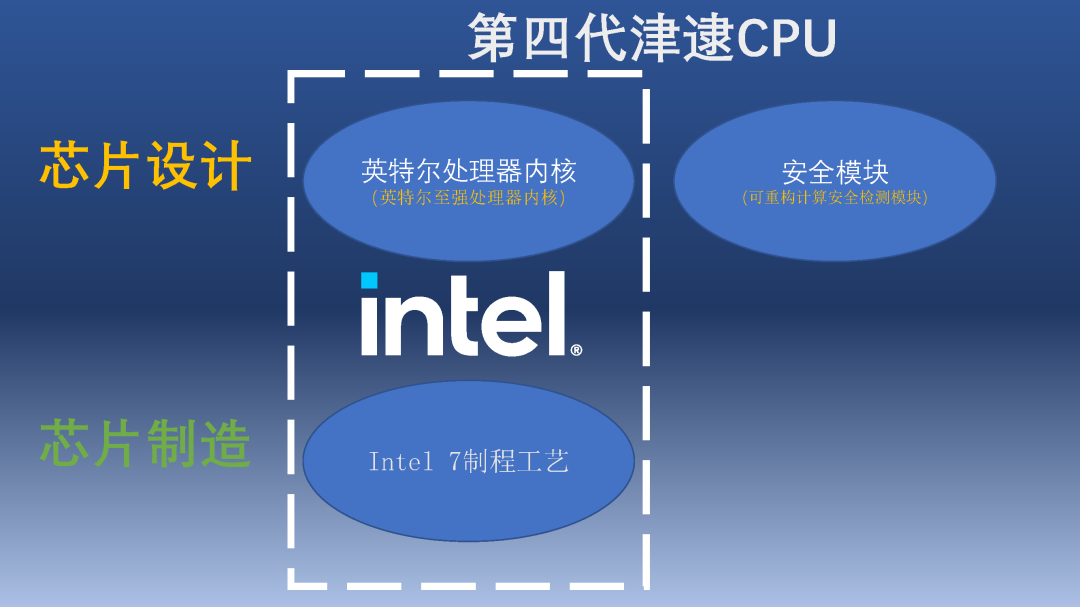

图片来源:英特尔 也就是说第四代津逮CPU可以分成两个部分,一部分是安全模块,另一部分是英特尔X86处理器内核。

而在性能方面,澜起科技官方宣传中有这样的描述“津逮CPU基于英特尔至强处理器内核,其功能、性能及可靠性与至强处理器一致”。所以四代津逮CPU追上了英特尔x86处理器或者说达到了国际领先水平是没问题的。只是这种说法有些奇怪,毕竟津逮CPU的性能部分来自于英特尔处理器内核。也就是说:英特尔处理器内核在性能方面追赶上了英特尔处理器。 另外一个问题就是第四代津逮CPU算不算***了。目前国内“造芯片”可以分成大致两种: 一种是字面意义上的制造芯片,拥有晶圆厂,可以直接生产芯片。 另一种是指像海思那样的Fabless公司,只负责设计芯片,制造部分交给台积电等晶圆厂进行。这种设计芯片的公司在一些情况下也可以算是“造”芯片。

具体到第四代津逮CPU呢?芯片的安全模块是由中国公司设计的,英特尔处理器内核是由英特尔设计的。整个芯片最终是由Intel 7制程工艺制造的。至于第四代津逮CPU到底算不算***,相信不同的读者会有自己的见解。 那么假设我们将“第四代津逮CPU”认定为“***”,那么会是什么情况呢? 2023年1月,英特尔正式发布第四代至强可扩展处理器(代号:Sapphire Rapids),而就在同一月,某***厂商发布了具备“同等性能、功能及可靠性”的“***”。国产CPU完全追上国际大厂水平,***完成了弯道超车。如果作为一篇“沸腾文章”写到这里其实就足够了,如果是一篇“威廉希尔官方网站 分析文章”往往会在这之后告诉你,这个所谓的“国产CPU”里面哪些是国产的,哪些又是进口的。但是从另一个角度看,这样的商业合作确实为***的发展打开了思路。就比如说今天我们在国外原有CPU的基础上加进去了一个安全模块,明天我们可以加入另一个模块。并且我们可以逐渐替换芯片中的非国产部分,这样一来总有一天我们能造出完整的***。 而Chiplet威廉希尔官方网站 恰好可以实现这种发展方式,Chiplet威廉希尔官方网站 的出现允许我们在“造芯片”的时候由浅入深地提高芯片内部使用的“国产成分”比例。

02 Chiplet

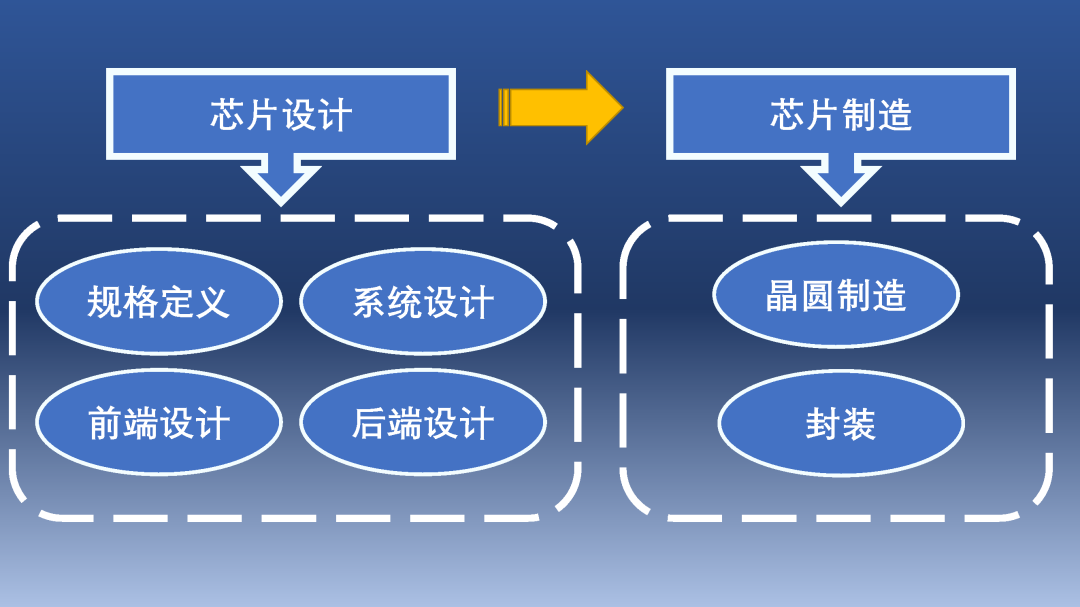

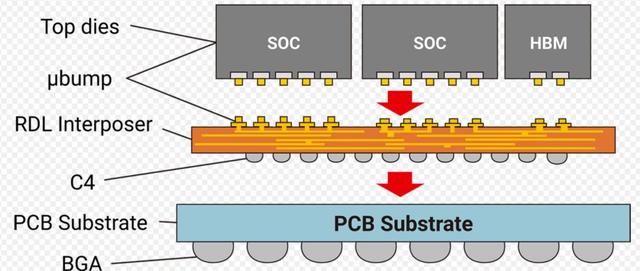

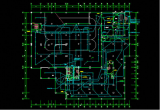

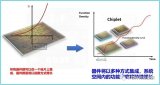

目前不同厂商对于Chiplet都有自己的定义和解释,但大致可以分为两种: 1、Chiplet就是把多个芯片(2个或2个以上)通过封装的方式“整”到一个芯片中。 2、Chiplet就是把多个芯片(2个或2个以上)通过先进封装的方式“整”到一个芯片中。 第一种定义其实和“合封芯片”相同,多个芯片封装到一起就算,第二种定义强调了封装方式必须是“先进封装”才算,例如2.5D封装、3D封装。 一款Chiplet芯片的设计制造流程可以大致分成两个阶段,第一个阶段主要是制造出芯片的Die(裸片),第二个阶段是将多个Die(裸片)进行封装。 (以下对于设计制造流程的描述只是进行粗略的大致描述,且描述过程中可能会以数字逻辑芯片的设计制造流程为主,interwetten与威廉的赔率体系 芯片、存储芯片等其它芯片的相关流程可能不尽相同。) 第一阶段——从图纸到Die: 1、规格定义:我们准备要搞一个芯片了。这个芯片干什么用的?需要实现哪些功能?性能要达到什么程度?成本控制在什么水平?例如这些是这个阶段要确定下来的问题,或者简单来说就是要明确芯片的用途、性能、规格、成本等指标。 2、系统设计:基于前期规划那些指标,这个阶段要明确芯片架构,确定芯片中都包含哪些模块,并且设计好它们之间的连接关系、交互关系。 3、前端设计:基于前面的那些工作,这一步将针对各模块开展具体的电路设计。将会使用硬件描述语言(Verilog或VHDL),对具体的电路实现进行RTL(Register Transfer Level)级别的代码描述。之后用逻辑综合工具,把硬件描述语言写成的RTL级的代码转成门级网表(NetList)。逻辑综合完成后需要进行静态时序分析,需要确保电路在面积、时序等目标参数上达到预设的标准。 在完成前端设计中每一个小步骤时基本都需要经过仿真验证来检验相关设计的正确性。仿真验证如果通过不了,那可能就需要修改设计甚至重新设计。 4、后端设计:基于前面的那些工作,并且结合晶圆厂提供的工艺文件,最终生成用于芯片生产的GDS(Geometry Data Standard)版图。同样在这个阶段也需要进行多次仿真验证。 5、芯片制造/从沙子到Die(裸片):从这个步骤开始,主要就是晶圆厂的工作了。这个步骤大致包括制造晶棒、生产晶圆、对晶圆进行一系列处理(比如薄膜工艺;光刻、刻蚀、去胶等图形化工艺;掺杂工艺;热处理工艺),完成这些之后,需要测试完成处理的晶圆。

举个例子来说,这是一块英特尔至强处理器的晶圆,经过处理后的晶圆大概就是这个样子。我们可以看到这块晶圆上有无数个小的方形块。经过测试之后会将这些小的方形块从晶圆上切下来,切下来的小方形块就是芯片的Die(裸片),Die经过封装之后就是完整的芯片产品了。 第二阶段——从Die到芯片产品:这一阶段主要就是芯片封装,由于芯片的Die是十分脆弱的,所以通常需要用“外壳”包裹一层之后才能作为芯片产品出售。这一阶段也是Chiplet芯片和一般芯片的最大区别,Chiplet芯片会使用1个外壳包装至少2颗Die,而一般芯片往往是1个外壳包装1颗Die。

03 国产与自研

在前文中提到了,Chiplet威廉希尔官方网站 的出现允许我们在“造芯片”的时候由浅入深地提高芯片内部使用的“国产成分”比例。对于企业来说,就是“自研”的比例。那么这个比例是如何提高的呢?

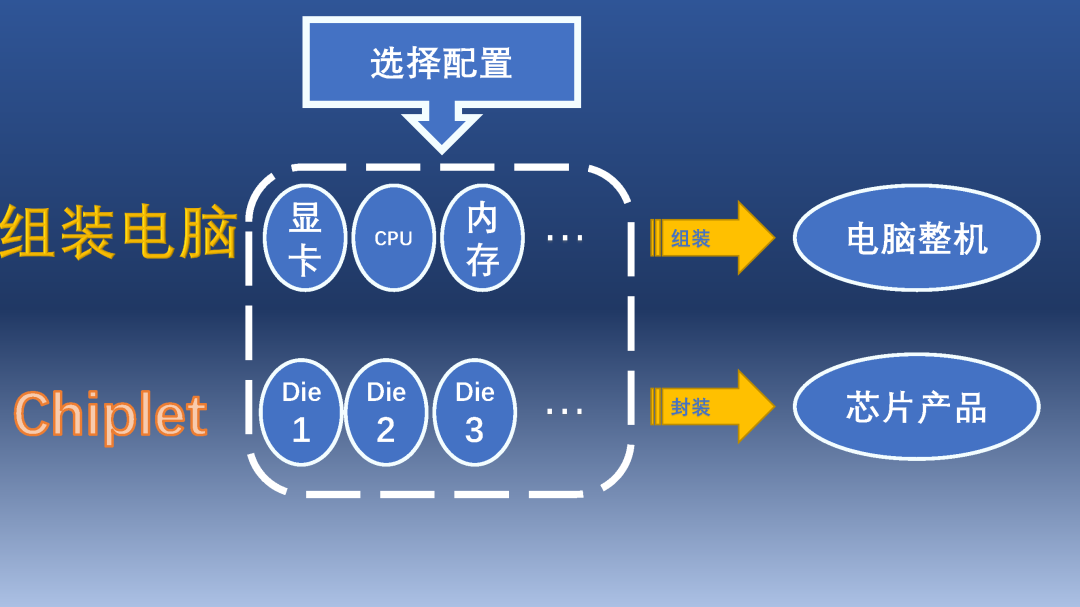

从芯片的制作流程上看,如果一家芯片公司只管芯片设计,那它就是一家Fabless公司,如果一家芯片公司只管芯片制造,那它可能是晶圆厂或者封测厂,如果一家芯片公司既管设计又管制造,那它就是一家IDM公司。但是以上这些公司门槛其实都很高。 但Chiplet威廉希尔官方网站 则不然,它对于公司的威廉希尔官方网站 积累几乎是无最低要求的,甚至说出个主意就可以成为Chiplet芯片公司。当然这个主意肯定不是说,把别人先进芯片上的logo用砂纸打磨掉,印上自己公司的logo。 这里就不得不提到Chiplet威廉希尔官方网站 与UCIe联盟了,如果说未来某个Chiplet威廉希尔官方网站 联盟(例如UCIe联盟)实现并且推广了不同厂商芯片间的“统一接口标准”,那么发布自己品牌的Chiplet芯片就会和组装电脑一样简单。

如果我们要组装一台电脑,那么就需要写一个配置单,具体来说就是决定用什么品牌、什么型号的显卡、CPU、内存等配件。由于这些配件之间连接所使用的接口通用性很强,所以选择的灵活性很高。例如主板上的内存插槽是DDR5的,那么只需要选择任意品牌的任意规格的DRR5内存条一般都能使用。(极少数会出现不兼容的情况)在确定好配置之后购买相应配件进行组装就可以了,自己组装或者委托其它人/其它平台代为组装都可以。如果是电脑公司的话,经过这样流程组装好的电脑可以贴上自己公司的logo并作为“整机”出售。 而Chiplet芯片未来也有可能是类似的流程,先写一个类似芯片配置单的东西,决定用什么品牌、什么型号的Die(裸片),最终将这些Die封装到一起,成为一个独立的芯片产品。如果Chiplet芯片最终发布公司不具备芯片封装能力,还可以委托其它具备封装能力的公司代为封装。 如果再进一步说,有些想要组装电脑的人其实并没有太多组装和硬件搭配的相关知识。他们可以告知商家自己的需求,出售电脑配件的商家往往也乐于根据这些需求提供配置单。这对于Chiplet芯片也许也是一样的,一家公司即使不懂不同Die(裸片)之间应该如何搭配,他们也可以通过Die的出品厂商或者封装厂获得他们需要的“芯片配置单”。所以未来对于Chiplet芯片公司来说,可能真的只需要一个主意就能完成这一切。不过这是Chiplet芯片公司下限而并非上限。 同样是拿组装电脑举例,有很多活跃在电商平台上小规模的“整机”公司,在他们的整机产品中使用的所有配件都可以在零售市场上买到。例如英特尔的CPU、英伟达的显卡,华硕的主板。而大规模的“品牌电脑”公司往往会在一些配件中使用一部分自己的东西,例如自己的主板、自己品牌的内存条。这样使用自己的配件一方面可以形成差异化竞争(这点在笔记本电脑领域尤其凸显),另外一方面可以节约成本,赚取更多的利润。 而对于Chiplet芯片公司也是这样,在规模小的时候可以全部使用别人的Die(裸片),别人的封装威廉希尔官方网站 。不过在公司发展起来之后可以逐渐加入自己东西,比如自己设计一个ISP芯片(图像信号处理器)的Die,然后和其它厂商的Die封装在一起,组成一个SOC芯片。这样这枚SOC芯片里面一部分比例的威廉希尔官方网站 是自己提供的,而且融合了其它厂商的Die,最终芯片产品的综合性能并不差。这样我们在“造芯片”的时候就可以由浅入深地提高芯片内部使用的“自研”比例。

04 Chiplet的其它优势

除了上文中提到的,Chiplet可以一定程度上自由组合不同厂商的Die。除此之外Chiplet还具备一些其它方面的优势。 灵活性高:Chiplet本质上是将不同的Die(裸片)整合到一起,只要每个Die之间的接口兼容,那就可以完成整合。因此除了接口以外对于每个Die其实不会有太多的要求。

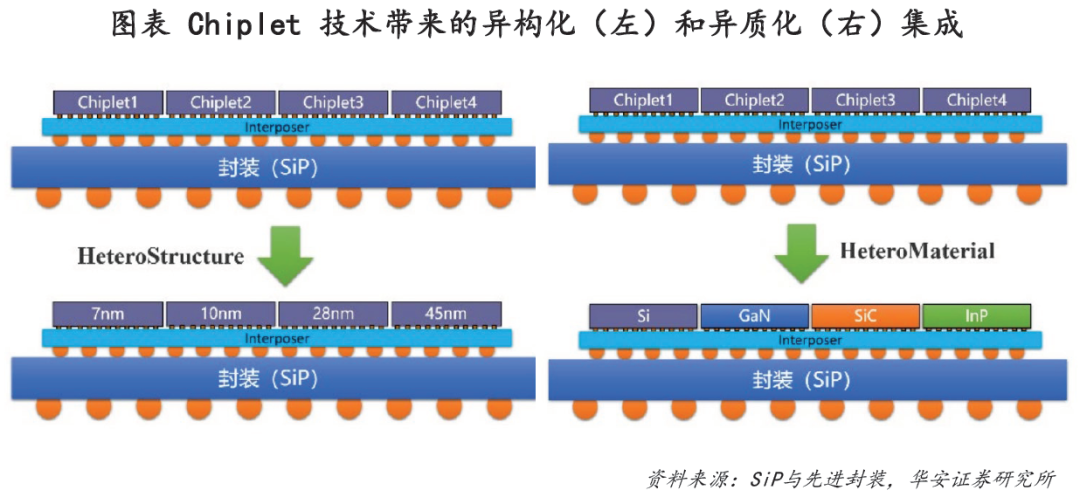

如图所示,Chiplet不光可以使用不同厂商的Die,还可以使用不同工艺甚至不同材质的Die。这样可以使企业在成本和定制化需求方面有更好的选择。例如部分不需要先进工艺的电路可以使用成熟制程制造,这样可以节约成本。 更高的良率:当其它条件相同时,Die的面积越大,良率就会越低。

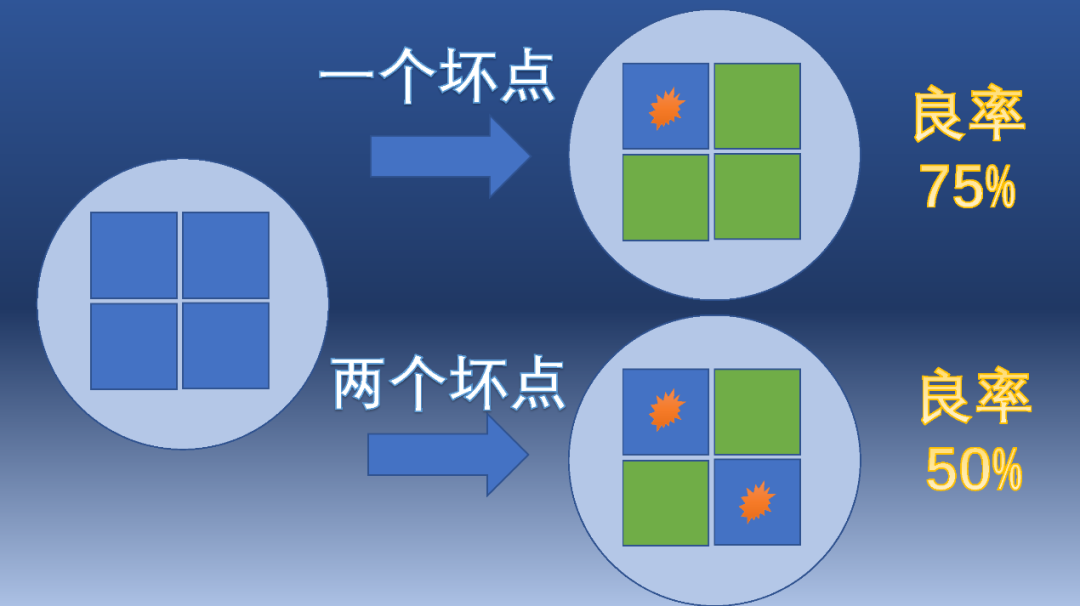

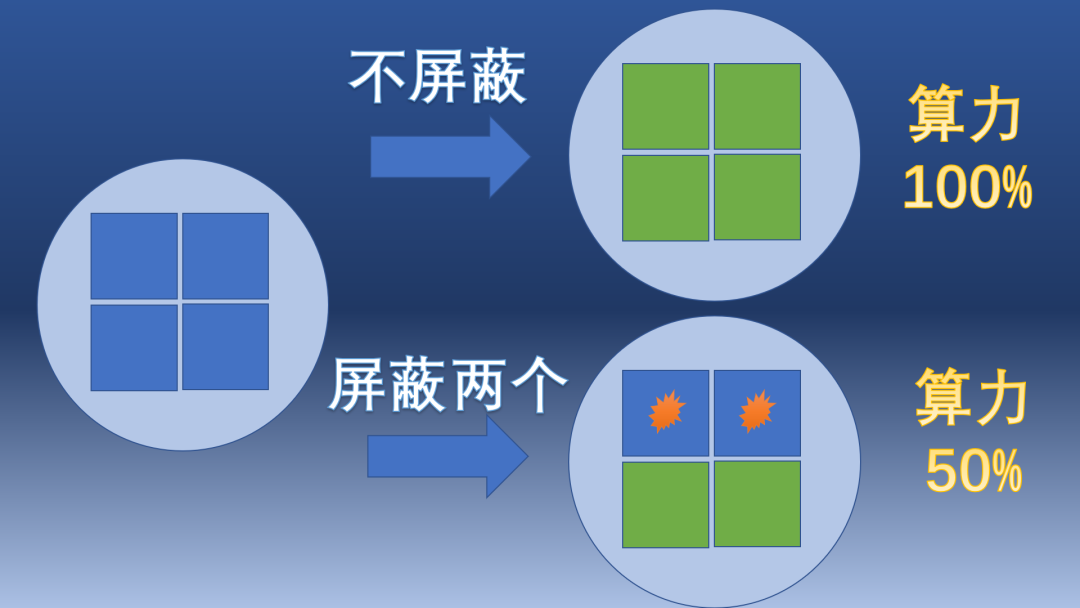

举个例子来说,假设一块小晶圆上面最多可以生产4块Die,如图所示当晶圆上出现一个“坏点”时,最终就只能生产出3块Die,这时良率是75%。而当出现两个“坏点”时,最终就只能生产出2块Die,这时良率是50%。但如果要生产面积比现在大一倍的Die会发生什么呢?

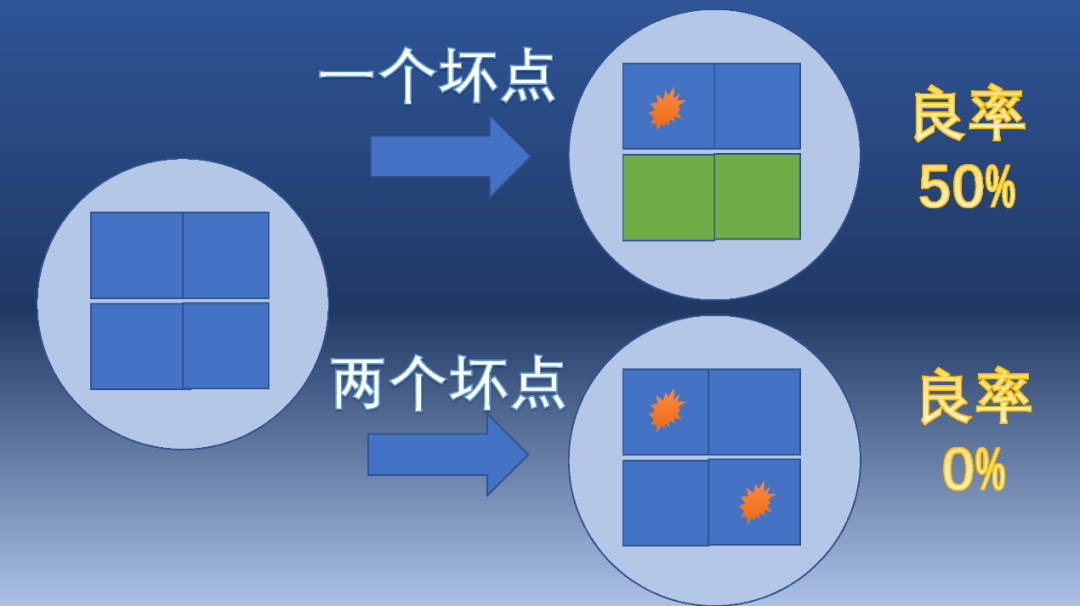

我们姑且将面积大一倍的Die称为大Die。同样尺寸的一个晶圆上最多可以生产2块大Die。如图所示当晶圆上出现一个“坏点”时,最终就只能生产出1块大Die,这时良率是50%。而当出现两个“坏点”时,最终就只能生产出0块大Die,这时良率是0%。 因此可以这样说,同等条件下,Die的面积越小,良率就会越高。Chiplet允许我们通过生产多个小面积的Die最终封装成一个大芯片。但是需要特别说明的是,这个结论必须在“同等条件”下才有效,现实情况下,其它条件往往是不同的,工艺、布局布线、温度等因素对于良率的影响往往才是大头。 产品复用:很多芯片其实需要比较频繁地迭代,比如像手机芯片可能两三年就会出一个新的。但是新一代的芯片内部并不是每一个地方都是新的,有一部分会沿用旧的设计。而在Chiplet威廉希尔官方网站 的影响下,我们可以模块化地设计/制造芯片,那么可以复用的部分可以单独做出一个模块最终封装到新款芯片中,这样就可以大大节约相关的制造成本。 “性能变强”:“性能变强”这个优势实际上是内行和外行之间打口水仗最多的地方,因为双方对于“性能”的定义往往是不一样。从本质上说,Chiplet威廉希尔官方网站 的实际作用是突破芯片Die面积的上限。 比如说,原来是1块面积为5的Die,如果使用Chiplet威廉希尔官方网站 ,那就可以做成5块面积为1的Die,然后封装到一起就可以了。但如果顺着这个思路想,我既然可以做面积为5的Die,那我能不能把5块面积为5的Die封装到一起呢?这样我最终的芯片面积就是25了。我们能制造的单颗Die最大面积是有限制的。比如现在商用的最大晶圆尺寸一般是12英寸,那么即使说破天,你最大也就造一块12英寸的Die。当然由于良品率、成本、散热等因素的限制,实际造不了这么大。但在多方因素的影响下总归是有一个最大尺寸限制的,而Chiplet可以通过多颗Die封装在一起“一定程度”上绕开这个限制。而在使用同种制造工艺的条件下,面积越大,就可以放下更多数量的晶体管,芯片的功能就越多。 那么晶体管数量越多,性能就越强吗?这里开始其实就是一个分歧点了,一些人认为性能就是芯片的“总体算力”,而另一些人则认为性能是,在其它条件大致相同的时候表现出的性能,这个性能的定义更接近于我们日常生活中的“效率”。

比如我们手头有两颗同样的4核CPU,每个核心都采用同样的设计,而且没有“大小核”的区别。现在我们通过软件屏蔽其中一颗CPU中的两颗核心,另一颗则不作处理。这时候不作处理的CPU的算力(或者说跑分)显然是另一个的两倍。但效率上,因为每颗核心采用了同样的设计,所以两者效率其实是一样的。 这其实引出了一个实际问题,如果我要跑算力(或者跑分),相关软件多核心性能能吃满的情况下,算力就是实际性能。但如果软件只支持双核CPU,那么屏蔽与不屏蔽,性能表现其实是一样的。所以说,Chiplet在服务器那边的应用可以切实提高芯片算力,但在消费级这边,意义就没有那么大了。

05 Chiplet真有那么美好吗?

首先需要郑重说明一点是,前文中提到的“Chiplet可以自由组合不同厂商的Die”属于“前瞻性陈述”。或者换句话说,自由组合这个事至少在最近几年没有那么“自由”。本质上的原因在于,目前不同Die之间的连接接口还属于百家争鸣的阶段,这种高度不统一让他们彼此之间难以兼容。 相信有不少年纪不小的小伙伴应该见过这种一拖十的充电线,由于当时手机等数码产品没有统一的充电标准,所以基本上就是一家一个标准,一家一个接头。直到后来才逐渐统一成:Type-c、Micro USB和Lightning接口。 现在的Chiplet也面临类似的问题,各家芯片的接口抛开物理尺寸不说,在功耗、延迟、带宽等方面差异极大。至少在现阶段实现自由互联是十分困难的。 为了让大家团结起来,搞一个统一的标准,UCIe联盟出现了。 但是UCIe联盟的出现似乎并没有促成业界达成真的一致。

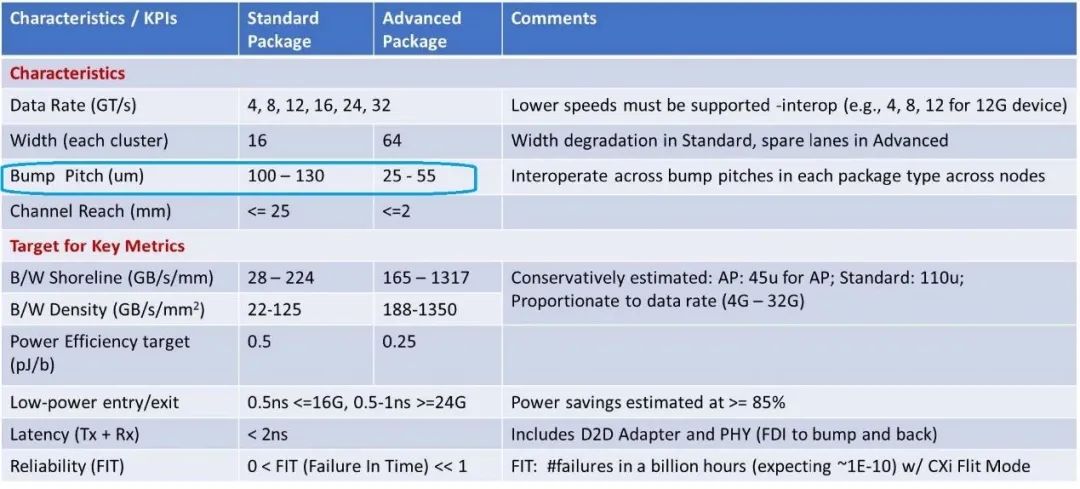

在UCIe发布的白皮书中,我们可以看到Bump间距(pitch)这一栏被分成了两个部分,Standard Package (2D) 主要用于低成本、长距离(小于等于25mm)的互连,其Bump间距要求为100um-130um。Advanced Package (2.5D) 主要用于高性能、短距离(小于等于2mm)互连,其Bump间距要求为25um-55um。 好消息是,UCIe支持较宽范围的bump pitch。坏消息是,这个“较宽范围”有点太宽了。以Advanced Package的bump pitch要求(25um-55um)为例,在这个标准下,未来可能至少衍生出4种符合这个标准的接口。也就是说在UCIe成立之前,大家的标准百花齐放。UCIe成立之后,大家在UCIe的框架下百花齐放。虽然说在一定程度上收紧了标准,但离“真正能自由组合”的统一标准还有距离。不过话说回来,现在各家芯片接口的发展方向本质上不一样的,想让他们统一,很难的啦。但是如果只是围绕几个大厂实现小范围统一希望还是非常大的,比如以英特尔的CPU为核心,其它厂家开发兼容英特尔CPU接口的芯片,并将其封装到一起。

06 UCIe联盟服务于“定制芯片”

而从商业角度看,UCIe联盟本质上是要做“定制芯片”的生意。就比如一家没有芯片方面威廉希尔官方网站 积累的公司,可以作为甲方向芯片公司下达需求,芯片公司完成相应需求,并将芯片产品交付给甲方。UCIe联盟实际上相当于允许甲方可以同时向多家芯片公司进行一个委托,比如去A公司定制芯片a(或者直接选用已有型号的芯片Die),再去B公司定制芯片b,然后a+b封装在一起。这样一来定制的自由度其实是提高了,而且如果是选用已有型号的芯片Die,成本也会更低。 在这种商业模式下,甲方公司其实可以自己做一点芯片的东西并加入到最终产品中。这也就是借助Chiplet可以由浅入深地提高芯片内部使用的“自研”比例。 而且近些年很多国际大厂是比较看好这类合作的。以英特尔为例,英特尔这些年在一些项目上的策略实际上是“不争名只逐利”。从津逮CPU的案例上看,英特尔是很乐于让其它厂商使用他们的内核,并且使用英特尔晶圆厂的工艺制造这些芯片。而且英特尔并不介意最终的芯片产品上打上其它厂商的logo。并且英特尔还会发文章称这种合作是“win-win”(双赢),毕竟对于英特尔来说他们该挣的钱并没有少挣。而对于芯片发布厂商来说,他们确实发布了一款性能和英特尔“完全一样”的芯片产品。不过这个与其说是“弯道超车”,不如说是“站在巨人的肩膀上”。 从目前已有的案例看,想要使用英特尔的CPU内核就必须使用英特尔的工艺,甚至最终还要配套使用英特尔的封装威廉希尔官方网站 。所以这对于英特尔等国际大厂来说是一种扩大销路的方式。

07 结语

1、Chiplet可以在有限范围内实现芯片的自由组合。我们可以借助Chiplet循序渐进发展***。 2、这种“中美合拍”的芯片最终算不算“***”可能会取决于国产化的比例。不过只要芯片公司在宣发的时候说清楚,哪些部分是自己做的?哪些部分是别人做的?那就是好公司。毕竟芯片威廉希尔官方网站 是要靠脚踏实地一点点积累,要求一口吃个胖子也不现实。肯定有些公司在宣传的时候不想说清楚这些问题,直接用“联合研发”或者“自研”的名号糊弄过去。 3、与消费端芯片相比,Chiplet在服务器端的优势更大。 4、Chiplet的很多优势其实来自于“先进封装”,但具体有哪些优势取决于使用何种“先进封装”,所以这方面内容在本文中没有过多展开讨论。 5、关于UCIe的相关标准,由于篇幅较长,感兴趣的读者可以参考UCIe Specification Revision 1.0。

编辑:黄飞

电子发烧友App

电子发烧友App

评论