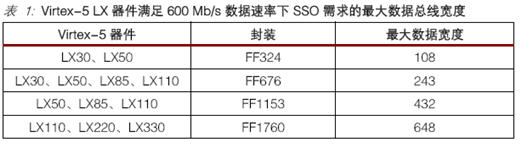

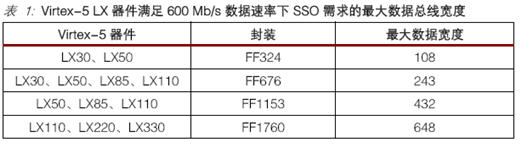

本白皮书讨论各种存储器接口控制器设计所面临的挑战和 Xilinx 的解决方案,同时也说明如何使用 Xilinx软件工具和经过硬件验证的参考设计来为您自己的应用(从低成本的 DDR SD

2010-08-18 10:50:37 3238

3238

:视频处理器框图FPGA获取并缓存四个视频源的数据流。这些FIFO缓冲器由DDR3存储器控制器清空并保存在DDR3存储器中。一旦一个完整的视频数据包存储完毕,视频处理器会向DDR3存储器控制器申请数据

2019-05-24 05:00:34

Everspin Technologies总部位于亚利桑那州钱德勒,主要是设计和制造MRAM、STT-MRAM的全球领导者,Everspin所生产的MRAM产品包括40nm,28nm及更高工艺在内

2020-08-31 13:59:46

请教大家,我打算使用这个方案,FPGA使用控制器硬核,外面挂两个16位DDR,这两个DDR的的差分时钟、地址线、控制线等共用,只有数据线使用各自的。希望做到两片同时访问,一次把32位数据分成两个16

2016-04-26 13:41:00

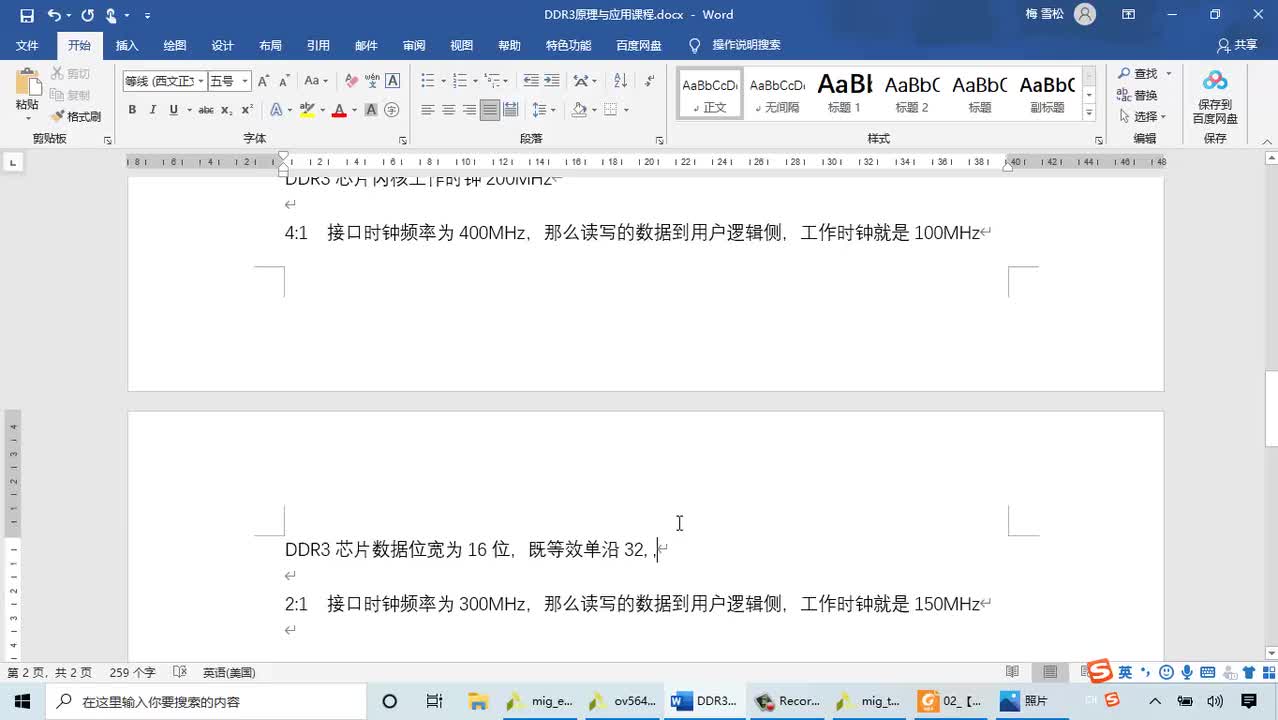

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

XILINX 关于FPGA 对DDR SDRAM 的设计文档

2012-08-17 09:20:26

Pinout文件,我们可以灵活选择。图2、FPGA Pinout下载链接图3、Xilinx官网下载Pinout我们打开一个.TXT形式的Pinout,如图4所示。可以看到,文件分为8列,包含所有设计原理图

2021-05-28 09:23:25

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

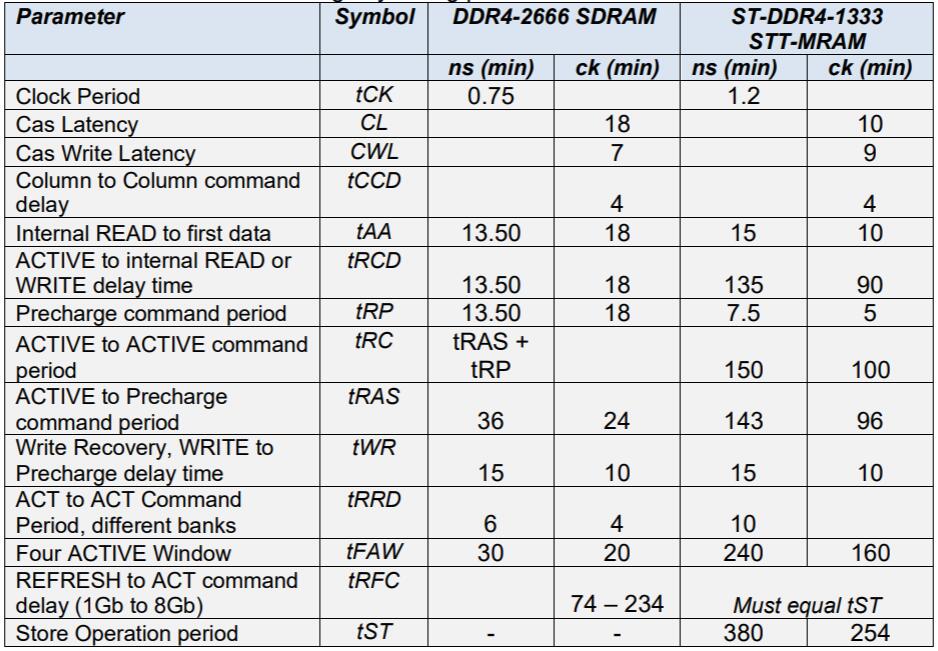

的JEDEC标准DDR4接口的变体,它包含了对完整系统支持所需的独特功能。本文将帮助工程师了解Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2021-01-15 06:08:20

破解Lesson05 特权Xilinx FPGA SF-SP6入门指南 -- 文本编辑器notepad++安装Lesson06 特权Xilinx FPGA SF-SP6入门指南 -- ISE中使

2015-07-22 11:49:20

你好任何人都可以指导我,Xilinx ISE中的DDR控制器是否有任何IP实现。如果没有如何实现DDR控制器以上来自于谷歌翻译以下为原文Hi can any one guide me

2019-02-27 12:13:51

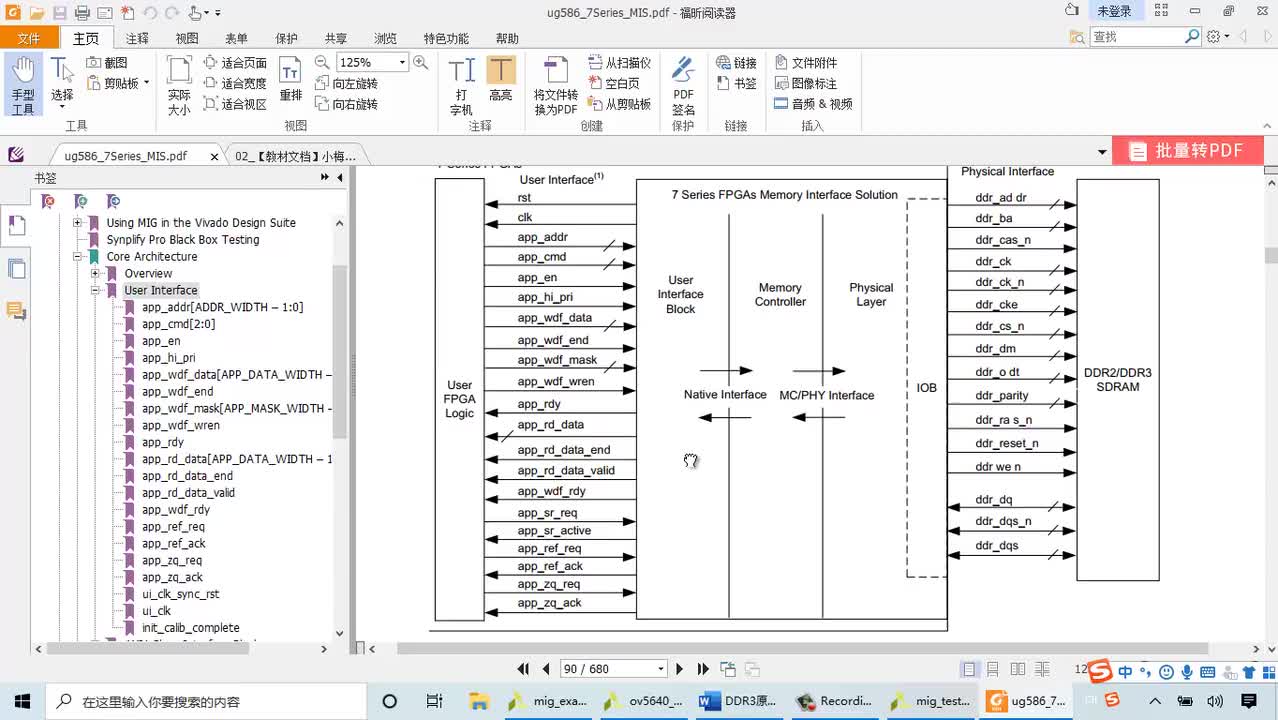

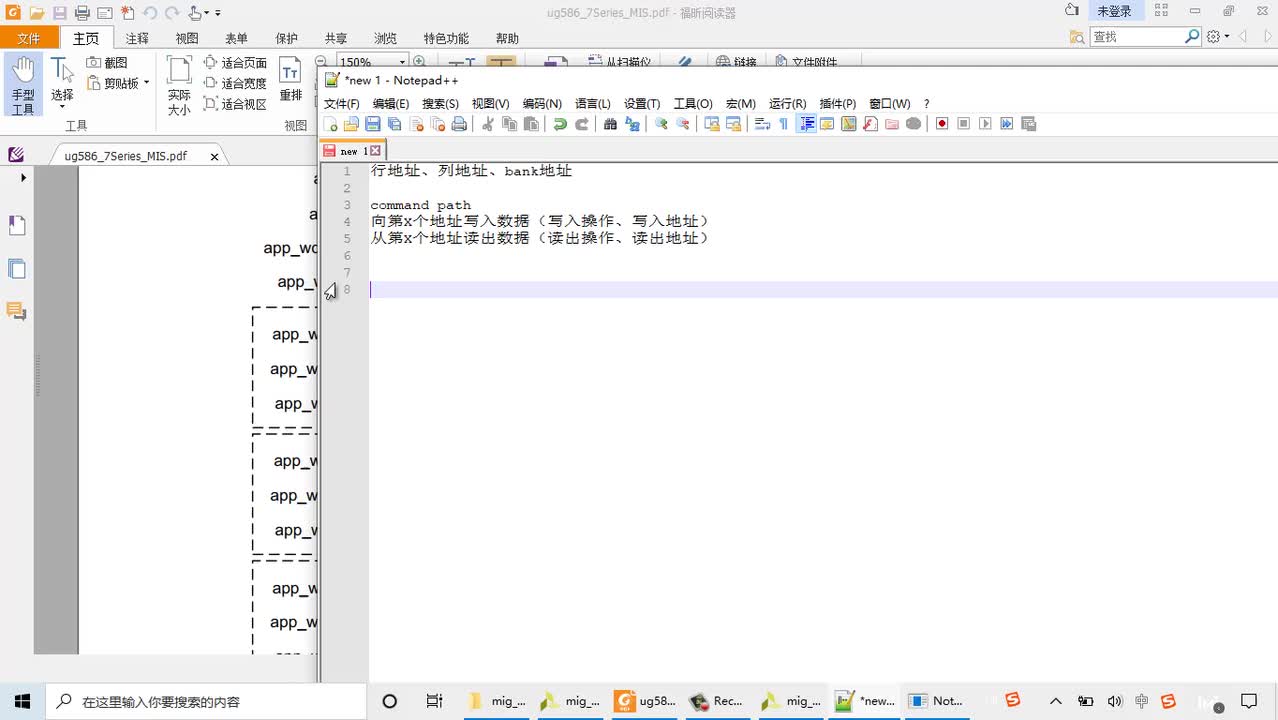

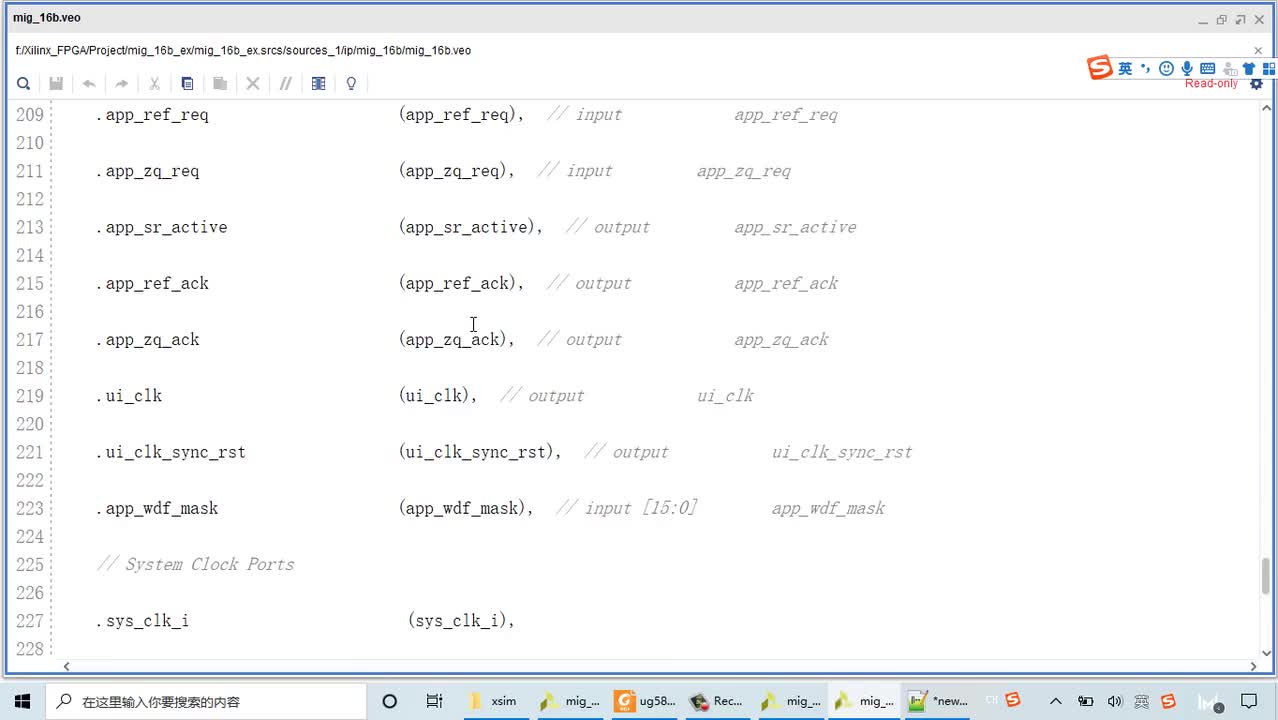

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制和读写时序的情况下,也能通过MIG IP控制器读写DDR存储器。一、新建工程在Vivado环境

2019-12-19 14:36:01

xilinx公司的7系列FPGA应用指南

2012-08-14 12:17:40

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装软件也不行

2018-01-24 08:23:17

。2.5 LBS状态机工作流程FPGA作为LBS的逻辑控制器,负责协调好与DDR_FIFO数据和PEX8311之间的时序关系。系统接收数据时,首先由驱动程序向PEX8311发 送复位信号,通过

2015-01-29 14:09:17

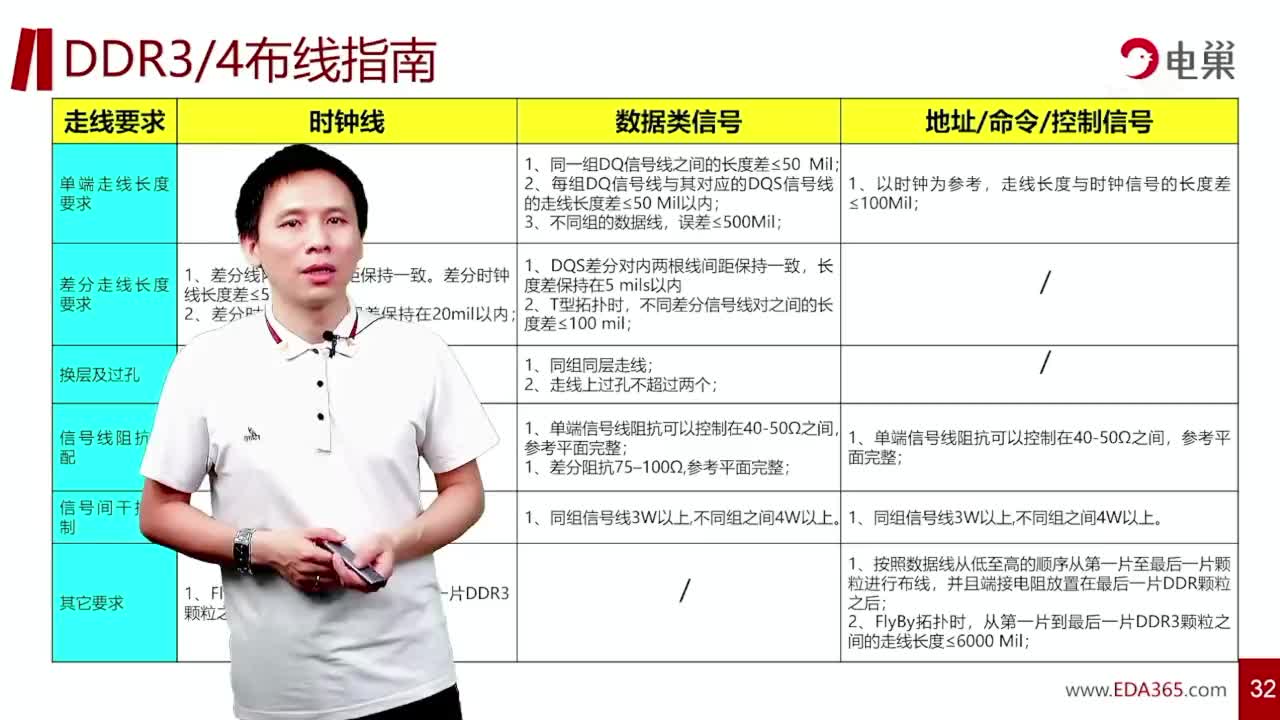

【PCB多层板设计挑战赛】+FPGA控制器应用领域:基于FPGA的低速辅助驾驶控制器挑战点:为了保证FPGA的高速接口(DDR4/MIPI/DP/USB)的SI并降低EMC,采用多层GND进行信号

2022-11-09 17:35:05

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。Altera DDR2控制器使用IP的方式实现,一般很少自己写控制器代码。ddr

2020-02-25 18:33:00

`例说FPGA连载36:DDR控制器集成与读写测试之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例对Altera提供

2016-10-08 17:05:55

`例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 如图

2016-10-27 16:36:58

SATA主机控制器SATA Host控制器SATA Host Controller基于FPGA的SATA主机控制器基于FPGA的SATA Host控制器本人在北京工作7年以上,非常

2015-11-11 15:06:39

我可以使用mig生成ddr控制器(xc6vlx130t)吗?mig向导只支持ddr2和ddr3!

2020-06-12 07:32:48

如图7所示。图7 DDR3读写状态机为确保设计的可行性及可靠性,对编写的DDR3读写控制器进行板级验证,硬件测试中选用Xilinx公司的Kintex-7 FPGA以及Micron公司的DDR

2018-08-02 09:34:58

基于Xilinx FPGA的DDR2 SDRAM存储器接口

2012-08-20 18:55:15

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

你好使用Xilinx的任何一个端口MIG DDR2 SDRAM控制器都是我遇到了问题我有vhdl顶级系统,其中我实例化ddr2控制器我的ddr2包装器与testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

嗨,我们从xilnx购买了ML555板。我们想验证该板上的ddr2控制器。我们已经加载了CD中提供的ddr2控制器的位图文件。我们没有观察到为阅读文件中提到的比较逻辑有效的数据提供的任何LED切换。如用户指南中所述,正确生成时钟。让我们知道这种行为的原因。问候--sampath

2019-08-19 09:35:52

你好如何在不使用DDR内存控制器的情况下设计FPGA BRAM(或任何其他内存模块_SD,DDR以外的本地等)大容量存储单元?当我通过示例设计“VC707_bist”替换DRAM控制器和BRAM

2019-04-04 15:10:55

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

Xilinx DDR 控制器。 DDR PHY 与电路板调试: Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。 这意味着您可以使用标准 MIG 示例设计来验证您

2021-01-07 16:02:09

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

大家好,我想设计自己的DDR控制器并在FPGA上验证它。我将在verilog中实现我刚开始阅读JESDC79C DDR规格..但我很困惑如何编写那些初始化序列?请建议如何处理这个设计DDR控制器

2019-04-29 11:59:22

嗨,我即将使用Virtex-4QV设备(XQR4VFX140)开始一个新项目。虽然我对使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些经验,但我发现MIG IP不支持VIRTEX-4QV器件。那可能是另类?如何将DDR2 SDRAM与此FPGA连接?弥敦道

2020-04-02 06:08:46

目前有一个项目需要使用DDR3作为显示缓存,VGA作为显示器,FPGA作为主控器,来刷图片到VGA上。VGA部分已经完成,唯独这个DDR3以前没有使用过,时序又比较复杂,所以短时间内难以完成,希望做过DDR3控制器的大神指点一二。急求!!!!

2015-11-16 09:18:59

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA与DDR2存储器接口DDR2控制器的设计原理是什么?DDR2控制器的应用有哪些?

2021-04-30 06:28:13

的内存控制器的设计与应用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存储器接口设计.pdf一种采用FPGA设计的SDRAM控制器.pdf用Xilinx+FPGA实现DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

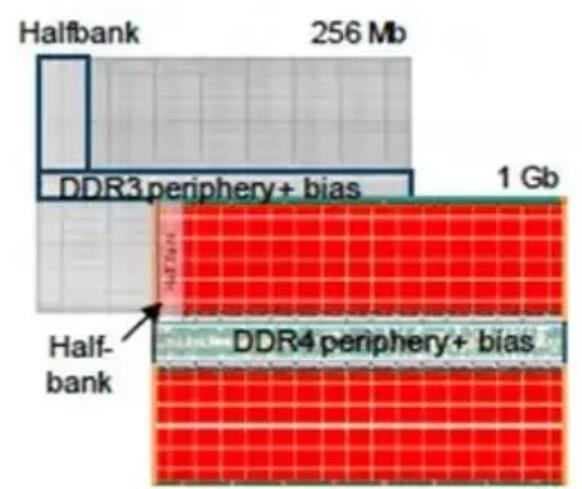

适用于Xilinx Virtex-7 FPGA开发板的32位DDR4 SDRAM

2020-12-30 07:39:14

你好我在Xilinx Spartan3E启动板上为旧的基于Z80的计算机开始了我自己的项目。但我已经冻结了DDR内存控制器。我可以使用任何DDR参考设计吗?我需要8位数据路径,就绪/忙碌信号表示

2019-05-15 07:15:33

Virtex-4 FPGA应用指南

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指标所要求的更好的新功能,并允许DDR2器件以666Mb/s的数据

2010-05-13 14:14:26 39

39 用中档FPGA实现高速DDR3存储器控制器

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储威廉希尔官方网站

进行了优化。下一代双数据速率(D

2010-01-27 11:25:19 879

879

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存储控制器的用户接口设计与仿真,本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速

2013-01-10 14:12:45 2990

2990 用FPGA设计DDR2控制器讲解DDR2时序原理用户接口设计帮助用户快速掌握DDR2的控制威廉希尔官方网站

新手上路的非常有帮助的资料。

2015-11-10 10:54:14 3

3 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 38

38 Xilinx FPGA工程例子源码:FPGA实现CAN总线控制器源码

2016-06-07 14:13:43 87

87 Xilinx FPGA工程例子源码:USB接口控制器参考设计VHDL代码(Xilinx)

2016-06-07 14:54:57 21

21 Xilinx-ISE9.x-FPGA-CPLD设计指南合集

2022-03-22 18:03:09 76

76 Xilinx FPGA工程例子源码:Xilinx DDR3最新VHDL代码(通过调试)

2016-06-07 14:54:57 77

77 Xilinx FPGA工程例子源码:Xilinx DDR2存储器接口调试代码

2016-06-07 14:54:57 27

27 Xilinx FPGA工程例子源码:Xilinx 的用于设计SMBus控制器的源程序

2016-06-07 15:07:45 14

14 Xilinx FPGA工程例子源码:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 基于协议控制器的DDR3访存控制器的设计及优化_陈胜刚

2017-01-07 19:00:39 15

15 DDR2SDRAM控制器IP功能测试与FPGA验证_陈平

2017-01-07 21:45:57 3

3 和 Xilinx Ehab Mohsen 聊到了将 DDR4 与 Xilinx UltraScale™ FPGA 相结合可实现的惊人性能优势和功能。 立即观看在线座谈 »

2017-02-09 06:18:33 470

470 控制器用户接口设计方案。该控制器用户接口已经在Xilinx 公司的VC707 开发板上通过了功能验证,并成功的被应用到高速图像数据采集系统中。

2017-11-17 14:14:02 3290

3290

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作

2017-11-22 07:20:50 4687

4687

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,运行速度高于1866 Mbps数据速率。

2018-11-30 06:21:00 5276

5276

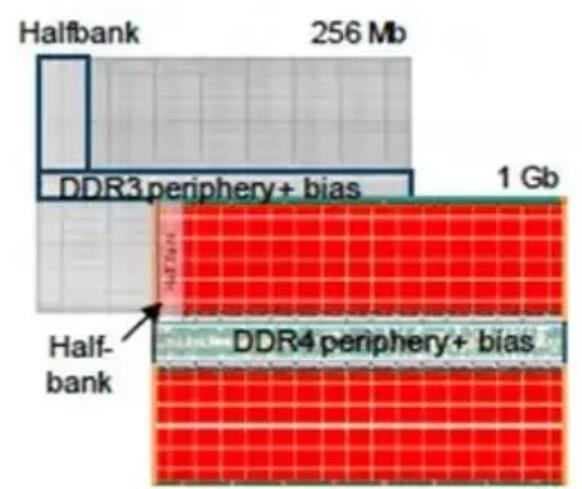

Everspin 近日宣布,其已开始试生产最新的 1Gb STT-MRAM(自旋转移力矩磁阻)非易失性随机存取器。

2019-06-27 08:59:43 9837

9837 GlobalFoundries、Everspin联合宣布,双方已经达成新的合作,将利用GF 12LP(12nm FinFET)工艺来制造新一代STT-MRAM(自旋转移矩磁阻内存),包括独立的MRAM芯片和嵌入式的eMRAM。

2020-03-16 08:42:26 497

497 MRAM和STT MRAM。STT MRAM需要控制器启用或FPGA,该公司也一直在通过其伙伴关系发展其生态系统。 Everspin的几个合作

2020-03-23 15:32:08 646

646 )STT-MRAM位单元的开发方面处于市场领先地位。 Toggle MRAM为许多行业提供服务,包括交通运输,航空航天和医疗,物联网及工业。Everspin与全球能源管理和自动化专家Schneider

2020-04-09 09:28:05 680

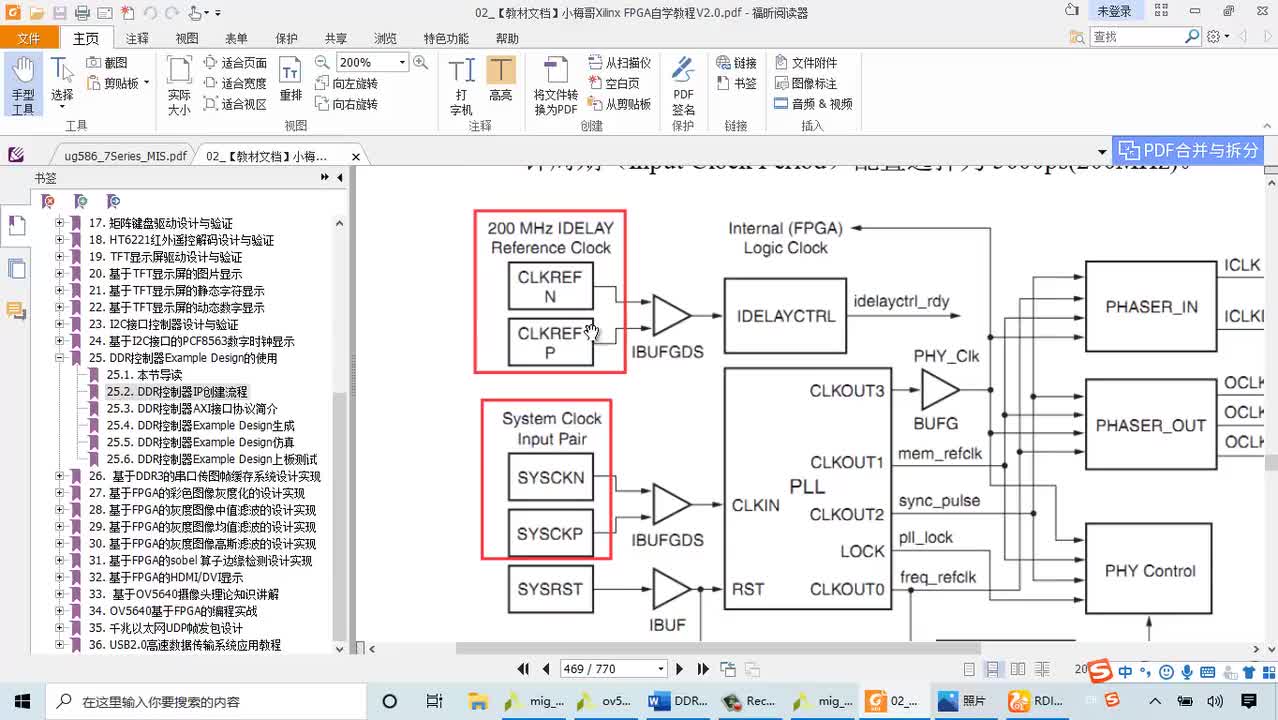

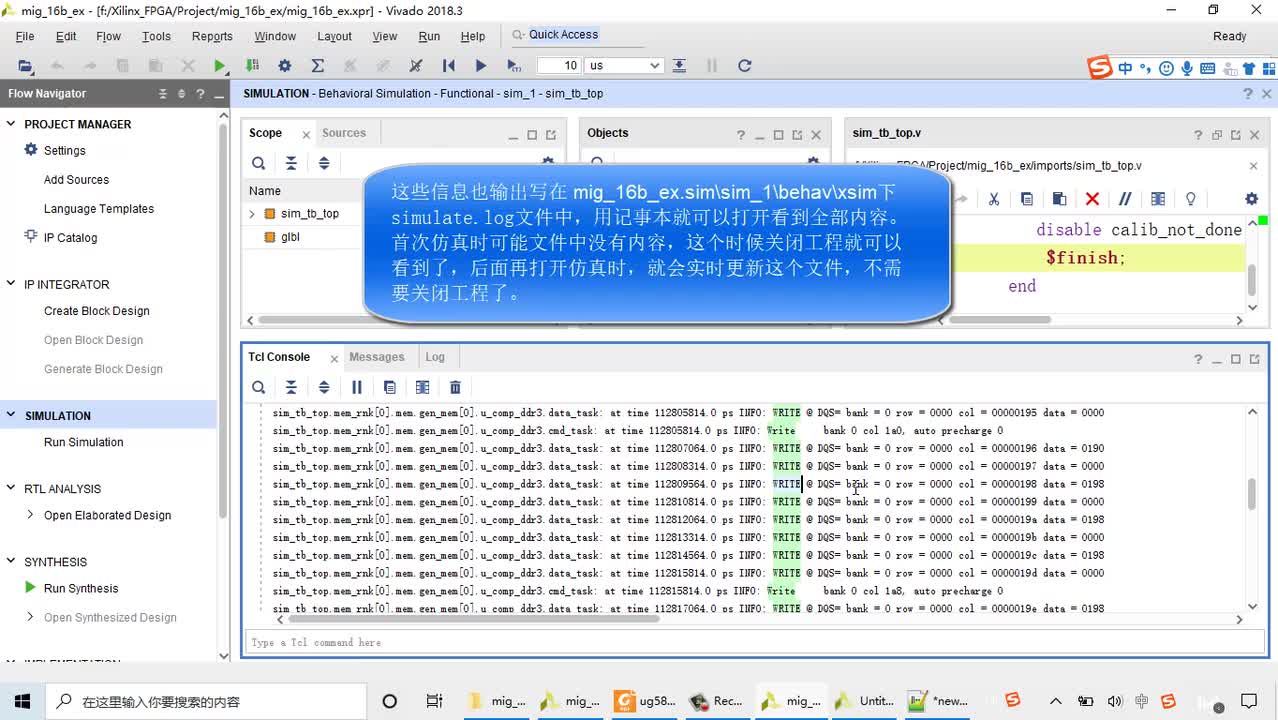

680 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

DDR PHY 与电路板调试:

Zynq UltraScale...

2021-02-23 06:00:10 15

15 本应用指南描述了在 Virtex™-4 XC4VLX25 FF668 -10C 器件中实现的 DDR SDRAM 控制器。该实现运用了直接时钟控制威廉希尔官方网站

来实现数据采集,并采用自动校准电路来调整数据线上的延迟。

2021-03-26 14:42:41 4

4 Xilinx FPGA的监控器件补充部件指南

2021-04-27 19:28:56 5

5 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 ,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据 Xilinx 官方提供的威廉希尔官方网站

参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 Everspin Technologies,Inc是设计制造MRAM和STT-MRAM的全球领导者其市场和应用领域涉及数据持久性和完整性,低延迟和安全性至关重要。E...

2022-01-25 19:29:14 3

3 Everspin是设计制造MRAM、STT-MRAM的翘楚,其市场和应用涉及数据持久性和完整性,低延迟和安全性至关重要。在磁存储器设计,制造和交付...

2022-01-26 18:14:01 9

9 干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

2022-02-21 18:15:32 6873

6873

everspin在磁存储器设计,制造和交付给相关应用方面的知识和经验在半导体行业中是独一无二的。Everspin拥有超过600项有效专利和申请的知识产权组合,在平面内和垂直磁隧道结(MTJ)STT-MRAM位单元的开发方面处于市场领先地位。

2022-11-17 14:23:28 2461

2461

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 743

743

电子发烧友网站提供《面向Xilinx FPGA和SoC的超快设计方法指南.pdf》资料免费下载

2023-09-14 10:02:31 1

1 电子发烧友网站提供《Xilinx FPGA和SoC的超高速设计方法指南.pdf》资料免费下载

2023-09-14 09:41:06 0

0 16层官方Xilinx Kintex UltraScale FPGA KCU105 4片DDR4分享下载

2021-10-11 14:24:57 63

63

电子发烧友App

电子发烧友App

评论