在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

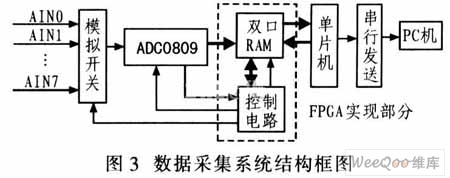

FPGA 使用新手 调用双口ram 中的数据。操作遇到问题。 DSP跟FPGA数据交互正常,但是在FPGA内,编写verilog按照dsp 的时序去读取字节数据存在问题,读出来的数据都为0x00;有哪位大虾能提示下,这个使用过程中需要注意的关键。

2016-02-17 17:03:16

利用FPGA设计双口ram,最大设计多的空间的?如果是cpld来实现,空间是不是更小?如何去确定这个大小呢?求指导

2013-10-21 21:23:21

各位大神,我最近在做FPGA项目遇到一个问题,我想实现这样的功能:向RAM里写一次数据,再多次读出来,可是我发现IP核里的RAM读第二次的时候RAM数据就清零了,根本读不我写的数据,请问有什么好的解决办法吗?谢谢啦!

2015-06-07 20:31:57

[attach]***[/attach](给出双口RAM的结构.介绍双口RAM的忙逻辑,并主要介绍了在雷达终端的数据处理过程中两个 CPU通过双El RAM进行数据的储存、交换和共享的设计原理和方法。

2012-08-11 16:21:22

利用FPGA自带的IP核实现双口RAM用于2片MCU进行数据交换时多次读数据后RAM中数据变为了0,是什么意思,打什么帮帮忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 编辑

双口RAM怎么实现左右两侧同时写入这是怎么实现

2012-08-15 18:18:34

用双口RAM实现和DSP的通信,用chipscope将要看的输出信号加进去的时候发现信号线呈现红色,BASE TYPE是IOBUF类型,这个应该是错的,加信号进去会警告提示布局布线可能会出错,事实的确如此,有人知道是什么原因吗?

2016-04-20 20:06:44

,写信号wr,我使用FPGA实现双口ram,双口ram一端连接主板的双口ram信号,另外一端连接我的nios II处理器由于控制采集处理等,现在问题存在地址冲突,比如我将数据存在0x00

2018-01-18 13:51:58

系统结构与功能: lpc3131外接8k*8双口ram与8G Flash,从双口ram读取数据(来自FPGA),并存至Flash中。问题: 丢数据,系统速度远低于ram的读速与Flash的写速度。双

2011-08-04 11:05:31

告诉我,对于所有斯巴达3代设备,RAM是18Kbit块,这意味着该块的最大双端口实现是512深36宽。我知道要弄清楚我需要什么,我必须写两个块然后并行运行它们然而我不知道该怎么做。谁能帮帮我吗。是不是

2019-02-13 08:12:00

本帖最后由 咖小啡 于 2011-3-23 11:41 编辑

请高手指教DSP-TMS320F2812与双口RAM-IDT7130的通信程序,

2011-03-23 11:41:04

ERAM用作简单双口RAM时,哪个信号可以作为wren使用?

2023-08-11 09:50:55

和后仿真。以上介绍了一种应用于通用微处理器系统中的SDRAM与双口RAM之间的数据转移接口控制电路,由VHDL语言设计,用Xilinx公司4000系列FPGA实现,目前该电路硬件实现和微处理器系统已经通过验证,证明可将SDRAM作为高速、大容量存储器应用在简单电子系统中。

2019-06-10 05:00:08

SDRAM与双口RAM的区别?它们两者一样吗?不一样的话能互相代替使用吗?

2012-09-05 16:51:10

过多介绍。下面给出几个各种实现方式的Verilog示例代码。分布式RAM下面给出一个异步读模式的双口分布式RAM的示例:module rams_dist ( input [5:0]a, dpra, output [15:0]spo, dpo if (we) ram[a]

2020-09-29 09:40:40

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

`嵌入式RAM使用之双端口RAM实验目的: 1.学习Altera公司Cyclone IV系列器件的内部结构2.学会调用Quartus II软件中提供双口RAM核并进行仿真实验平台:芯航线FPGA学习

2017-01-02 09:40:23

应用系统实验平台:芯航线FPGA学习套件核心板实验原理:为了实现通过串口发送数据到FPGA中,FPGA接收到数据后将数据存储在双口ram的一段连续空间中,当需要时,按下按键0,则FPGA将RAM中存储

2017-01-04 00:54:36

针对目标板上的双口RAM芯片的右端口进行读写测试,来检测右端口和内部存储地址的正确性。原理图1:RS422接口:MCU:LDO:DB9接口:PCB LAYOUT:PCB 3D view:

2018-08-30 09:48:15

活动第一季——看教程,秀笔记,赢好礼https://bbs.elecfans.com/jishu_520463_1_1.html23【连载视频教程(十三)】嵌入式块RAM应用之双口RAM:https

2015-10-23 12:47:16

什么是双口RAM?基于FPGA的双口RAM有哪些应用?

2021-05-06 07:41:03

设计来增设全新的芯片功能,据此实现了芯片整体构造的简化与性能提升。下面英尚微电子介绍FPGA开发板内部ram是如何操作的。 除逻辑外,所有新的FPGA都有专用的静态ram块,这些块在逻辑元素之间分布并由

2020-09-10 11:11:57

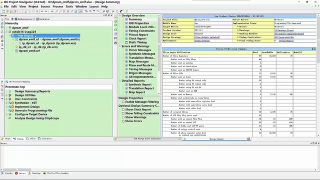

`例说FPGA连载84:工业现场实时监控界面设计之双口RAM特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc ① 在新建的工程中,点击菜单

2017-03-26 21:18:53

我现在需要设计一个双口的ram,它要求数据和地址线是复用的,双向的,想利用FPGA设计,请教下大家思路,谢谢。

2012-07-13 08:52:18

在设置双口RAM的时候,我想在数据同时读写时,先读这个地址上一次的数据再写入新的数据,就和ise中的read first类似。但是我设置的仿真结果总是先把数据写进去再读取,等于输入什么输出什么,有什么办法么?

2020-03-16 10:25:01

哪位大神有verilog实现的双口RAM例程,就教!

2015-07-29 20:44:56

毕业设计在做基于FPGA的多通道数据采集系统,现在基本的硬件原理图已经完成就还有一个USB控制芯片(CY7C68013,56引脚)与双口RAM(CY7C09279V-12AC)之间的接口和通信

2014-04-16 21:14:56

的应用。采用FPGA威廉希尔官方网站

构造双口RAM,实现高速信号采集系统中的海量数据存储和时钟匹配。功能仿真验证该设计的正确性,该设计能减小电路设计的复杂性,增强设计的灵活性和资源的可配置性能,降低设计成本,缩短

2010-04-24 09:44:28

的下一个周期将读控制信号置为无效,状态机恢复为读空闲状态。3 FPGA仿真实现在Modelsim开发平台下,实现了PCI9052读写双口RAM的仿真过程,该仿真波形如图4所示。从仿真波形可以看出该代码可以

2018-12-12 10:27:45

介绍一种基于双口RAM的L0NW0rkS现场总线智能通信节点的设计方法,并给出详细的设计步骤、硬件及软件实现。通过此LonWorkS智能通信节点,能够完成RS-232-C/RS-485标准

2011-03-08 17:25:48

,利用基于双端口RAM 中一种巧妙的地址映射机制实现同时对多行代码设置断点的功能,并且能够方便地实现被调试系统和调试主机之间调试信息和命令的交互。UDM 还具有易于扩展的优点,当SOPC 系统中有多个

2020-08-15 09:59:40

最近再做一个双CPU板子,需要搭建一个双DSP系统,它们之间的数据传输通过双口RAM通讯,求各位大神指导

2016-05-04 13:00:06

求教大牛关于CPLD的双口RAM设计程序!

2012-10-22 16:18:14

大神们。我是新手!求解决 在做FPGA 配置双口RAM和rom如何消除读取延迟

2015-11-17 19:42:18

如何利用FPGA实现UART的设计?UART的结构和帧格式

2021-04-08 06:32:05

本文介绍了一种利用双口RAM实现DSP与单片机高速数据通信的方法,给出了它们之间的接口电路以及软件实现方案。

2021-06-03 06:18:37

如何利用双端口RAM去实现PCI总线接口?

2021-05-06 06:30:53

本文结合组合导航系统设计,介绍了利用又口RAM实现导航计算机主从机之间通信的一种实用、高效的系统设计方法。

2021-05-28 06:58:45

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

PCI9052是什么?什么是双DRAM?怎样去设计PCI和双口RAM之间的接口?

2021-05-07 06:03:59

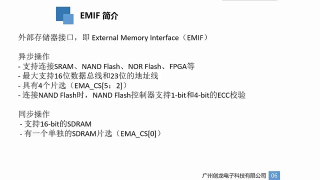

请教各位大神!是否可以通过FPGA内核配置的双口RAM,实现FPGA与DSP之间的数据交换?可以的话怎么实现?怎么设置FPGA的内核RAM?如何连接DSP的外部存储器XINTF的引脚和FPGA的引脚?谢谢!

2017-12-07 15:44:03

威廉希尔官方网站

要求;通过双口RAM接收捷联惯性导航系统IMU及系统实时解算等数据并以bin格式文件形式将其存储在SD卡中,以时间为文件名保存,SD卡不小于16GB,数据存储速率不小于50000字节/秒(数据频率500HZ,每帧100字节)有大神愿意做的联系,名字q

2018-05-07 13:45:20

我想选一片双口RAM,是32KX8,5V供电的,我首先选择了IDT7007但是发现没有工业级的,军用级价格很贵但是采购有很麻烦,请求大家推荐一块双口RAM!谢谢大家!!!

2011-09-20 10:30:19

小弟最近在设计一款双核采集系统使用ep1c6q240c8和tms320vc5509a双核,两块芯片使用外部双口RAM进行数据传输,请教各位大神ep1c6q240c8怎么和双口RAM连接啊???????????????????????

2012-11-05 10:42:41

从双口ram里读数据的时候一直有两个时钟的延时??[attach]***[/attach]

2017-05-13 09:38:29

我想用fpga实现一个双口的ram,有8位的数据和地址线,他们是共享的,分时复用,请问怎么解决这个问题,另外读写冲突的问题怎么解决应该,哪位高手指点一下,谢谢啦。

2012-07-10 11:21:39

使用FPGA自行设计桥接电路,本设计结合系统需要,采用双口RAM实现数据交换,FPGA实现接口逻辑转换。接口设计方案如图1所示。图1中DSP为Analog Devices公司TS101,4片TS101

2019-04-22 07:00:07

你好,我想知道简单的双端口和真正的双端口RAM之间的资源使用差异? True双端口Ram中的额外读写端口是否在不使用fpga结构资源的情况下处理?如果这是真的那么为什么要专门使用简单的双端口配置呢

2019-06-10 07:15:24

在FPGA中怎样去构造存储器?如何利用库函数去构造双端口RAM?库函数法构造双端口RAM的有哪些步骤?其它存储器的构造方法有哪些?双端口RAM在高速数据采集中有什么应用?

2021-04-14 06:57:55

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA威廉希尔官方网站

构造双口RAM,实现高速信号采集系

2010-02-11 11:20:27 69

69 摘要:分析了在空间环境下影响RAM可靠性的主要因素及主要故障模式,介绍了利用FPGA实现RAM检错纠错电路的方法,给出了仿真结果,并将此方法同用中小规模集成电路实现RAMEDAC的方

2010-05-10 09:42:23 15

15 基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM 最大

2010-11-15 17:44:19 82

82 利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采用两套时钟线,地址线和数据线,例化双口RAM的

2011-01-15 15:41:26 29

29 摘要: 在高速并行流水信号处理中,ASIC(FPGA)+DSP+RAM是目前国际流行的一种方式,尤其是FPGA+DSP+RAM更适合中国的国情.本文利用FPGA的算术逻辑单元与外部存储器相结合,解决了线路板面积有限与雷达数据处理需要大量存储空间的矛盾;利用FPGA的并行流水特点解决了

2011-02-27 16:00:26 83

83 FPGA内部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日学习的时间了,今天我们来聊一聊在FPGA设计中RAM的两种使用方法,RAM是用来在程序运行中存放随机变量的数据空间,使用时可以利用QuartusII的LPM功能实现RAM的定制

2018-06-08 11:30:28 19561

19561 本文介绍了如何在FPGA 中利用Block RAM 的特殊结构实现HDTV视频增强算法中灰度直方图统计。

2019-07-10 08:10:00 2578

2578 些大材小用,因此xilinx公司在其FPGA内部专门集成了很多存储器模块,称作Block RAM,其犹如slice海洋当中的一颗颗明珠,专门实现数据暂存功能,且每个时钟区域都布置了若干个Block

2020-11-23 14:08:43 7378

7378

在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技FPGA做简单总结,说明基本原理。

2020-12-24 14:28:09 916

916 我们知道,RAM是用来在程序运行中存放随机变量的数据空间,使用时可以利用QuartusII的LPM功能实现RAM的定制。

2020-12-30 16:27:53 9

9 FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2022-02-08 15:50:49 12183

12183

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM? FPGA在一个时钟周期可以读取多个RAM数据 FPGA中的RAM是FPGA中存储数据的主要形式之一,许多FPGA

2023-10-18 15:28:20 598

598 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 80

80

电子发烧友App

电子发烧友App

评论