实时时钟芯片(RTC)允许一个系统能同步或记录事件,给用户一个易理解的时间参考,这里分享一些实时时钟芯片的设计资料,以及工程师在应用设计时应为了避开设计时出现的问题。

2016-07-25 11:08:49 5224

5224

在进行具体工程的抗干扰设计时,我们可以选择有较高抗干扰能力的产品,采取抑制干扰源、切断或衰减电磁干扰的传播途径和利用软件手段等措施,来提高装置和系统的抗干扰能力。

2018-11-01 08:55:30 6762

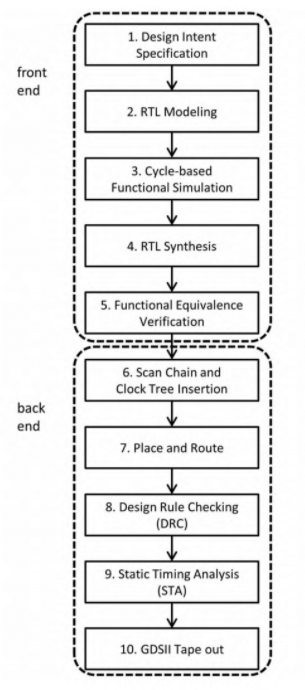

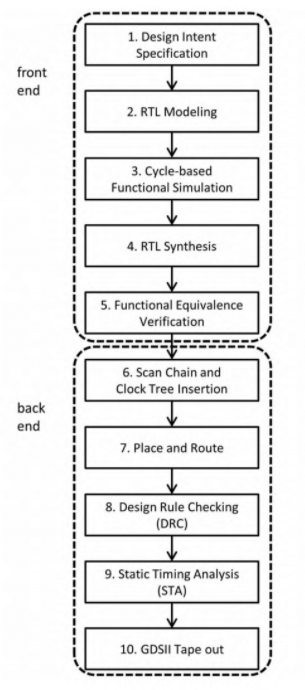

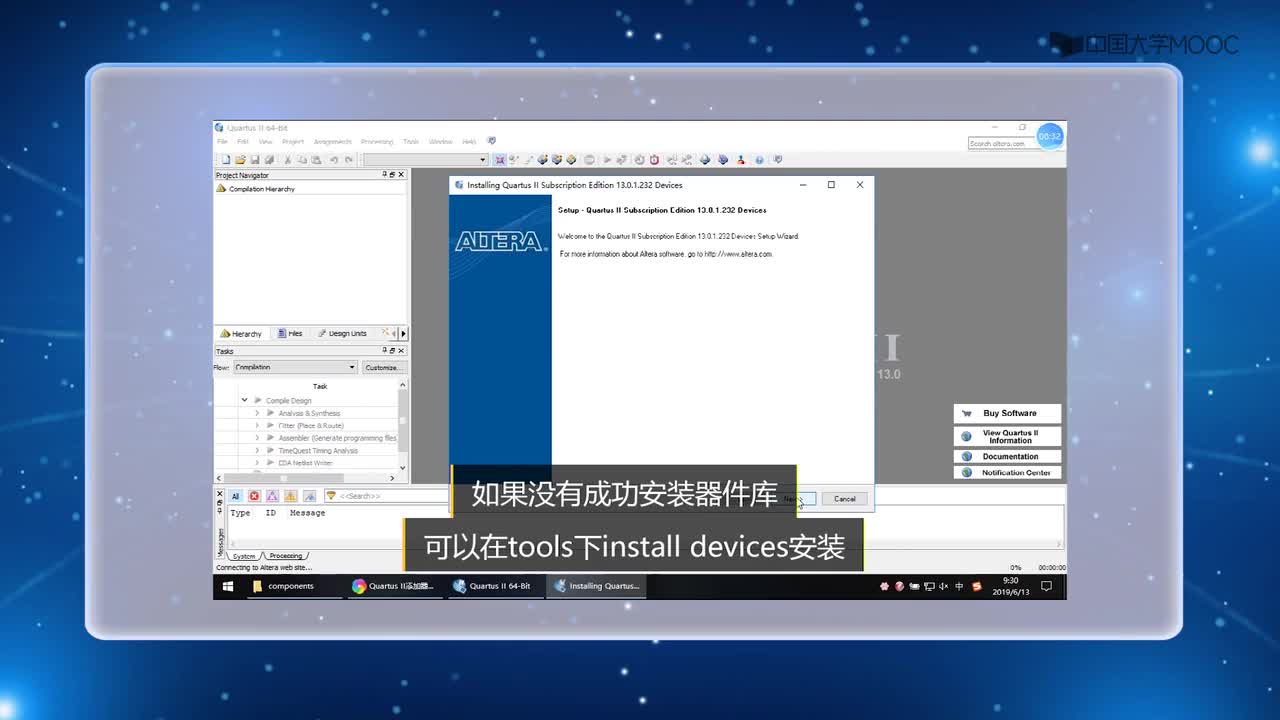

6762 FPGA的前端设计流程类似于ASIC,但后端不同。FPGA的后端部分与ASIC的主要区别在于FPGA的布局和布线。对于ASIC,place and route软件决定IC的制造方式。

2022-06-20 16:24:12 4730

4730

ASIC1810 - ASIC1810 - List of Unclassifed Manufacturers

2022-11-04 17:22:44

1、概念区别: ASIC(专用集成电路)是一种在设计时就考虑了设计用途的IC。 FPGA(现场可编程门阵列)也是一种IC。顾名思义,只要有合适的工具和适当的专业基础,工程师就可以对FPGA

2020-12-01 17:41:49

...................................493.2 设计工具 ISE 与 Vivado......................................493.3 ASIC 设计转换

2015-09-18 15:26:25

`图片上的这玩意叫做Astro Pi,Pi是什么意思我就不解释了,Astro是天文的意思,那么这个树莓派是干嘛用的,有什么功能大家应该不难猜到了吧。Astro Pi是增加了特殊定制外壳和配件的树莓派

2016-01-11 10:49:58

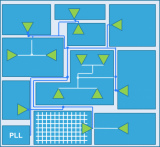

我想生成8个相位时钟。所以为此,我将不得不使用两个PLL。我想确保所有生成的时钟都没有时钟偏差。时钟向导中是否有一个功能可以指导两个PLL生成没有偏斜的时钟?或者有任何特定的方法来生成时钟?提前致谢

2018-10-11 15:01:10

1.clock计时按钮的计时时钟是多少?和核时钟一样,还是核时钟的几分频

2.显示的计时周期也是按这个时钟计算的吧???

2018-06-21 17:56:56

信号,就是这个道理。所以,连接排线一般也都在板子边沿,且尽量短,尽量用扎带固定。如果排线干扰,选用屏蔽线,效果可能会好一些。或者在线上套磁环,但这样的缺点是不方便生产。4.时钟信号导致的干扰及解决办法

2022-10-22 08:00:00

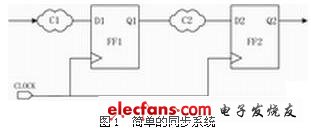

: 所设计系统的稳定情况下的最高时钟频率所设计系统的稳定情况下的最高时钟频率,他是时序分析中最重要的指标,综合表现所设计时序的性能首先介绍最小时钟周期TclkTclk = 寄存器的时钟输出延时Tco

2018-07-03 02:11:23

: 所设计系统的稳定情况下的最高时钟频率所设计系统的稳定情况下的最高时钟频率,他是时序分析中最重要的指标,综合表现所设计时序的性能首先介绍最小时钟周期TclkTclk = 寄存器的时钟输出延时Tco

2018-07-09 09:16:13

FPGA能否继续在SoC类应用中替代ASIC?CoreConsole工具是什么,有什么功能?

2021-04-08 06:23:39

运用前须知:1、IWDG所用计时时钟是不稳定的(35-60KHZ),通常取40KHZ计算.对以下代码段,定时时间为:T=prer/40000*rlr,单位是Svoid watchdogInit

2021-07-30 06:49:17

时钟振荡 计时 评估板

2024-03-14 21:24:48

在设计最初, 由于没有将时钟信号定义在全局时钟引脚上, 导致MAXPLUS II 在时间分析时提示错误:(时钟偏斜加上信号延迟时间超过输入信号建立时间). 全局时钟引脚的时钟信号到各个触发器的延时

2019-09-19 05:55:36

时钟振荡 计时 评估板

2024-03-14 22:58:14

时钟振荡 计时 评估板

2024-03-14 22:58:14

2.定时器计时,ETR模式计数(1)问题分析问题由来:项目需要对一个外部输入信号统计一段时间内负脉冲(低电平)的个数思路:一个定时器用来计时1分钟,一个定时器通过ETR模式进行边沿检测并计数(本次

2021-08-19 07:49:16

ASIC的门密度范围。SiliconCity柔性架构可让设计人员针对多种产品变化型款,创建独特的基础晶圆架构,同时通过设计复用大幅缩短客户的设计时间,减少非经常性工程(NRE)成本,并降低开发风险。

2019-08-29 06:00:52

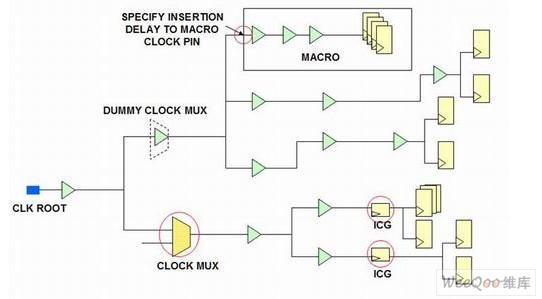

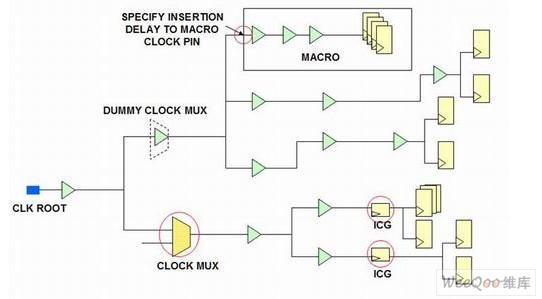

从ASIC到FPGA的转换系统时钟设计方案

2011-03-02 09:37:37

嗨,我们正在尝试使用Vivado工具链手动路由FPGA,并想知道应该使用什么工具来手动路由Virtex 7 FPGA。还可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?我们将如

2018-10-25 15:20:50

在对DCS系统进行工程的抗干扰设计时需注意什么?为了保证系统在工业电磁环境中免受或减少内外电磁干扰,必须从设计阶段开始便采取三个方面抑制措施:抑制干扰源;切断或衰减电磁干扰的传播途径;提高装置

2011-11-21 16:55:42

挑战。本文主要介绍了逻辑设计中值得注意的重要时序问题,以及如何克服这些问题。最后介绍了利用Astro工具进行时序分析的方法。关键词:ASIC;同步数字电路;时序;Astro引言 随着系统时钟频率的提高

2012-11-09 19:04:35

基于DSP的变频调速系统电磁干扰问题分析,怎么解决这些干扰?

2021-04-25 07:35:17

我的设计完全在Verilog中,并且已经使用Spartan FPGA进行了测试。我将源代码提供给ASIC工厂,以实现作为ASIC使用他们(我认为)的概要工具。我的问题是,有没有办法使用任何

2019-07-25 13:44:31

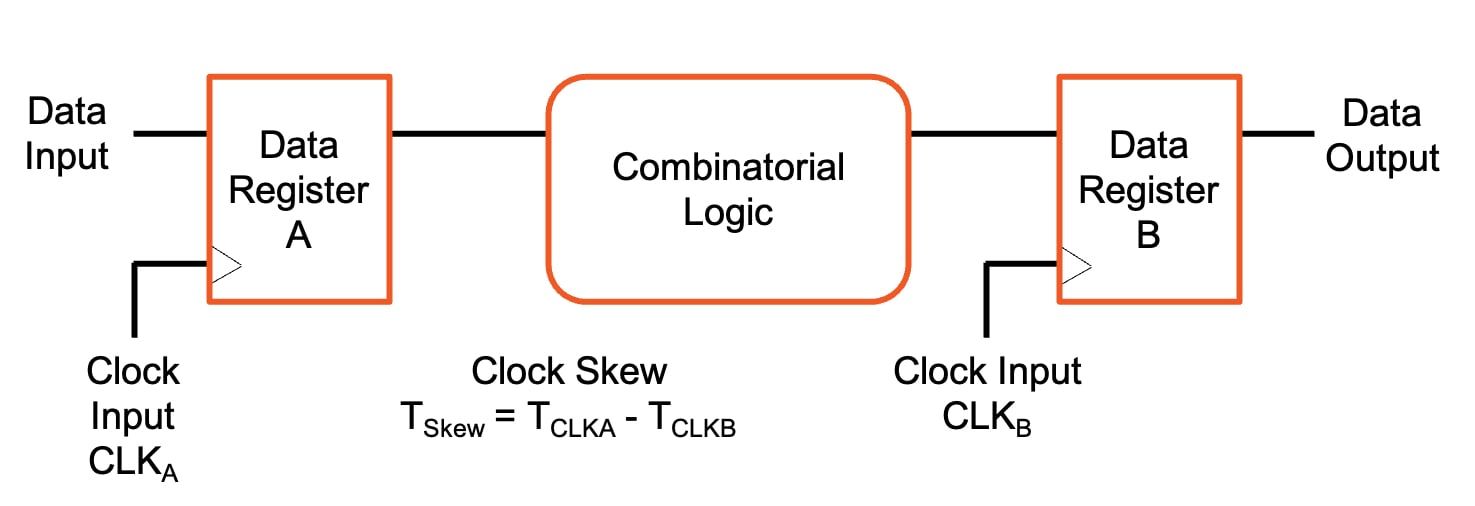

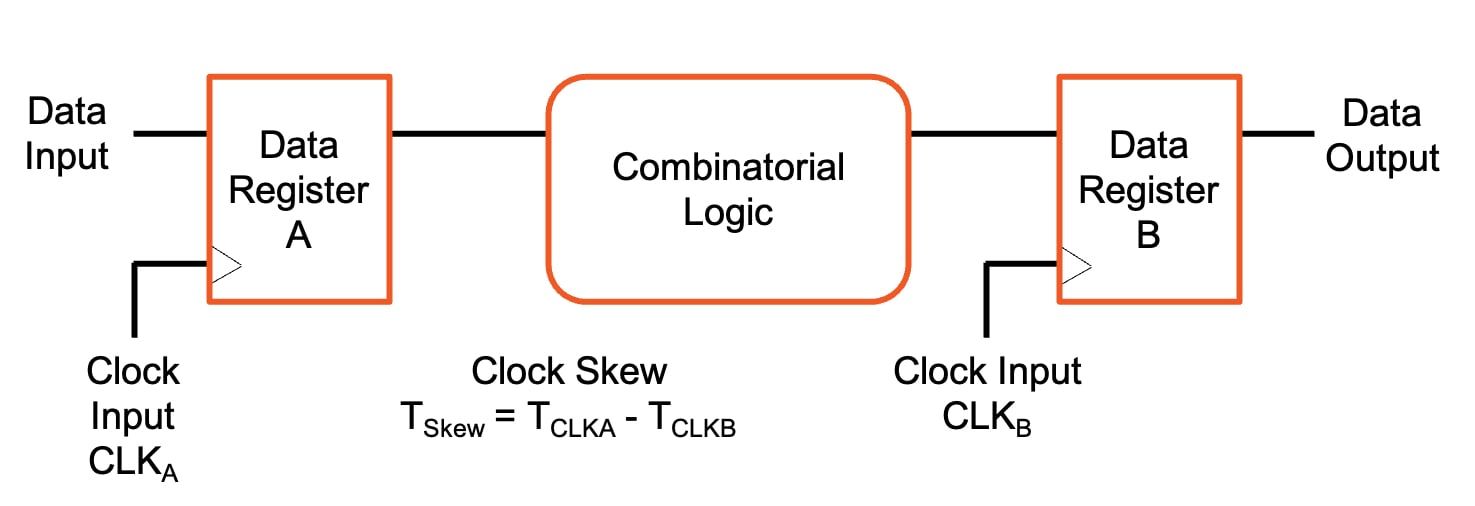

逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等

2018-04-03 11:19:08

亲爱的大家,我对时钟信号和数据信号进行采样,想要馈送到IDDR2,但它需要两个时钟。所以我的采样时钟信号无法直接馈入IDDR2,需要反向采样时钟信号,如何反转它使反转信号没有任何偏斜&与采样

2019-06-11 06:11:26

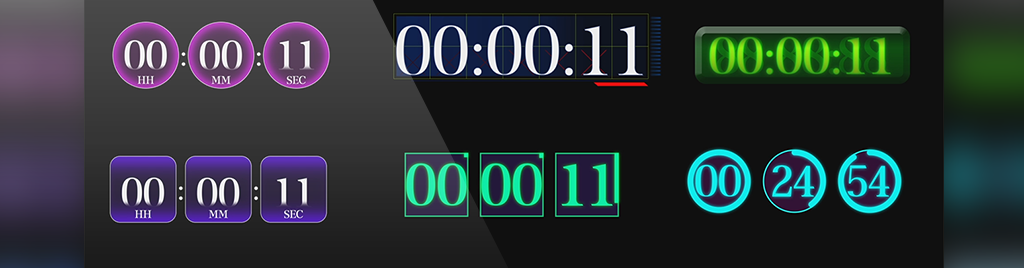

1)设计任务:完成倒计时时钟的设计。2)指标要求(1)能够分钟级的倒计时,分钟和秒显示。(2)倒计时的起始值可以设置。(3)具有暂停和清零按钮,倒计时结束报警。(4)供电电压3.3V/5V。获取该

2021-11-11 08:51:16

嗨......我有2个定制FPGA板。主FPGA具有100MHz的osc,用作参考时钟。这将进入主FPGA芯片上的DCM,用于所有时钟操作。相同的时钟被缓冲并从主板驱动出来并发送到类似的FPGA板

2019-03-15 07:17:33

嗨,复位网是否有任何gobal路由资源,因为复位类似于时钟,它有很多负载到每个FF和很多扇出。我们怎样才能在合理的偏斜范围内重置每个FF。 例如在7系列FPGA中谢谢。

2020-08-27 11:45:19

请哪位大侠帮帮忙:利用89C51设计一个时钟控制系统设计,要求:1、采用LED数码管显示时钟分、秒的计时和静态显示;2、采用串口工作方式0对4位共阳数码管进行时钟分、秒的计时。。。。。偶是新手,请给位帮帮忙,给个方案,偶先在这里谢过了。。。。。

2011-04-07 20:09:10

上升/下降沿也包含大量的奇次谐波,其在更高频率时会引起 EMI。另外,时钟通常会在板上传播一段较长的距离,从而更可能给其他组件带来干扰。通常,EMI 可通过频谱分析仪测量,如图 1 所示。图中,绿色信号存在一些超出红色 FCC 屏蔽的频率分量(300MHz…

2022-11-23 06:43:42

`请帮忙分析一下,干扰源及解决方法,不胜感激!`

2015-11-30 22:46:29

在电磁电路中的电磁兼容性很大范围是由线路贮藏和互相连接的成分决定的。有从天线返回的相应信号列是能放射出电磁能量的,其最主要是由于电流幅值,频率和电流线圈的几何面积决定的。通常,有三个主要的电磁干扰

2012-04-18 10:36:30

(FloorPlan)布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。工具为Synopsys的Astro

2020-02-12 16:07:15

时钟偏斜是什么?偏斜是由哪些因素造成的?如何去使用Astro工具,有哪些流程?

2021-04-12 06:50:56

嗨,大家好! 我遇到了一个问题,希望能帮助我。当我使用chipcope分析我的设计时,我发现全局差分时钟引脚与chipcope端口没有连接,因为它没有端口与芯片内的差分时钟引脚相连,但它

2020-06-12 14:22:16

时钟电路的电磁波干扰

所有会产生电压频率信号的电子组件都是潜在的电磁波干扰-Electro-Magnetic Interference, EMI-的来源这些电磁波信号将会影响如收音机电视或行

2010-03-18 10:35:42 29

29 防欺骗抗干扰同步时钟时间服务器防欺骗抗干扰同步时钟是针对当下北斗/GPS民用信号易受到干扰、攻击以及欺骗等特点,导致无法正常授时、定位而开发的卫星信号安全隔离产品。适用于电力、运营商、轨道交通、安防

2024-01-02 15:52:20

摘要:本文通过介绍只有双时钟的单片机系统,在多个事件需要分别定时或延时的时候,解决一个时钟完成多个计时延时的有效方法,通过这种方法可以达到对多个被控事件统一自

2006-03-11 12:38:48 471

471

AT89C51组成的时钟电路原理图

我们以一个实际的时钟电路来说明定时器的软件编程方法,时钟就是我们最为常见的显示时、分、秒为单位的计时工具

2010-03-06 10:10:13 4044

4044

ASIC,ASIC是什么意思

ASIC(Application Specific Integrated Circuits)即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造

2010-03-26 17:10:27 7379

7379 芯片的偏斜原因有哪些?

一、问题 在电子工业的许多领域,都将倒装芯片结合到新产品中,呈现增长的规律。因此,

2010-03-27 17:08:57 1558

1558 时钟计时器元件清单时钟计时器元件清单时钟计时器元件清单时钟计时器元件清单时钟计时器元件清单

2015-11-18 17:07:37 28

28 简易数字时钟计时器DIY制作,有protues仿真和源程序 。可以看看

2015-11-20 16:45:52 82

82 基于MATLAB的系统分析与设计时频分析。

2016-01-15 16:06:18 16

16 本文结合NCverilog,DesignCompile,Astro等ASIC设计所用到的EDA软件,从工艺独立性、系统的稳定性、复杂性的角度对比各种ASIC的设计方法,介绍了在编码设计、综合设计、静态时序分析和时序仿真等阶段经常忽视的问题以及避免的办法,从而使得整个设计具有可控性。

2016-11-29 01:04:11 5074

5074

时钟与计时的基本原理

2017-10-25 08:52:33 18

18 LUCT是什么? 第一层时钟树和第二层时钟树 时钟树设计及其设计方式是引起系统芯片性能差异的主要原因。 从历史角度看,ASIC时钟树设计人员利用商用自动化工具设计时钟树,以确保执行时间等性能取得预期

2018-02-10 04:45:00 7477

7477

当时钟开始计时,它将运行并且继续计秒直到它停止。当让它开始计时的程序停止的时候,时钟继续运行。但是,你想要计时的事件可能不再有效。例如,如果程序测量输入的等待时间,当程序停止的时候,输入已经被接收。在这种情况下,当程序停止的时候,程序将不能“看到”事件的发生。

2018-04-03 15:45:41 10095

10095 AN-0983:零延迟时钟计时威廉希尔官方网站

介绍

2018-04-23 10:58:22 0

0 本文主要介绍了时钟计时器设计与制作.

2018-06-26 08:00:00 42

42 在低于40纳米的超深亚微米VLSI设计中,时钟树网络在电路时序收敛、功耗、PVT变异容差和串扰噪声规避方面所起的作用要更重要得多。高性能DSP芯片会有大量关键时序路径,会要求时钟偏斜超低的全局时钟

2018-10-02 13:53:34 4476

4476

了解新的UltraScale ASIC时钟架构:如何使用它,它带来的好处以及从现有设计迁移的容易程度。

另请参阅如何使用时钟向导配置时钟网络。

2018-11-29 06:40:00 3390

3390 系统采用AT89C51单片机,以汇编语言为基础,目的是设计一个可以用四位的数码显示管能够显示时、分的电子时钟,电子时钟是基于单片机的一种计时工具,单片机通过延时中断产生一定的时间中断,用秒的定义,通过计数满60秒进一,满60分进一,满24小时清零。从而达到计时的目的,是人们生活的必要工具。

2019-01-17 08:00:00 16

16 TimeQuest Timing Analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

2019-11-28 07:09:00 1753

1753 本文首先介绍了asic的概念,其次介绍了ASIC的特点,最后介绍了ASIC设计过程。

2020-04-23 10:53:45 7603

7603 不大,因为它们只针对几种信号,可能只能在一条通道上测量问题的影响。频谱分析仪是工程师非常信赖的工具,用以测量和识别干扰源。市场上有许多不同类型的频谱分析仪,但许多人首选电池供电的小型频谱分析仪,因为他们需

2020-10-22 10:41:00 0

0 本文主要就对如何降低时钟(干扰源)的干扰进行了分析和总结,因此可以得出以下如何切断时钟干扰的传播途径的结论。

2020-09-02 16:11:09 5433

5433

的影响;但是对于10Gbps的信号,1个时钟周期为100ps,50ps的随机抖动对系统的影响是致命的。另一方面,速率提升使得通道的损耗变大,码间干扰会变得更加严重。这篇文章主要针对码间干扰的产生以及如何消除码间干扰进行分析。 码间干扰,又称ISI(

2020-09-11 14:58:19 23309

23309 在 PCB 设计中,您希望时钟信号迅速到达其集成电路( IC )的目的地。但是,一种称为时钟偏斜的现象会导致时钟信号早晚到达某些 IC 。当然,这会导致各个 IC 的数据完整性不一致。 什么是时钟

2020-09-16 22:59:02 1938

1938 去年 3 月份,一款支持 5G 的全键盘手机 Astro Slide 在 Indiegogo 平台众筹成功,却由于疫情影响迟迟没有发货。1 月 15 日,据外媒 XDA 报道,Astro Slide 将于 2021 年 6 月正式发货,并将于 9 月开放购买。

2021-01-20 16:20:02 1869

1869 时钟和计时IC评估套件-用户手册

2021-04-23 18:00:28 19

19 5G NR 架构要求将 PTP 用作主计时协议来为射频单元(Radio Unit,RU)提供计时服务(请参见 5G ChangesNetwork Timing Architectures)。从运营商

2021-05-12 16:34:02 6

6 时钟设计方案在复杂的FPGA设计中,设计时钟方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的时钟资源及它们的限制,需要了解不同英国威廉希尔公司网站

之间的权衡,并且需要很好地掌握一系列设计实践

2021-06-17 16:34:51 1528

1528

门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。 一、什么是门控时钟 门控时钟威廉希尔官方网站

(gating

2021-09-23 16:44:47 12192

12192

1)设计任务:完成倒计时时钟的设计。2)指标要求(1)能够分钟级的倒计时,分钟和秒显示。(2)倒计时的起始值可以设置。(3)具有暂停和清零按钮,倒计时结束报警。(4)供电电压3.3V/5V。获取

2021-11-06 11:51:05 38

38 CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步时钟域是指时钟频率和相位具有一定关系的时钟域,并非一定只有频率和相位相同的时钟才是同步时钟域。异步时钟域的两个时钟则没有任何关系。这里假设数据由clk1传向clk2。

2022-05-12 15:29:59 1334

1334 电子发烧友网站提供《使用FPGA的数字时钟(计时表).zip》资料免费下载

2022-11-23 10:38:36 5

5 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 686

686

AN3988 基于STM32F4的时钟配置工具

2022-11-24 08:32:13 0

0 电子发烧友网站提供《复古1980年代LED时钟/倒数计时器.zip》资料免费下载

2022-12-13 10:03:30 0

0 所有时钟信号的偏斜小于1 ps。其中一些应用包括相控阵、MIMO、雷达、电子战 (EW)、毫米波成像、微波成像、仪器仪表和软件定义无线电 (SDR)。

2022-12-22 15:19:31 628

628

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相

2023-01-05 14:00:07 949

949 LVDS解串器的偏斜裕量是其抖动容限的指标。应用笔记3821:4通道(3个数据通道加时钟通道)LVDS串行器/解串器的偏斜裕量测量展示了一种利用串行器和LVDS互连来测量偏斜裕量的方法。本应用笔记描述了如何仅使用解串器测量偏斜裕量。概述的过程几乎可用于任何LVDS解串器。

2023-01-10 09:20:05 583

583

通过了解同步电路、时钟传输和时钟分配网络,了解时钟偏斜、它是什么及其对现代系统的影响。 现代数字电子产品设计的最大挑战之一是满足时序限制的能力。保持可预测且组织良好的逻辑操作流的一种方法是在数

2023-01-27 10:05:00 2273

2273

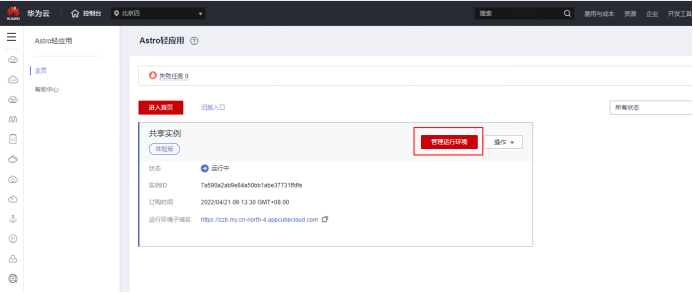

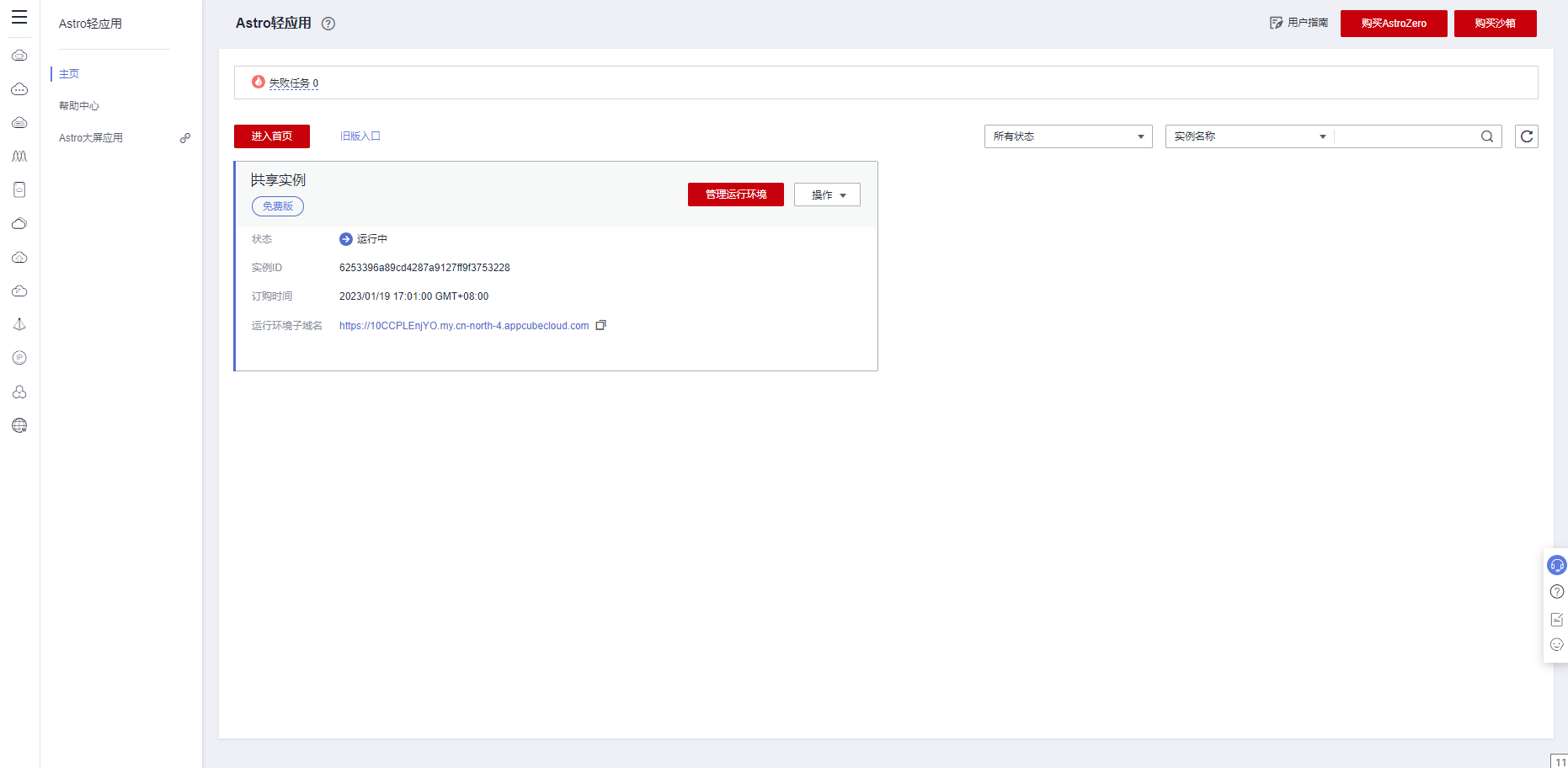

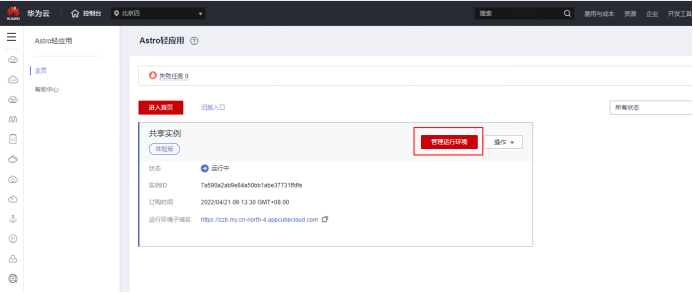

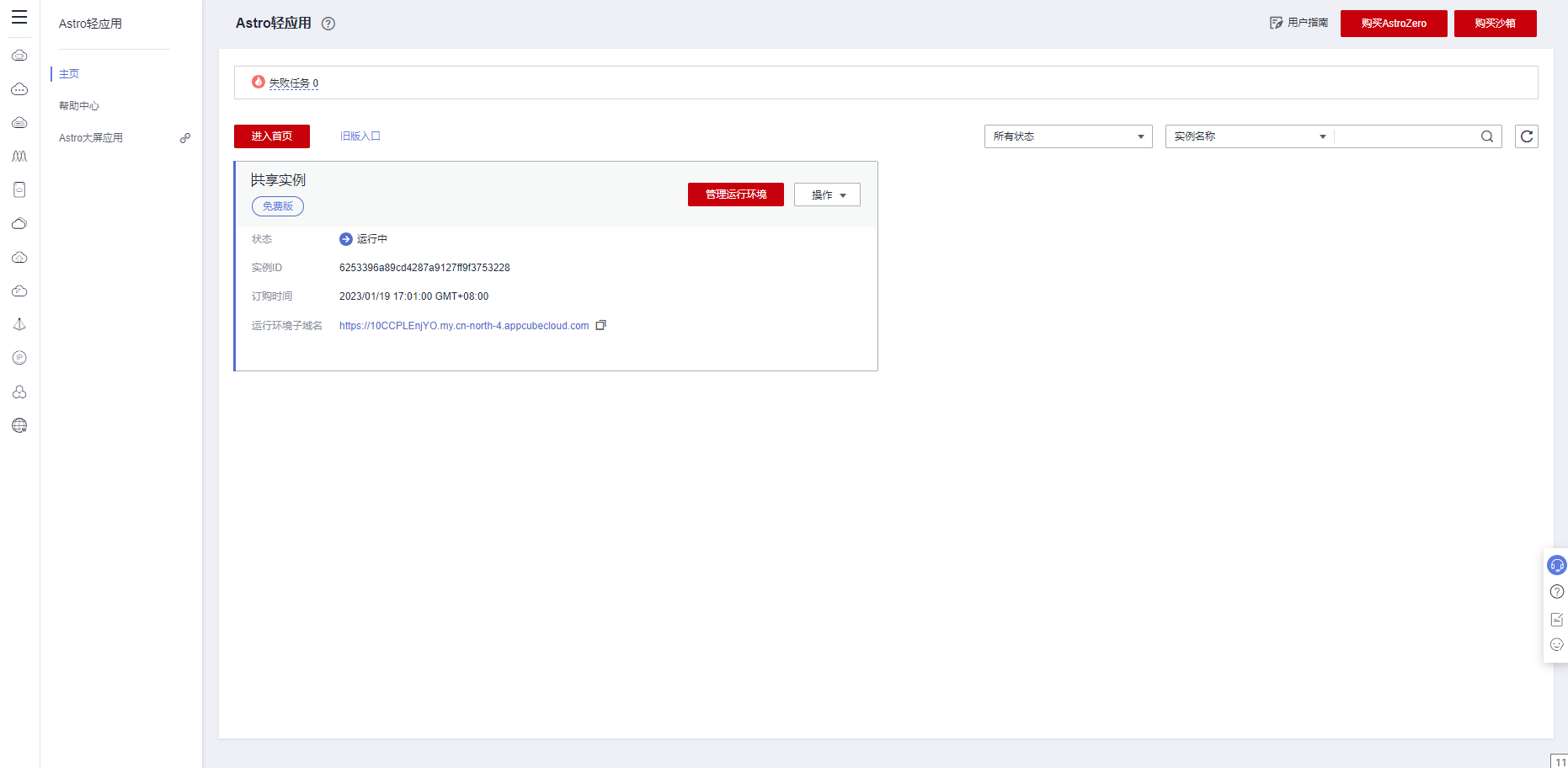

如何基于Astro零代码能力,DIY开发,完成问卷、投票、信息收集、流程处理等工作,还能够在线筛选、分析数据。实现一站式快速开发个性化应用,体验轻松拖拽开发的乐趣。 环境准备 注册华为云账号、实名

2023-03-24 20:31:56 393

393

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 电子发烧友网站提供《健身房倒计时的时钟开源设计.zip》资料免费下载

2023-06-19 15:09:45 0

0 电子发烧友网站提供《为新年倒计时制作的实时时钟.zip》资料免费下载

2023-06-19 10:19:53 0

0 时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-05 09:05:28 647

647

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-12 11:17:42 794

794

收藏这份实用又有趣的新手指南,零基础踏上华为云低代码开发的奇妙旅程。 第Ⅱ章 Astro 轻应用奇遇——用鼠标「拖拽」的开发 不被编程所困,像玩拼图一样打造订购系统! 今天,我们用鼠标拖拽的方式开发

2023-08-25 15:58:18 192

192

收藏这份实用又有趣的新手指南,零基础踏上华为云低代码开发的奇妙旅程。 第Ⅰ章 旅程的开端 发现 Astro 轻应用地图 第 1 站:创建账户 首先,你需要在华为云Astro官网注册专属账号。若已有

2023-08-25 15:58:53 329

329

据称 Astro 3.0 是首款支持 View Transitions API 的主流 Web 框架。基于该特性,开发者可以在页面导航中轻松实现淡入淡出、滑动、变形,甚至持久化有状态元素。此前只有

2023-09-01 15:15:29 414

414

终日专注「敲代码」的三位华为云 Astro 平台开发者,7 月 9 日,在华为开发者大会 2023 极客挑战赛上,给学员们开上了「小灶」。 当多数人仍纠结用哪种编程语言呈现数据时,管玥已利用华为

2023-09-05 22:47:47 665

665

SYNWIT MCU 时钟计算应用工具

2023-10-17 15:20:55 237

237

摘要:本文主要探讨华为云 Astro Canvas 在数据可视化大屏开发中的应用及效果。首先阐述 Astro Canvas 的基本概念、功能和特性说明,接着集中分析展示其在教育、金融、交通

2023-11-12 17:52:17 452

452

电子发烧友网站提供《Astro II的中文手册.pdf》资料免费下载

2023-11-16 09:32:01 0

0

电子发烧友App

电子发烧友App

评论