SAMC21(一款 Cortex-M0+ MCU)非常适合需要数学计算的应用。SAMC21 MCU 具有可进行乘法运算的快速单周期乘法器选项,还具有一个新的外设,称为除法和平方根加速器

2018-07-19 09:25:25 5283

5283 除法运算。很多人觉得不就是除法嘛,直接打上/即可,但是,FPGA是不能正确综合这个除法器的,综合的结果只是一个固定数值,而不像其他微处理器。可以这么说,用FPGA实现除法运算是比较麻烦的。

2020-06-17 10:17:27 6533

6533

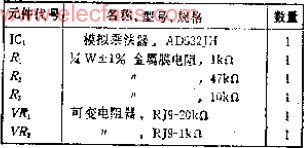

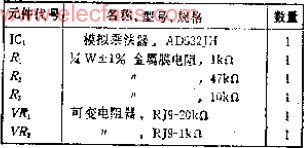

减法电路是基本集成运放电路的一种,算术运算电路主要包括数字**加法器电路、数字减法器电路、数字乘法器电路和数字除法器电路。

2024-02-19 10:00:17 310

310

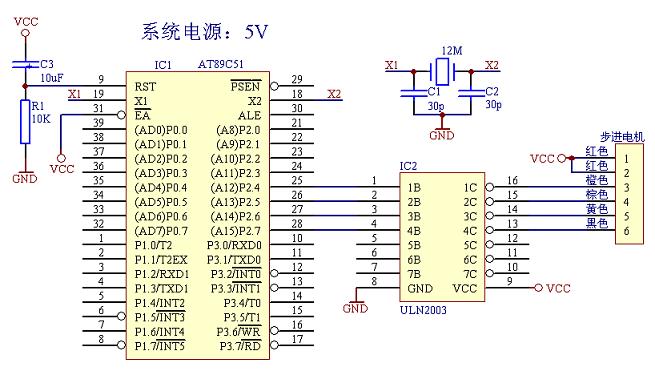

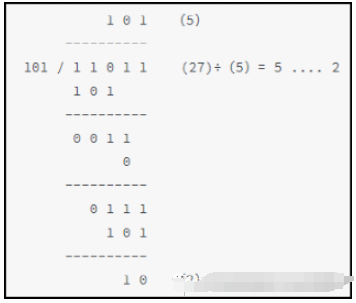

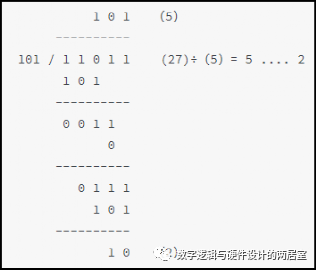

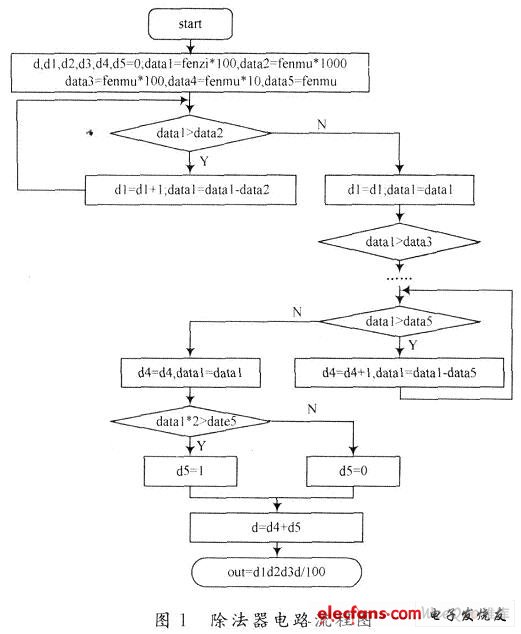

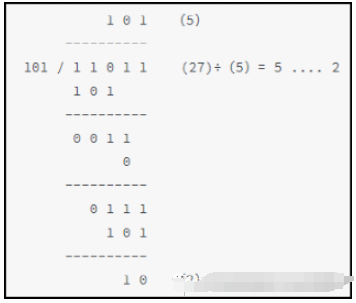

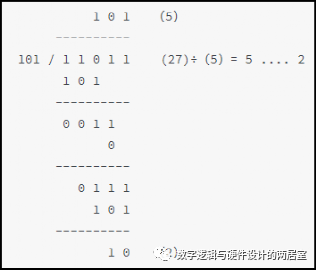

代替,比如可以先用除法运算获得整数部分,然后用求余运算获得余数,再对余数进行运算。2、本例实现一个除法运算,所得上的整数部分送P1口显示,小数部分送P0口显示。3、实现方法,本例计算101除以2的结果

2012-03-22 10:47:30

Verilog中用*实现乘法和用乘法器ip核实现乘法综合结果有哪些不同?

2016-03-18 09:35:13

刚学习FPGA一个礼拜,从树上抄了一段小程序,16位除法器,QUARTUS2调试出来波形总是不对(偶尔有几段是对的),还望大神指教,本人菜鸟。程序: module DIV16(input CLK

2015-05-05 14:12:07

一个变量除以一个常数81,怎么写啊 。想直接调用IP核,可是还没法控制什么时候进行除法运算。又不想自己写除法器求指点啊!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

2013-04-16 15:08:35

刚刚学习verilog,夏宇闻的《verilog数字系统设计教程(第三版)》中,P143中图10.3,乘法器延时为1个与门和8个全加器的延时,为什么是 8 个?我觉得应该是 10 个全加器延时,请求大神帮忙解答一下,谢了。

2014-10-10 23:04:39

我在Verilog中遇到二进制除法问题。我想得到一个包含商的输出。我稍后将处理decima的位置。以下代码完美地运行,我可以显示输出,它与我正在寻找的完全匹配。分配股息= 48

2019-08-19 10:49:19

主频在400Mhz,输入端可配置,最大128位,整数无符号除法(四舍五入),重点是在10个周期内算完。

2016-07-25 08:04:46

- 例程2,ADC滤波算法04 - 总结1us的误差,足矣改变这个世界 ————CSDN根号301 - 为什么整数位移比乘除法高效 首先,整数位运算要比乘除法要高效。如果学过计算机组成...

2021-12-24 07:33:48

4.3 实例九 除法器设计4.3.1. 本章导读要求掌握除法器原理,并根据原理设计除法器模块以及设计对应的测试模块,最后在 Robei可视化仿真软件经行功能实现和仿真验证。设计原理这个除法器的设计为

2021-11-12 07:03:52

使用AD633与AD711按照官方提供的电路搭建了一个除法器,在使用中发现与实际不符,求解答 一. 这是输入的两个信号,最上面一个作为被除信号,下面一个作为除信号。 这是通过除法器后的信号,其中

2019-02-12 14:10:52

本帖最后由 gk320830 于 2015-3-5 13:40 编辑

手册上说可以接成除法器,但没有给出实际电路,望高手指点。。。

2012-03-25 14:20:07

请问由八位的输入数据,怎么得到CRC编码后的16位数据啊?verilog里面怎么做除法运算?

2014-10-25 20:05:44

请问一下大家,几个疑问(可以肯定代码是没有问题的!):一,为什么可以在这里把小数直接强制转换成无符号的整型?二,这样强制转换后的结果可能会是零?三,这样转换后,是如何保证计算精度的?四,这样转换背后的意义在哪里?

2022-02-15 14:24:54

请问一下大家有没有用Xilinx的除法器IP核的,版本是V3.0的!我们在做有符号数除法的过程中运算结果经常出错!原先做的产品,Divider的工作频率是40M,后来工作频率变为62M时就经常出错

2015-03-06 19:42:16

,占用的资源就越多。虽然有IP可以直接调用,但我们还是要了解FPGA中除法的原理,手动来写一个除法器。FPGA中除法原理两个32的无符号整数除法,被除数a除以除数b,他们的商和余数都不会超过32位

2020-12-24 16:06:22

;humi_ge=humi_dat%10;temp_bai=temp_dat/100;temp_shi=temp_dat/10%10;temp_ge=temp_dat%10;end这个程序大神们看一下,我在ISE中不能综合但是在Quartus2中能综合,请问用verilog 实现任意整数的除法和取模怎么办?

2013-10-08 08:47:49

本帖最后由 第二道彩虹 于 2022-1-15 21:34 编辑

Labview自带函数计算精度大多为二进制32位,对于一些高精度计算精度不够。在网上没有找到Labview更高的精度函数,因此

2021-12-27 16:35:15

有效, 可以分拍有效, 这时候除法器还会根据送入除法器的接口数据顺序进行计算。 如下图时序 除数和被除数数据来临的时刻不相等, 而希望按照顺序进行做运算, 这时候使用 blocking 模式最好

2021-01-08 17:00:55

和Cordic的互联除法器的输入可以由除法器的结果或Cordic的结果直接输入,这样构成了除法器和Cordic的级联。比如计算tan(z),可以直接把Cordic的输出sin(z)连接到DVD,cos(z)连接

2018-12-11 10:57:03

`Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1概述在本例

2015-12-09 12:22:00

本帖最后由 taiyangshenniao 于 2013-9-5 16:42 编辑

各钟加法器,乘法器,除法器,的verilog 的实现,(位运算)

2013-09-05 16:41:14

`大虾们,小女子最近调程序的时候用到了ise ip core的除法器,但是调用modelsim仿真的时候发现木有进行除法啊,单独写了个除法器也还是用不了,这是什么情况呢?(vhdl写的程序哈)`

2013-06-15 11:52:45

小弟是初学者,刚把verilog基本语法看完,只会写简单的四位或者八位的加法器,但是两个4位加法器级联构成一个8位加法器不会写啊,应该是顶层调用两个四位的,但不知道具体怎么写,求大神指点!不胜感激!

2013-12-03 11:51:06

请问关于乘法器的Verilog 程序中,移位累加具体每一步是怎么走的,自己琢磨了一番,感觉不是太懂,求高手解释。(明白二进制乘法的计算过程)

2015-10-17 23:08:02

用Verilog设计五模除法电路。。。可是无知的我连五模除法电路是什么都不知道啊 !!求多模除法电路的资料啊!!

2014-03-30 10:16:00

请问下大家,,进位选择加法器和进位跳跃加法器的区别是啥啊?我用Verilog实现16位他们的加法器有什么样的不同啊?还请知道的大神告诉我一下。。

2016-10-20 20:23:54

的工况就不太适用。笔者的工作室长期承接单片机、电路、机电液、工控、自动化、软件EXE编程等项目,最近做了个单片机计算器的设计,在设计除法时利用长整形除法和取余运算,可以得到若干小数位的精度运算,与大家

2013-11-19 19:26:38

想问一下大家 单片机使用硬件除法器求出的商和余数数据怎么处理呢

2023-10-30 08:28:51

哪位有模拟除法器的电路仿真,我需要一个简单的除法运算电路。MULTISIM10上面的除法器只是个代号没有实际的型号,我用AD532来做结果不行。

2013-12-16 11:10:24

介绍了等精度测量频率的原理,利用Verilog硬件描述语言设计实现了频率计内部功能模块,对传统的等精度测量方法进行了改进,增加了测量脉冲宽度的功能;采用AT89S51单片机进行数据运算处理,利用

2011-03-07 12:44:31

定点除法器的输出是商和余数的形式,但是我想让他表示成小数的形式(因为最后要送到数码管显示),该怎么装换?求大神,给点思路也可以!总共是8位显示,而整数部分和小数部分的位数不定?怎么设计

2014-05-15 20:01:12

本文中介绍了如何在verilog编码时使用自己想要的加法器和乘法器等

2021-06-21 07:45:56

在处理双精度数时,经常会涉及到拆分双精度数的整数和小数部分。有一下几种解决方案:一、解决这个问题我们首先想到的可能是通过几个取整函数,先求取整数部分,然后利用差值求取小数部分。取整函数包括最近取整

2014-10-17 14:01:05

有没有人对如何用参数化加法器树编写Verilog有任何建议,输入参数是操作数的数量?加布里埃尔以上来自于谷歌翻译以下为原文Does anyone have any suggestions

2019-04-25 13:28:42

求助,有没有大神用verilog写过浮点矩阵乘法器的,我写出浮点乘法器和加法器之后就进行不下去了,急求助!!!只有一个积分~~~

2017-09-18 09:22:03

求大神分享一种基于Verilog计算精度可调的整数除法器的设计

2021-04-29 06:30:43

有哪位亲知道除法器选用哪种型号的比较好?是用作PSD位置传感器的外围电路,我在网上找到的最便宜的一种是一百多,不知道可不可靠。。另外,用运放实现电流到电压的转换 电阻和相位补偿的电容取多少合适呢?我看到上面有写电阻不宜过大 易产生自激,但所给原理图上用了1M。。求各路大神指点

2014-08-18 23:35:53

简单给大家分析一下嵌入式C语言编程时用到的除法与移位。 除法土豪 除法在嵌入式微处理器里可算是一个消耗大户,复杂的实现方式不仅占用了大师宝贵的计算时间而且精度有限情况下占用了大片的RAM。因此

2019-04-30 00:31:32

除法器和32bit硬件乘法器,能自动执行有符号或32位整数乘除法和开根号运算。硬件运算大大提升了应用程序的效率,减少了代码运算量,相比软件它们对于特定问题计算速度更快,位宽更大。 下面和大家一起配置

2018-11-30 09:23:40

请问在Verilog里可以直接用'/'来做除法吗?如果不能要怎样做除法呀??希望知道的人能够指点一二。。。

2016-09-08 11:33:56

判断。直到,B 完全移位后得出结果C 。 除法:首先,让被除数(A)与除数(B) 进行比较,当被除数不小于除数时,才能进行整数除法。然后,让C自加一,让被除数(A)减除数(B)后赋值给被除数(A)。直到,被除数小于除数,得出最后结果C 。计算模块的内容就是这些了。下面附上源代码:

2016-09-01 09:03:33

这是一个高速硬件除法器,要求画出此硬件的除法器的工作流程图。说明其工作原理特别是高速原理。要求有仿真时序波形图并说出说明在fpga上验证器硬件功能。

2020-12-17 09:10:03

本文在设计实现乘法器时,采用了4-2 和5-2 混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占用率;经Xilinx ISE 和Quartus II 两种集成开发环境下的综合仿真测试,与用Verilog

2009-09-17 11:13:21 27

27 TI推出的CDC706是目前市场上体积最小且功能强大的PLL合成器/乘法器/除法器之一。尽管其物理外形非常小巧,但却极为灵活。该器件能够在特定输入频率下生成几乎独立的输出频率。

2009-11-26 14:35:47 21

21 AD534是一款单芯片激光调整四象限乘法器/除法器,可提供以前只有昂贵的混合式或模块式产品才具有的精度规格。无需外部调整便可保证±0.25%的最大乘法误差。该器件具有出色的电源抑制、低温度系数,结合

2023-06-28 11:13:29

AD534是一款单芯片激光调整四象限乘法器除法器,其精度规格以前只有昂贵的混合或模块化产品才有。无需任何外部调整,AD534L的最大乘法误差保证为0.25%。出色的电源抑制性能、低温度系数以及片内

2023-08-09 16:52:53

在FPGA中实现高精度快速除法

2010-07-17 16:33:18 25

25 高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37 描述AD534是一款单芯片激光调整四象限乘法器/除法器,可提供以前只有昂贵的混合式或模块式产品才具有的精度规格。无需外部调整便可保证±0.25%的最大乘法误差。该器件具有出色的电源抑制、低温度系数

2024-01-11 15:27:16

AD532是首款预调整的单芯片乘法器/除法器;无需任何外部调整电阻或输出运算放大器,即可保证±1.0%的最大乘法误差和±10 V的输出电压范围。AD532经过内部调整,易于使用,为设计

2010-10-02 09:37:50 132

132 AD534是一款单芯片激光调整四象限乘法器/除法器,可提供以前只有昂贵的混合式或模块式产品才具有的精度规格。无需外部调整便可保证±0.25%的最大乘法误差。该器件具有出色的

2010-10-02 09:39:56 133

133 51单片机的高精度除法程序及使用

开发人员在开发51单片机应用系统过程中,往往遇到多字节除法及倒数问题。但目前一些资料中所介绍的有关程序,复

2008-09-09 10:12:28 2044

2044

并行除法器 ,并行除法器结构原理是什么?

1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成

2010-04-13 10:46:30 14666

14666 除法器对数运算电路的应用

由对数电路实现除法运算的数学原理是:

2010-04-24 16:07:27 2520

2520

用于比率计算的除法运算电路

电路的功能

本电路是用X除输入信号Z

2010-05-08 15:29:01 1618

1618

介绍一种在 8096 /96 系列单片机上实现的单精度 浮点数 快速除法。该算法采用了预估一修正的数值计算方法,并充分利用了16 位CPU 中的乘除法指令,计算速度快、精度高,有很强的实用

2011-06-03 16:47:06 93

93 辗转相除法是整数和多项式理论中求最大公因数和最大公因式的一类重要方法,对于较大的两个整数和次数较高的两个多项式而言,利用辗转相除法手动计算它们的最大公因数和最大公

2013-06-06 10:54:26 0

0 模拟除法器是一种能实现两个模拟量相除的电子器件。目前不仅应用于模拟运算方面,而且已扩展到无线通讯、电视广播、人工神经网路、机器人控制威廉希尔官方网站

等领域。此外,模拟除法器在模糊控制和测量仪表中也是非常重要的器件。

2014-09-19 15:14:31 3096

3096 计算机如何来计算除法的?

第一步:分析除法

第二步,计算机中对第一步的模拟(真值)

2015-12-31 10:43:18 15

15 8乘8乘法器verilog源代码,有需要的下来看看

2016-05-23 18:21:16 24

24 同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高.加法器是一种数位电路,其可进行数字的加法计算。当选用同相加法器时,如A输入信号时,因为是同相加法器,输入阻抗高,这样信号不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 55183

55183

Verilog-A 将设计精度推向一个新的水平

2017-01-14 15:20:31 13

13 Verilog-A 将设计精度推向一个新的水平

2017-01-14 15:20:31 12

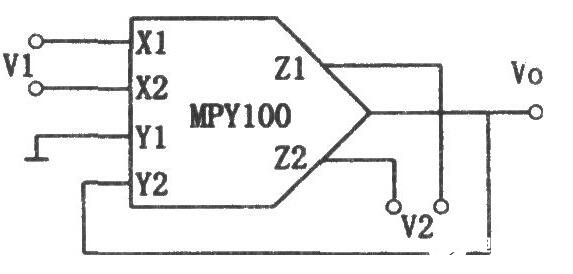

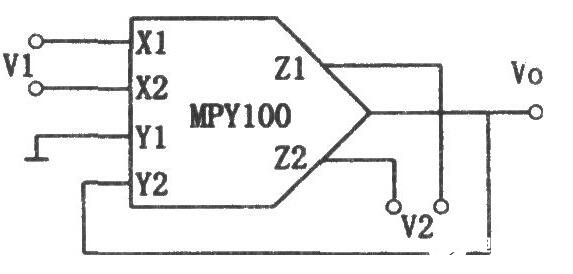

12 输入信号为V1、V2,输出Vo为Vo=10V2/V1。这种除法器是将乘法器接在运算放大器的反院回路组成的。V1的输入范围为-0.2V到10V,V2的输入范围为-10V到10V。

2019-12-31 14:12:44 17759

17759

在FPGA的开发应用中,大多数EDA软件(后面以altera QuartursII为例)都提供乘除法、开方运算的设计向导,或提供LPM宏函数,但普遍占用资源量大。而在许多信号处理应用中,要求计算精度

2020-07-29 17:48:57 1155

1155

verilog实现加法器,从底层的门级电路级到行为级,本文对其做出了相应的阐述。

2021-02-18 14:53:52 5585

5585

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数威廉希尔官方网站

来实现。乘法器不仅作为

2021-02-18 15:08:01 24392

24392

AD533:低成本乘法器、除法器、平方器、平方器、根过时数据表

2021-04-30 21:05:33 3

3 AD533:低成本乘法器、除法器、平方器、平方根过时数据表

2021-05-07 10:50:33 20

20 AD734:10 MHz四象限乘法器/除法器数据表

2021-05-15 10:18:05 12

12 简化合成器的有源乘法器和除法器

2021-05-16 17:15:02 9

9 介绍各种加法器的Verilog代码和testbench。

2021-05-31 09:23:42 19

19 4.3 实例九 除法器设计4.3.1. 本章导读要求掌握除法器原理,并根据原理设计除法器模块以及设计对应的测试模块,最后在 Robei可视化仿真软件经行功能实现和仿真验证。设计原理这个除法器

2021-11-07 10:51:04 18

18 整数在 IEEE 的规定上有短整数 short integer , 中整数 integer 和 长整数 long integer

2023-02-13 15:00:13 1142

1142 14 级纹波进位二进制计数器/除法器和振荡器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 14 级纹波进位二进制计数器/除法器和振荡器-HEF4060B

2023-02-15 18:54:07 1

1 取被除数的高几位数据,位宽和除数相同(实例中是 3bit 数据)。

2023-03-27 11:32:13 502

502

本文是本系列的第四篇,本文主要介绍FPGA常用运算模块-除法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:20:45 1840

1840

取被除数的高几位数据,位宽和除数相同(实例中是 3bit 数据)。

2023-05-30 17:31:39 742

742

进行整数除法时,结果值略去小数部分,只取整数部分

2023-06-25 10:17:37 3472

3472

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想打打拍改善下时序都不知从何下手。

2023-07-04 10:03:39 599

599

使用IAR IDE仿真RL78内置硬件乘法器和除法器注意事项

2023-10-30 17:04:14 468

468

电子发烧友App

电子发烧友App

评论