我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

自然毫无压力。这其中还有软核和硬核的区别,不过除了性能,使用方法大同小异。所谓IP核,就是把各种专用集成电路用硬件描述语言描述,然后烧到FPGA里形成专门的电路,这样就不必另外搭芯片了,所有的电路在

2020-10-22 11:28:52

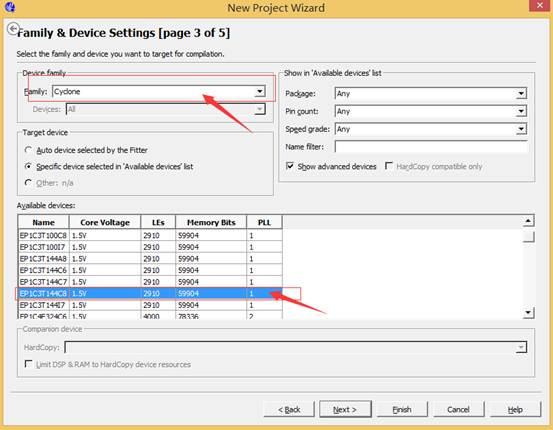

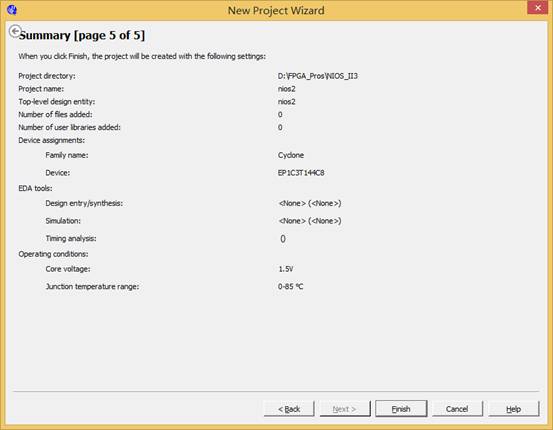

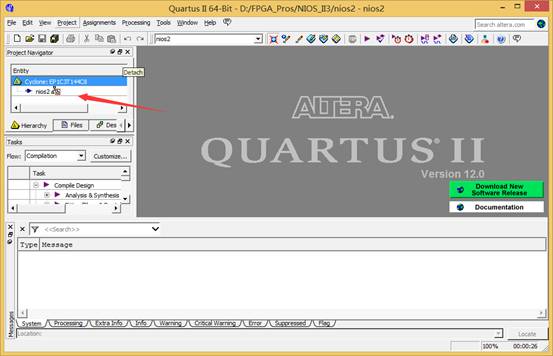

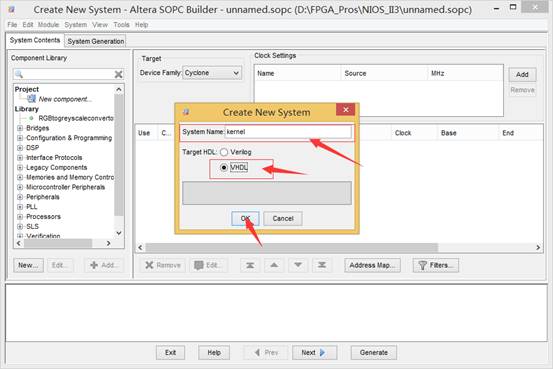

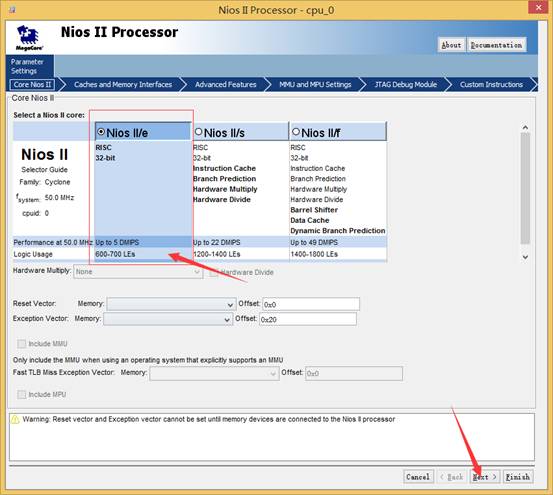

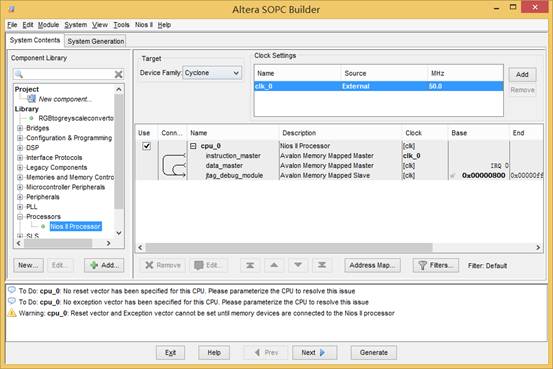

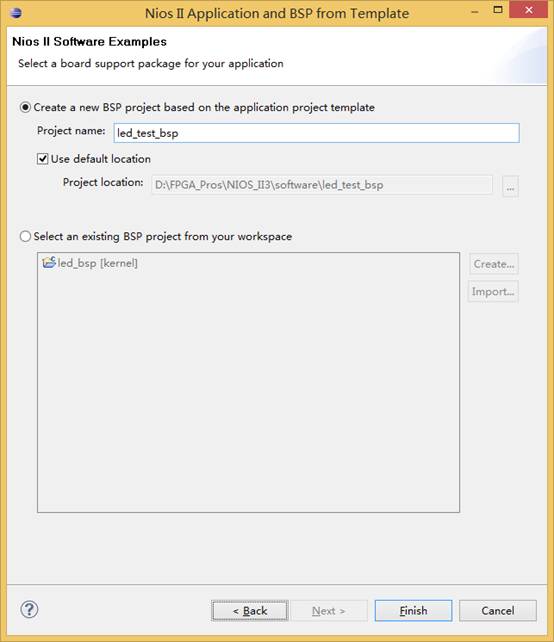

FPGA是现场可编程门阵列,是可编程逻辑器件(PLD)的一种。 NIOS II是一种知识产权核(IP Core),是嵌在FPGA内部的处理器软核,相当于在FPGA内部设计了一个微处理器

2018-08-17 09:59:27

FPGA和Nios_软核的语音识别系统的研究引言语音识别的过程是一个模式匹配的过程 在这个过程中,首先根据说话人的语音特点建立语音模型,对输入的语音信号进行分析,并提取所需的语音特征,在此基础上建立

2012-08-11 11:47:15

(Phase Locked Loop)、DSP和CPU等软处理核(Soft Core)。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向

2023-05-30 20:53:24

Danny Biran:对宽带的需求使可编程逻辑成为DSP和嵌入式应用的最佳选择。Altera的Nios II嵌入式处理器是Altera为嵌入式应用准备的软核处理器,能够帮助FPGA设计人员迅速开发最适合的处理器系统,其定制处理器内核、外设、存储器接口和定制硬件外设满足了系统独特的需求。

2019-07-23 08:13:18

是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC 阶段,IP 核设计已成为ASIC 电路设计公司和FPGA

2018-09-03 11:03:27

FPGA硬核与软核处理器有什么区别和联系?

2023-05-30 20:36:48

如何根据成本、功耗和性能来选择微处理器?FPGA结构中硬核和软核的特点是什么?处理器IP有什么重要性?

2021-04-08 06:16:37

求大神,FPGA内部的PCI的IP软核实现PCI接口设计?

2013-05-02 16:12:21

SOC设计领域的核心威廉希尔官方网站

-软/硬件协同设计摘要:基于IP库的SOC必将是今天与未来微电子设计领域的核心。它既是一种英国威廉希尔公司网站

,也是一种设计方法学。一块SOC上一定会集成各种纯硬件IP、和作为软件载体

2009-11-19 11:19:30

Altera公司意欲通过更先进的制程工艺和更紧密的产业合作,正逐步强化FPGA协同处理器,大幅提升SoC FPGA的整体性能,为抢攻嵌入式系统市场版图创造更大的差异化优势。随着SoC FPGA在

2019-08-26 07:15:50

倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。SoC定义的基本内容主要在两方面:其一是它的构成,其二

2016-05-24 19:18:54

的SoC设计方案——SoPC(System on a programmable chip)。随着百万门级的FPGA芯片、功能复杂的IP 核和可重构的嵌入式处理器软核的出现,SoPC设计成为一种确实可行

2019-07-12 07:25:22

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如

2019-10-11 07:07:07

使用fpga做一个arm的软核处理器,那么用户程序如何烧到rom里面,fpga又如何能使rom里的程序加载到ram运行呢?对于硬件如何启动软件运行不懂,希望有人能解答一下。

2017-03-31 15:31:33

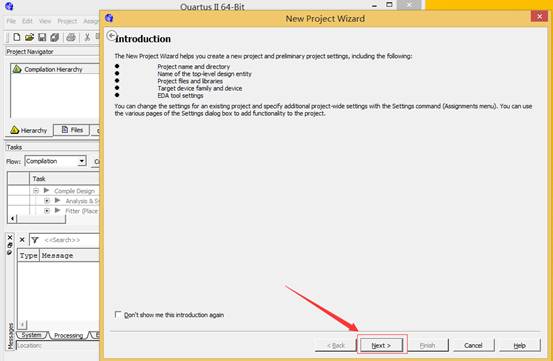

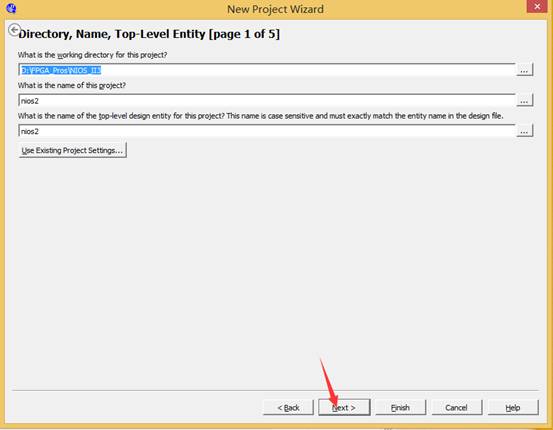

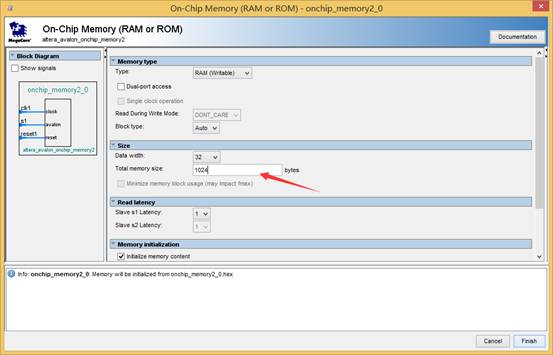

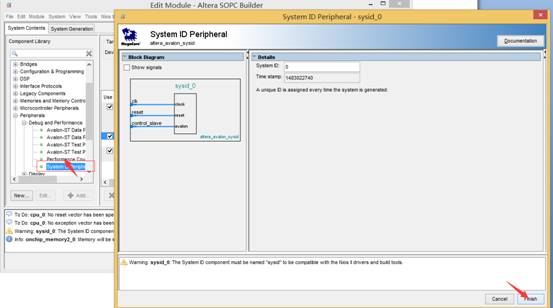

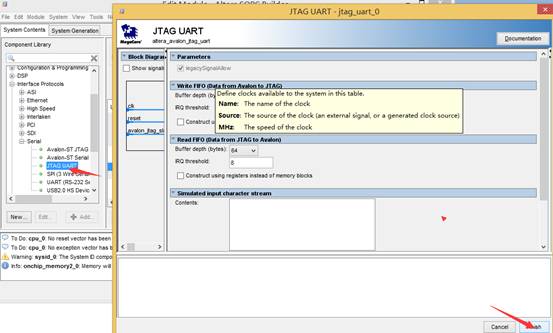

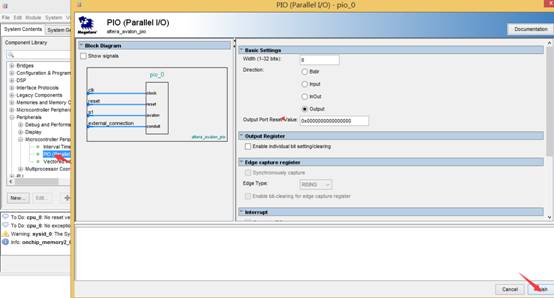

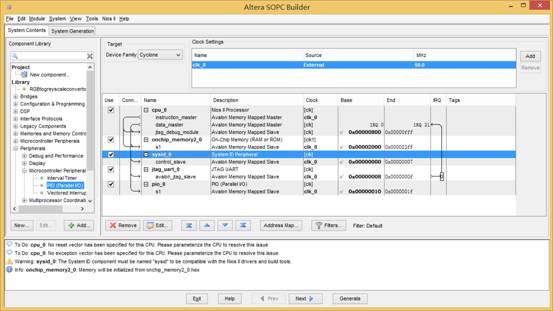

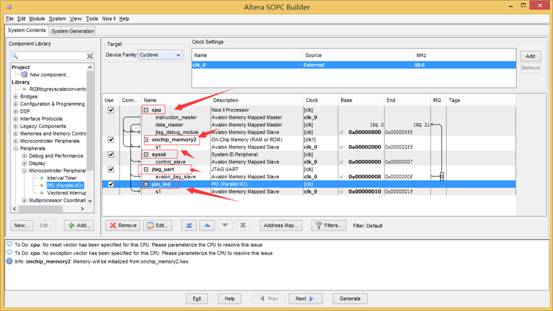

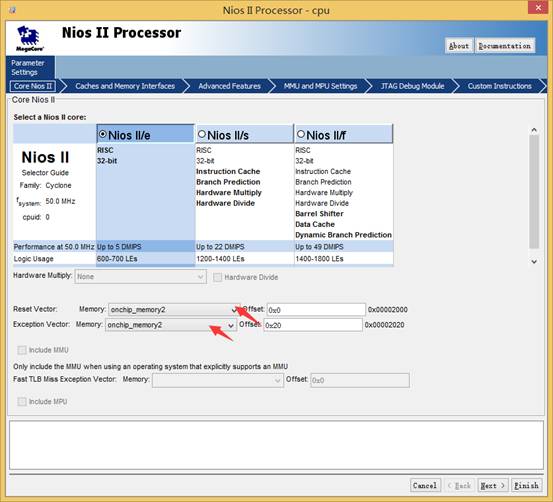

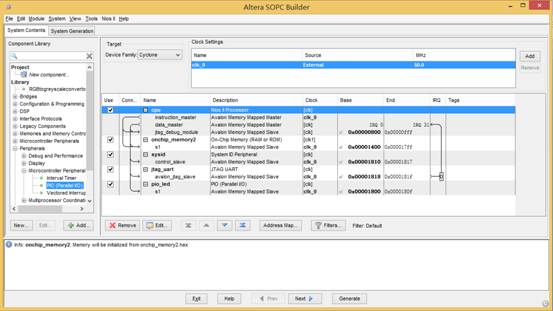

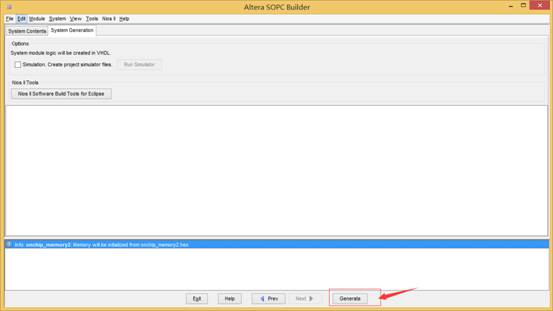

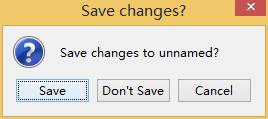

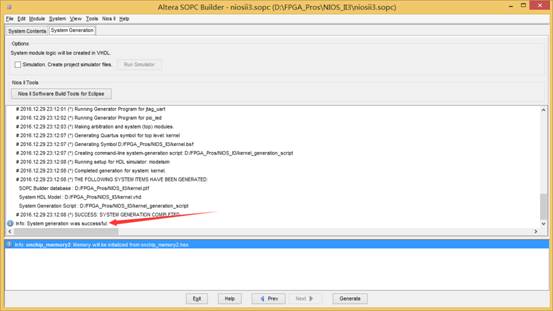

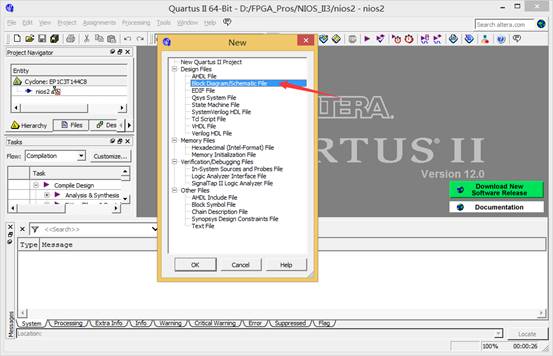

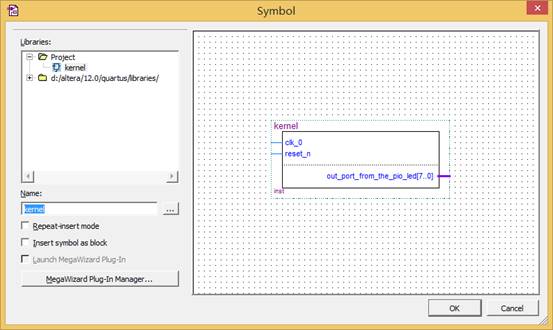

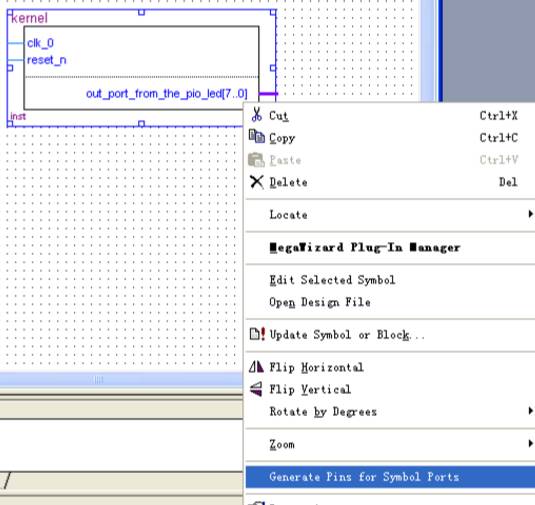

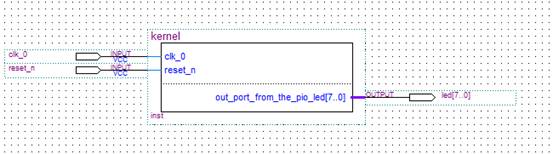

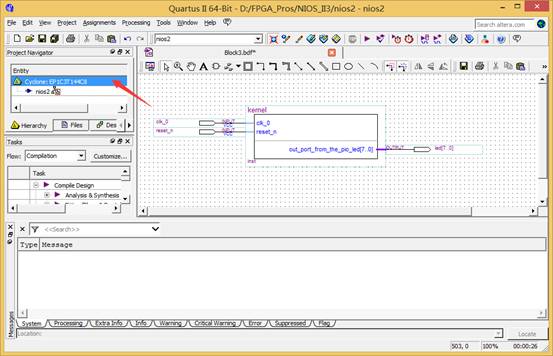

求用sopc builder定制IP核的步骤,是9.0的软件,假设硬件代码已有

2013-09-14 18:35:40

软核与fpga如何共用一块flash?

目前fpga开发板上只有一个flash,用nuclei 向软核中下载程序掉电就不跑了,请问怎么解决?

2023-08-12 06:05:26

; 2008年6月11号,为帮助系统级设计人员在FPGA软核

2008-06-17 11:40:12

)放置flash 偏移地址0x50000处,关闭看门狗,重新配置后,发现fpga只更新了硬核,软核没有运行。通过测试,发现更新完硬核后,软核还是找到的第一个程序软核入口。没有找到要更新程序软核入口地址。不知道如何设置,使重新配置后,能够找到更新程序软核地址?希望大神帮助。。感激

2017-07-30 10:21:09

[url=]ISE中应用MicroBlaze软核[/url]

2015-12-14 13:22:42

FPGA 架构的软核 RISC-V CPU(图 1)和在 PolarFire SoC FPGA 中实现的硬核 CPU 内核。此外,Mi-V 提供了由 Microchip 及其合作伙伴开发的一套广泛

2021-09-07 17:59:56

ArduZynq 和 TE0726-03M ZynqBerry SBC 中的 Zynq Z-7010 SoC 的 FPGA 容量存在显著差异。虽然所有 Zynq-7000 SoC 都采用双核 Arm

2018-08-31 14:43:05

原谅我记忆力不好。。。花了好久弄明白的东西才十个小时不到就忘记了,所以趁现在记得赶紧记录下来。本文内容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

第一章、为什么工程师要掌握FPGA开发知识? 5第二章、FPGA基本知识与发展趋势 72.1 FPGA结构和工作原理 72.1.1 梦想成就伟业 72.1.2 FPGA结构 82.1.3 软核、硬核

2014-11-03 17:14:22

好的浮点数参数数据进行补偿运算,消除零偏及温漂。这其中要用到一定量的浮点运算,原本计划采用FPGA+DSP的架构,但板子面积有限。以前用过斯巴达3系列芯片的核,故决定浮点运算部分采用软核来实现,可以省掉一片DSP。

2016-10-12 09:52:40

相比之前学习数电时对FPGA的学习,经过一段时间对锆石A4的试用之后对FPGA有了一个全新的认识,最近开始学习FPGA深层次的东西,开始学习软核部分,由于自己也在学单片机、嵌入式等,所以最近才真正

2016-10-11 19:28:32

代码调用在硬modem与软modem之间的选择,看完你就懂了

2021-05-31 06:59:04

本文介绍在使用Arm DesignStart计划开放的处理器核搭建SoC并通过FPGA实现的过程中所用工具软件(不介绍如何操作),理清“软件编程”和“硬件编程”的概念,熟悉SoC设计的流程。软硬件

2022-04-01 17:48:02

想问问virl_sdn_fsdprb_1在arm核里有什么作用呢?看名字可以猜一下功能吗

2016-09-06 14:36:33

FPGA(FieldProgrammableGateArray)译作中文为:现场可编程门阵列,也就是设计者可以在现场对可定制的数字逻辑进行编程的集成电路。 1 什么是FPGA? 首先,如果你从未

2019-09-26 14:44:42

的实时人脸检测 SOC介绍项目基于FPGA(Xilinx Spartan7 XC7S50)构建的ARM Cortex-M3软核SoC实现了实时人脸检测,通过CMOS-OV5640 Sensor采集实时

2022-08-25 16:31:14

FPGA上搭建一颗私人定制的ARM Cortex-M0或Cortex-M3内核的SoC,ARM DesignStart计划提供了处理器核,通过加入AXI总线,可以添加更多的AXI外设,如GPIO、UART、SPI、TIMER、INTC等。原作者:wcc149

2022-07-27 16:58:55

需要什么样的IP核(软核或硬核)?2.如果我们想在FPGA内部实现带有嵌入式处理器的HDMI,DVI和DispalyPort,它可以是带有ARM的软核Microblaze或SOC FPGA,是否需要任何

2019-02-19 10:09:29

1、在Picorv32 / 蜂鸟E203软核上运行RT-Thread 首先介绍一下我用的 FPGA 开发板,也就是荔枝糖(EG4S20),这块开发板性价比应当算是很高了,100RMB有20K逻辑

2022-09-16 16:15:39

在Xilinx FPGA上使用Cortex M1 软核——Keil中使用J-Link调试Cortex-M1嵌入式工程本文的软件代码部分参考自ARM提供的例程。

2021-12-15 08:36:50

UART内部可划分为哪几个模块?这些模块有什么功能?基于APB总线的UART接口软核该如何去设计?

2021-06-18 08:20:15

基于DSP核控制的SoC系统是由哪些部分组成的?基于DSP核控制的SoC系统该如何去设计?

2021-06-18 09:42:47

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

引言随着半导体威廉希尔官方网站

的发展,深亚微米工艺加工威廉希尔官方网站

允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

硬核确实能够提供比软核更好的性能。通过使用锁存、动态逻辑、三态信号、定制存储器等,全定制设计团队能实现比完全静态综合的设计更好的结果。对于需要达到现有工艺和英国威廉希尔公司网站

极限性能的SoC来说,全定制硬核

2021-07-03 08:30:00

导航系统SoC芯片设计的要求有什么?如何构建基于LEON开源软核的SoC平台?

2021-05-27 06:18:16

on Chip)是以嵌入式系统为核心,以IP复用威廉希尔官方网站

为基础,集软、硬件于一体的设计方法。使用IP复用威廉希尔官方网站

,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点

2019-08-20 07:53:46

对设计进行综合,下载到FPGA中就可以方便地实现一个具有高速DSP功能的嵌入式处理器。那么直接在读写寄存器上进行嵌入式软核Nios Ⅱ串口编程,有哪些方法?我们应该注意哪些事项呢?

2019-08-06 06:37:27

Altera公司的FPGA作为全定制芯片的一个代表正在得到日益广泛的应用。为了用户使用方便,Altera公司推出嵌入式软核NiosⅡ可以便利地使用工具生成并放人FPGA芯片中。NiosⅡ软核可以在用

2019-10-25 07:25:38

有没有带DSP软核的FPGA,要求DSP运行速度在50kHz以上。

2014-09-29 18:13:51

FPGA的学习难度和CPLD的学习难度是一样。区别在于FPGA的逻辑资源比CPLD的逻辑资源多得多,FPGA可以实现比较复杂的逻辑设计和信号处理算法,CPLD一般用于 简单的逻辑设计。 所以建议你从

2014-09-16 17:52:27

你好 我对Saprtan 3E有一些疑问。 (1)当试图将软处理器嵌入到传统FPGA中时,主要问题是什么以及如何解决它。(2)Saprtan 3E如何解决这个问题,因为它需要将软核处理器嵌入到传统

2019-06-05 07:48:29

SoC,即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁剪、可升级、可扩充,并具备软硬件在系统可编程的功能。它结合了SoC和FPGA的优点,具有以下基本特征:至少包含

2020-03-13 07:03:54

”在一起,并且一开始不熟悉工具软件,可能会感觉难以上手。本文介绍在使用Arm DesignStart计划开放的处理器核搭建SoC并通过FPGA实现的过程中所用工具软件(不介绍如何操作),理清“软件编程

2022-07-13 15:04:56

什么是三相全控桥整流电路?怎样去设计IP软核?怎样对IP软核进行仿真及验证?

2021-04-23 07:12:38

把软核移植到自己的FPGA板卡后,需要设计硬件模块,设计的硬件模块怎么与软核通信呢?通过软核的ICB总线吗?如果想把ICB总线转为AXI总线,需要哪些操作呢?

2023-08-12 07:08:40

模块间的协调控制由FPGA软核来完成。FPGA软核能够实现与普通单片机相同的功能,进而可以通过一块芯片同时实现信号处理以及外围接口控制,节省了电路空间。FPGA软核作为整个系统的监控,能够不停 地接收

2014-03-16 23:39:13

本文介绍的是基于RISC体系结构的8位高速MCUIP软核的设计与实现,采用Verilog HDL自上而下地描述了MCUIP软核的硬件结构,并验证了设计的可行性和正确性。在实际硬件电路中,该IP核的运行频率达到75MHz,可应用于高速控制领域。

2021-04-19 07:28:21

请问谁手里还有原来ip-extreme免费版本的coldfire for altera软核,能否分享给我一份?

2021-06-21 06:25:01

本文介绍了一种基于FPGA及NiosII软核处理器与TFT-LCD接口的方法。它直接采用CPU对存贮器的读写,实现了对TFT-LCD屏的实时操作。它具有直接、有效和速度快等特点。该设计使CPU对TFT-LCD的控制极其简单化。

2021-05-08 07:21:11

最近新接手个project,要求将ARM Cortex M0 软核 嵌入到Nexys 4 FPGA 中,然后设计自己的microprocessor,再设计外围电路,由于之前没接触过,求教这个据说

2014-06-12 21:13:15

最近新接手个project,要求将ARM Cortex M0 软核 嵌入到Nexys 4 FPGA 中,然后设计自己的microprocessor,再设计外围电路,由于之前没接触过,求教这个据说

2014-06-12 21:13:37

本文介绍了基于LEON3开源软核处理器的动态图像边缘检测SoC设计。 实验结果表明该SoC系统工作正常,可以实现每秒22~25帧,最佳分辨率为400×240和640×480的动态图像边缘检测

2021-02-22 07:50:13

我已经搭建好了软核microblaze,但是用sdk编程却看不懂,请教大侠如何学习在sdk内编程?

2014-03-04 17:15:00

新手学习FPGA有点疑问: 1, 很多教程所谓的NIOSII只是一个软核吧, 跟我选哪款FPGA处理器没关系吧? 2, 这么说的话我买黑金199块钱的那款板子也完全够用?

2019-04-08 09:34:36

核的分类和特点有哪些?在FPGA设计中的核分为哪几种?核基FPGA是如何设计的?软核的设计及使用是什么?

2021-04-14 06:25:39

VCU110板的Micro SD能否用于基于XCVU190的定制soc系统外设或仅配置FPGA?

2019-09-26 07:50:10

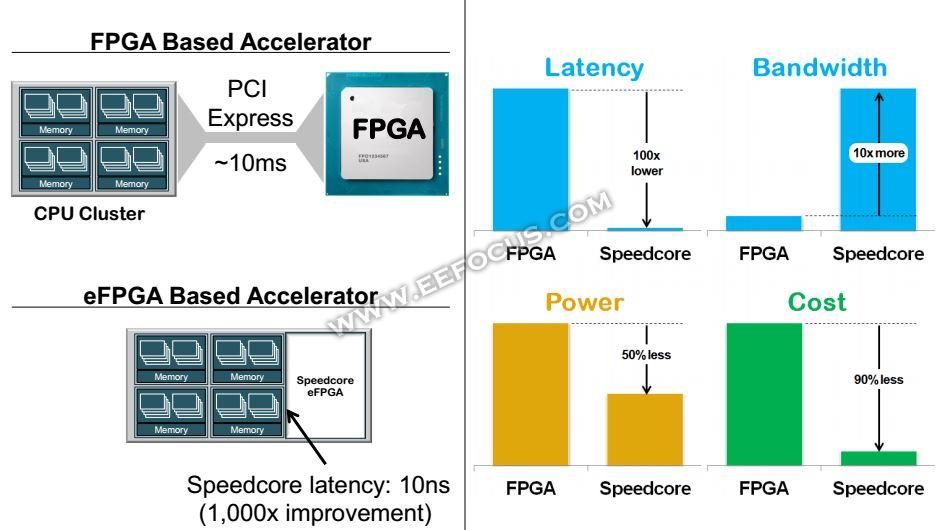

选择ASSP还是采用合适的SoC? 工程是通常都会充分权衡,并进行一番性能折衷,因为如果选用ASSP,虽然便于实施,但会阻碍产品定制与差异化的发挥。于是越来越多的OEM厂商利用FPGA,从成本、功耗

2011-06-28 16:03:06

设计周期,提高设计质量。现场可编程门阵列FPGA具有可编程特性,用户根据特定的应用定制电路结构,因此其处理速度大大超过通用处理器。与ASIC相比,FPGA的缺点是在提供灵活的可编程同时,则以芯片的面积、功耗和速度做为代价。

2019-07-29 08:33:45

SoC,即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁剪、可升级、可扩充,并具备软硬件在系统可编程的功能。它结合了SoC和FPGA的优点,具有以下基本特征:至少

2019-08-23 08:18:51

基于FPGA 的SOC 系统中的串口设计

作者:葛锐 欧钢摘要:本文在XILINX FPGA 中采用嵌入式处理器Picoblaze 进行SOC 设计,以较少的

2010-02-08 09:48:37 21

21 SoC FPGA使用宽带互联干线链接,在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括处理器、外设和存储器接口。Cyclone V SoC FPGA在一个基于ARM的用户可定制芯片系统(SoC)中集成了

2012-09-04 14:18:14 4604

4604

本文是关于Altera公司SoC FPGA 的用户手册(英文版) 。文中主要介绍了什么是SoC FPGA、SoC FPGA相关知识介绍、为什么要使用SoC FPGA以及SoC FPGA都应用到哪些方面。

2012-09-05 14:03:08 153

153 现在,您可以采用 Altera SoC 器件来设计定制器件,这是我们流行的28 nm Cyclone V 和 Arria V 系列中的型号。我们的 SoC 器件将帮助您满足多变的市场需求和接口标准。

2013-10-10 15:51:34 137

137 有不少喜欢将FPGA与MPU做比较,其实应用有很大不同。FPGA适合行业个性化定制,如协议、前后仿功能逻辑实现甚至综合包括现在流行的卷积算法等. ARM架构的MCU及MPU已渐成行业主流, 边际成本

2019-01-17 17:18:08 5564

5564

小梅哥最新款FPGA_SOC

2019-05-28 06:09:34 3982

3982 小梅哥最新款FPGA_SOC

2019-08-30 06:10:00 3548

3548

本文将手把手教你如何基于ARM DesignStart计划,在FPGA上搭建一个Cortex-M3软核处理器。 以Xilinx Artix-7系列FPGA为例,介绍如何定制一颗ARM

2022-08-22 09:00:27 1540

1540 开始SoC FPGA的学习路程还是蛮难的,不仅要熟悉整个的设计流程,而且还要掌握FPGA以及软件方面的知识,尤其大概看了一下后面的整体设计部分,操作起来还是较为繁琐的,以至于让人晕头转向。尽管如此

2023-03-30 10:13:35 6239

6239

电子发烧友App

电子发烧友App

评论