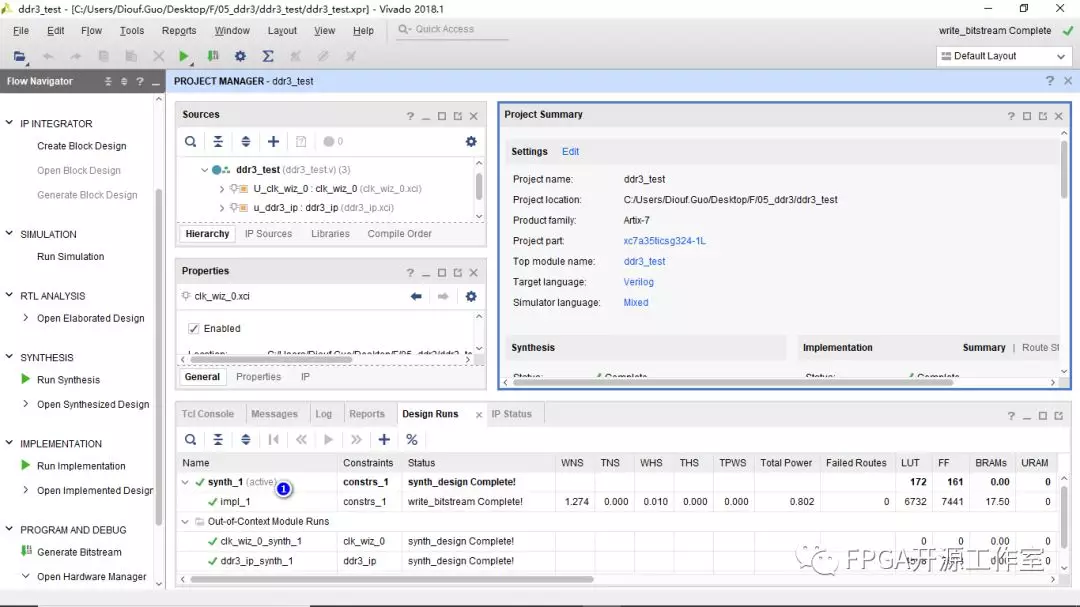

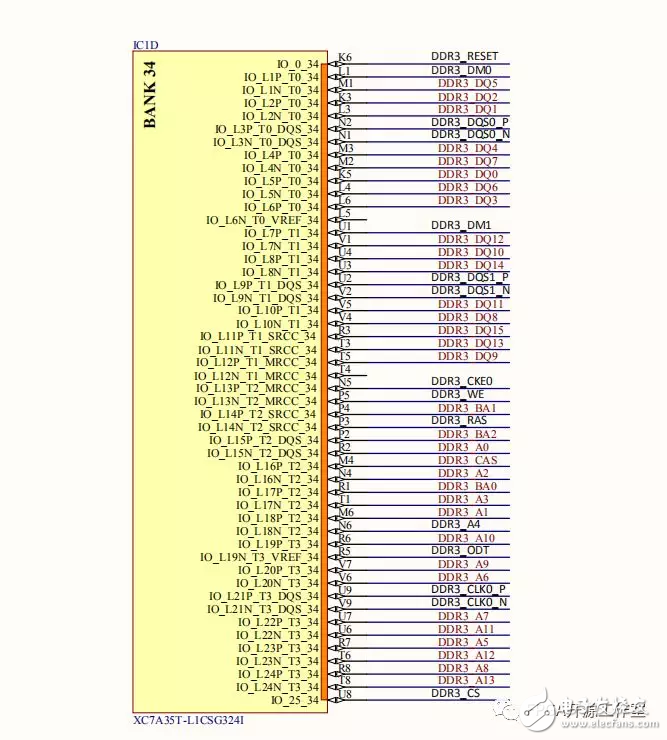

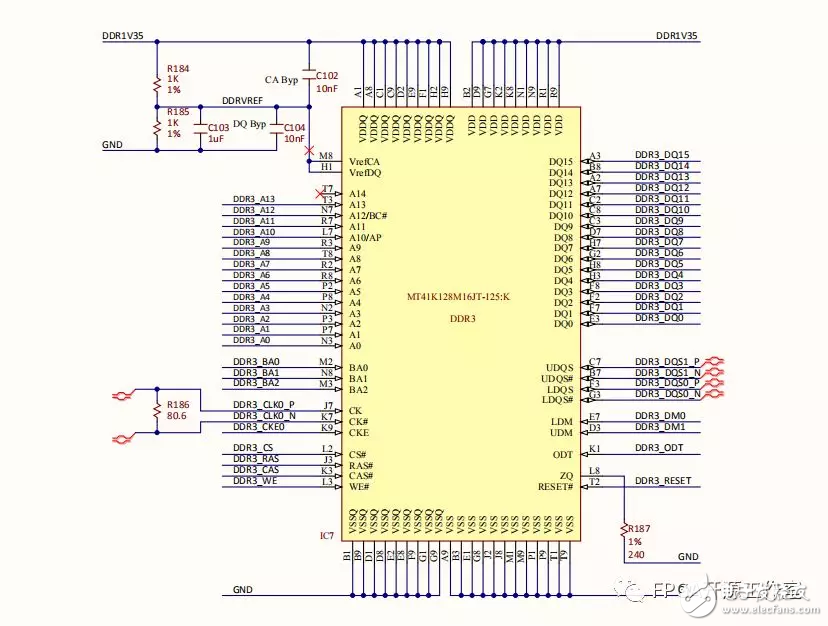

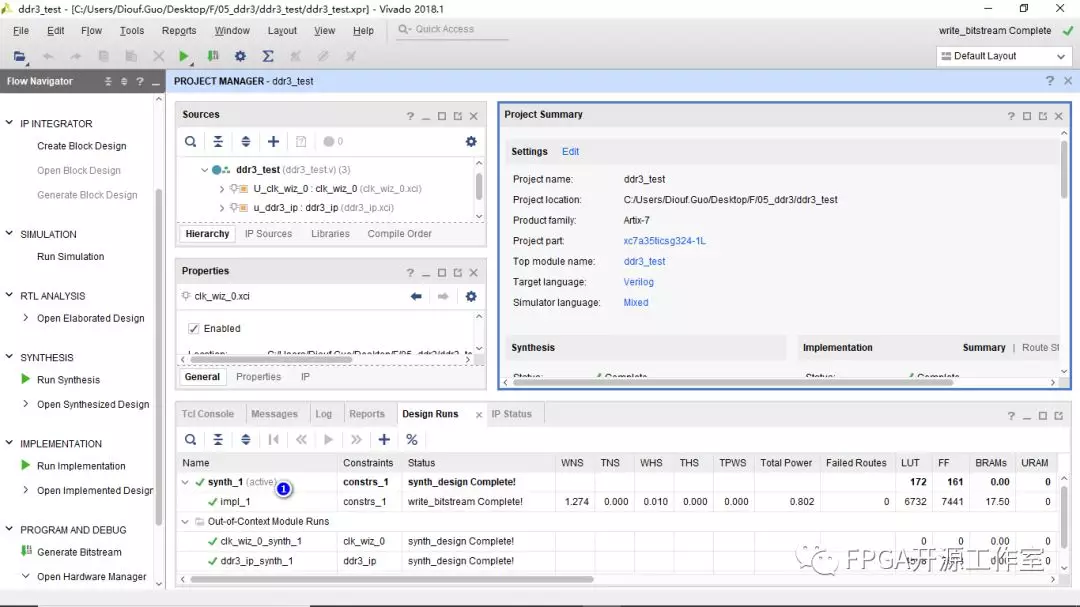

将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA

2020-12-15 16:45:16 2476

2476

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2020-12-16 15:47:59 1691

1691

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2021-01-01 10:09:00 3711

3711

2022年4月20日,中国苏州讯 —— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。 华邦的 1.35V DDR3 产品在 x8

2022-04-20 16:04:03 2554

2554

DDR31.DDR3概述DDR3内存控制器主要用于以JESD79-3C标准做SDRAM设备的外部存储接口。支持的内存类型有DDR1 SDRAM,SDRSDRAM, SBSRAM。DDR3内存控制器

2018-01-18 22:04:33

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

为了实现更强大的系统操作,DDR3 SDRAM驱动器设计通过降低电容得到了增强,动态片上端接(ODT)和新的校准方案。电容减少来自于使用新的合并驱动器。使用新驱动程序,组成输出驱动程序的电路共享用于ODT。DDR2上使用单独的结构作为输出驱动器和终端阻抗。

2019-05-23 08:20:56

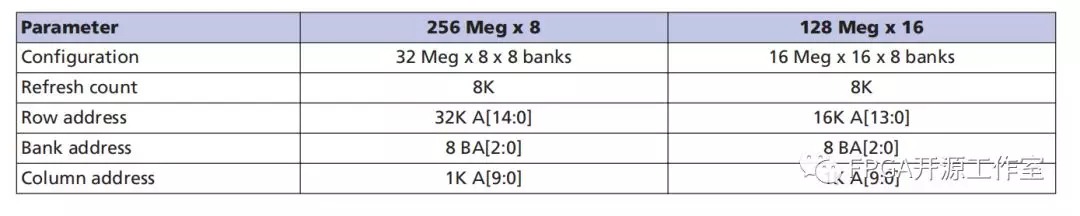

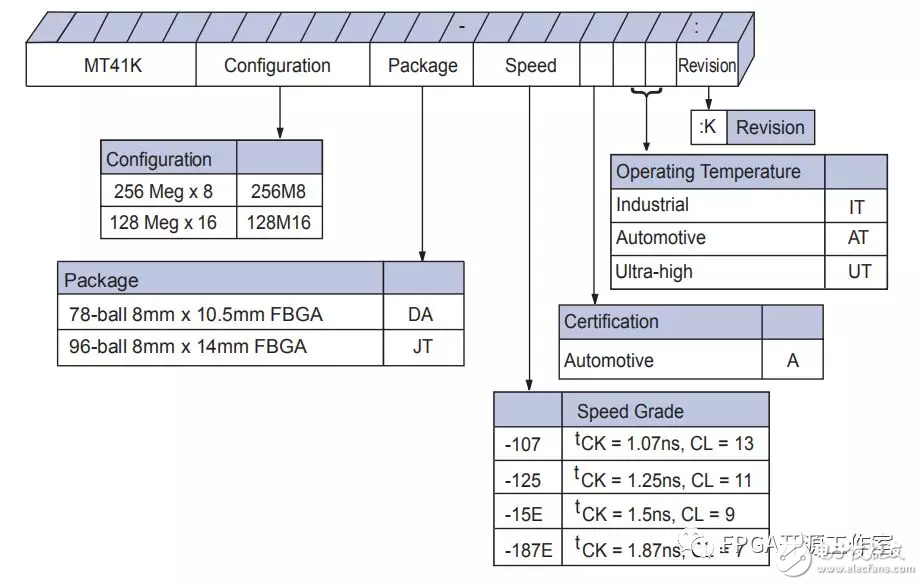

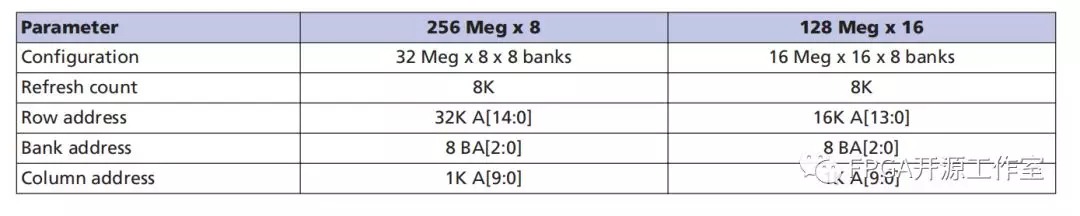

通过DDR3内存名MT41J128M16-16Meg*16*8Banks通过命名怎样算出内存的大小?

2017-06-15 21:19:11

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

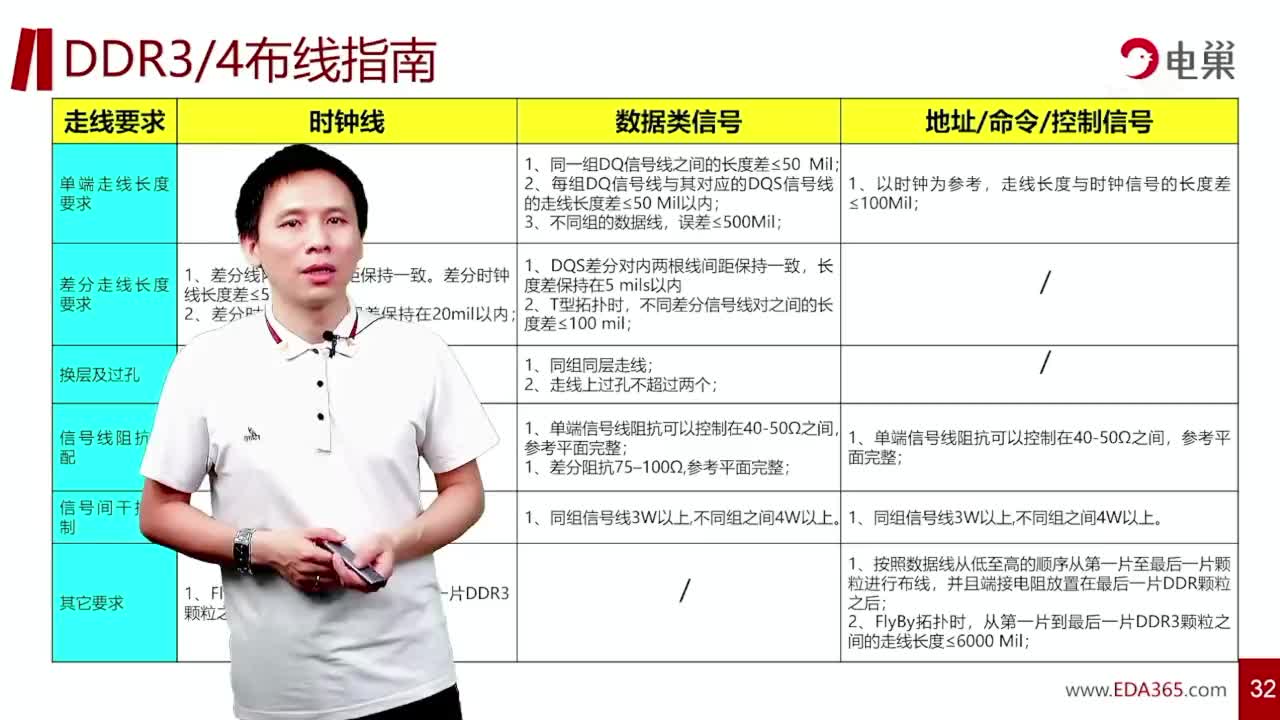

共享交流一下,DDR3布线技巧

2016-01-08 08:17:53

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 编辑

各位好!关于DDR3,之前有小结过如果进行DDR3的SW leveling和进行EMIF4寄存器的配置。但是调试时,如果进行DDR3的问题定位,现小结一下,附上相关文档。如有相关问题,可在楼下跟帖讨论。谢谢!

2018-06-21 04:01:01

附件为DDR3走线主要的规则介绍,有兴趣的朋友可以下载看看,老手就不用了~

2019-03-08 20:37:44

专家,你好,想节省代码设计的周期,请问是否可以提供6670的DDR3的驱动例子?谢谢

2018-06-21 13:34:52

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

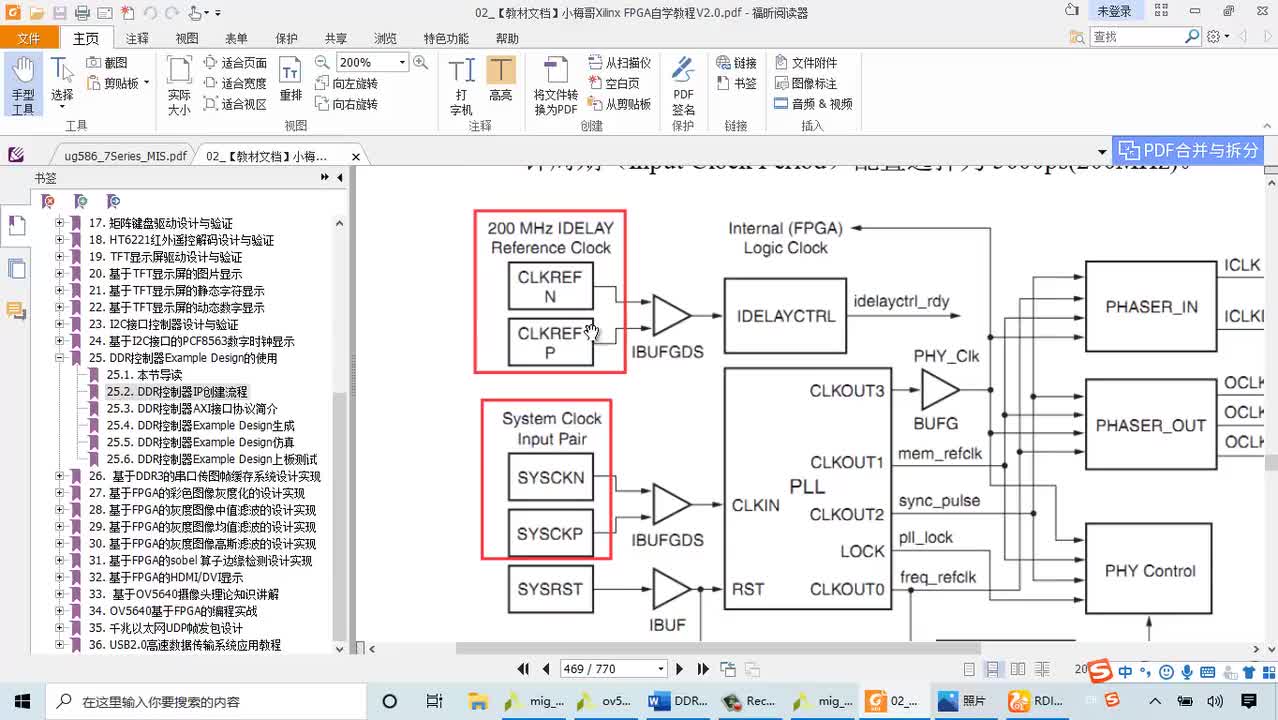

最近阿威也在玩MIG ,然后对我问了一大堆问题,主要针对MIG的时钟。后来发现自己理解得还是不够。这么一讨论更加清晰了,做个笔记吧。第一个时钟,也就是MIG 对DDR接口的时钟。因为我用的是ddr3

2019-05-21 07:21:10

你好,ISE版本为13.3,modelsim版本为10.1c 64bit.MIG工具为ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

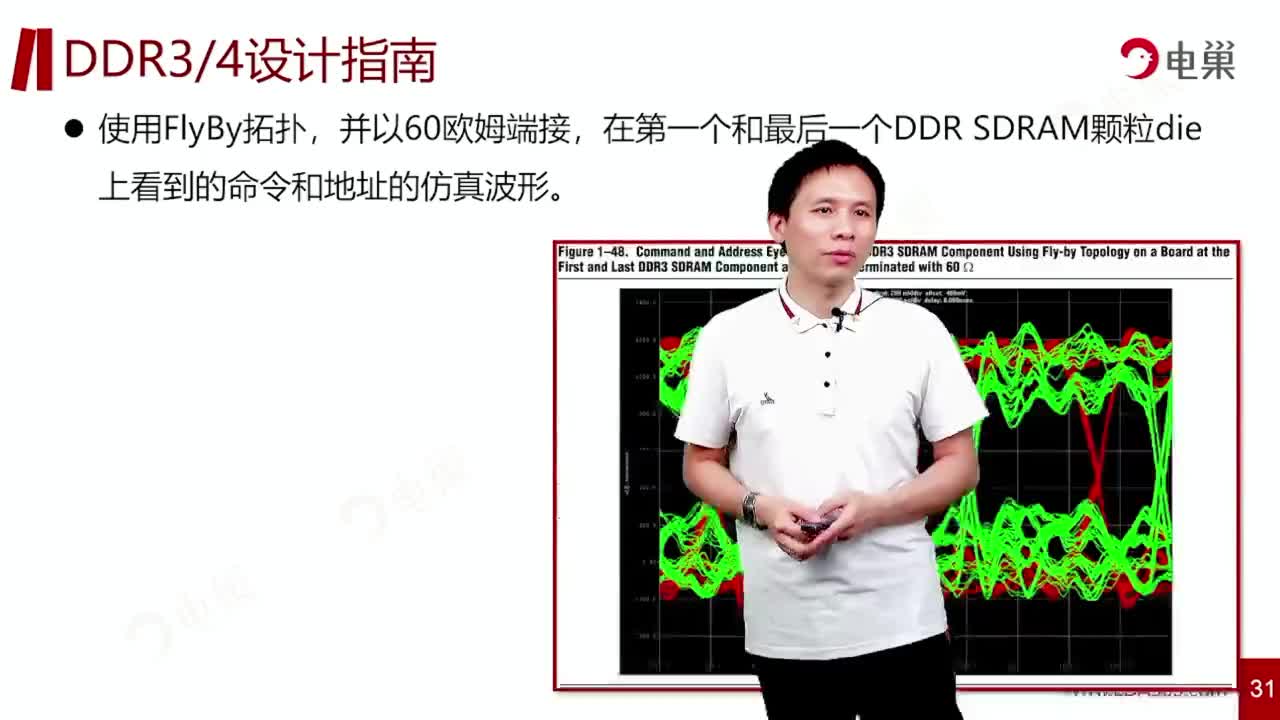

leveling应运而生,这也是为什么在DDR3里面使用fly_by结构后数据组可以不用和时钟信号去绕等长的原因,数据信号组与组之间也不用去绕等长,而在DDR2里面数据组还是需要和时钟有较宽松的等长要求

2022-12-16 17:01:46

BeagleBone的参考设计中,DDR3设计是DDR3 Device without VTT Termination。而其他的AM335X的参考设计都是有VTT Termination

2018-06-21 03:05:42

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

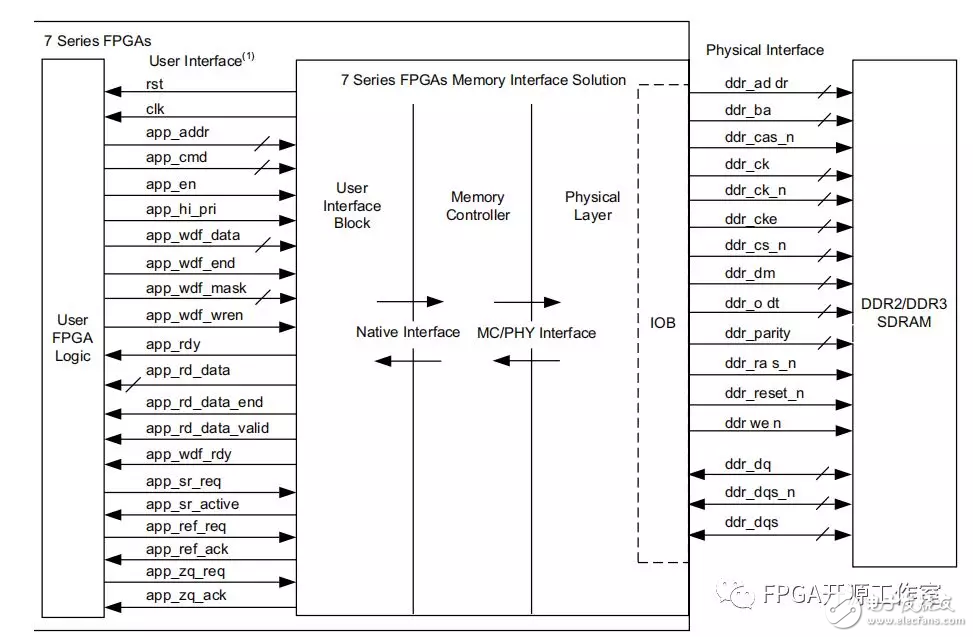

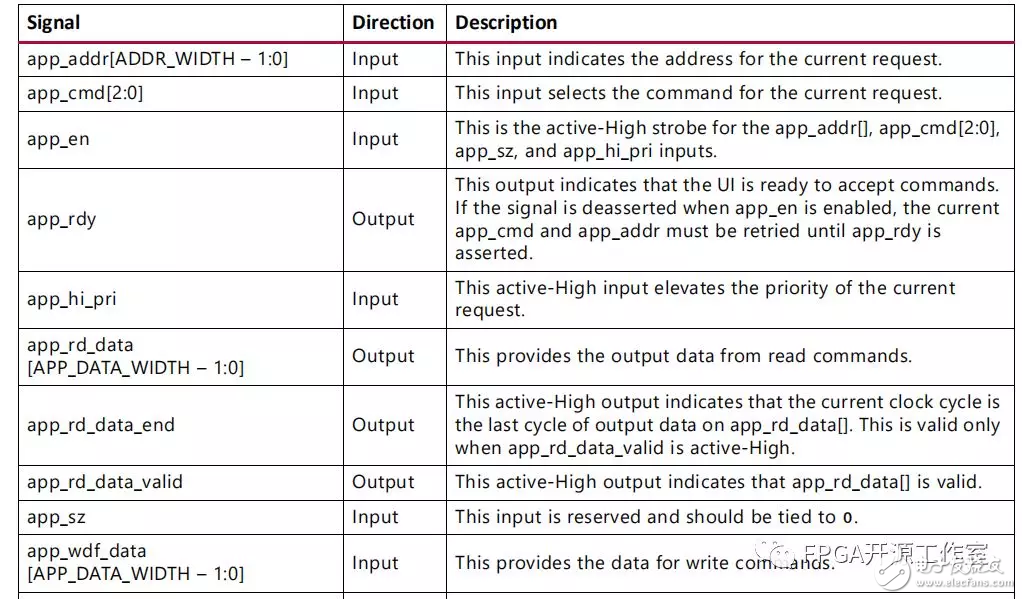

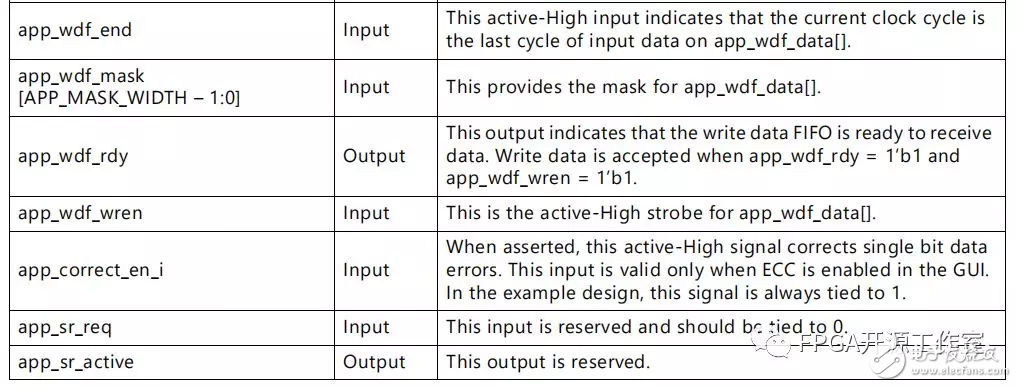

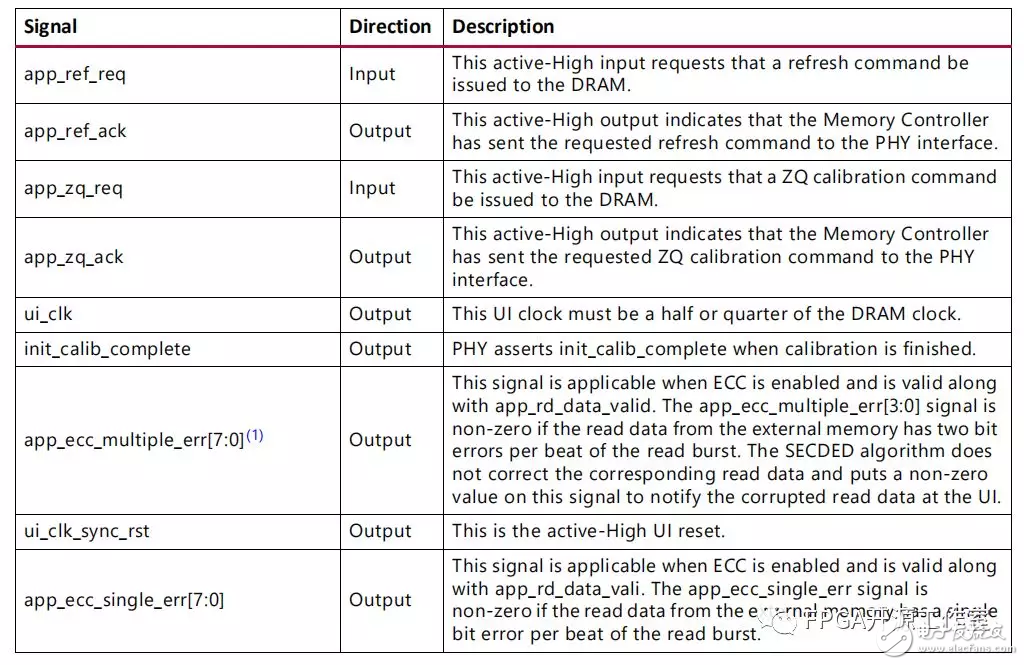

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

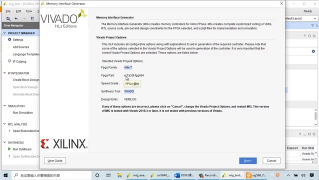

”。13.点击“Generate”生成MIG控制器。四、生成文档点击“Generate”,生成MIG控制器相关的设计文档。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置过程。

2019-12-19 14:36:01

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

看完保证你会做DDR3的仿真

2015-09-18 14:33:11

本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍Gowin中DDR3 的基础知识、DDR3的IP core的特性和使用以及DDR3的IPcore例程的仿真。课程资料包含DDR3

2021-05-06 15:34:33

IP并完成连线。3.按照下图对IP进行相应的配置。Axi Datamover 配置:mig_7_series配置:打开该IP后点击NEXT进入配置界面:选择型号之后点击NEXT,选择DDR3

2021-07-30 11:23:45

嗨,我正在设计一个定制FPGA板&我将使用带有Kintex(XC7K160T-2FFG676C)FPGA的DDR3 RAM。我阅读了xilinx& amp; amp; amp

2020-04-17 07:54:29

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

大家好, 我在使用MIG控制器实现DDR3时遇到以下错误工具:ISE 13.4设备:virtex 6警告:ParHelpers:360 - 设计未完全路由。u_ddr3

2020-04-28 08:47:27

MT41J25616XX用于DDR3芯片。当我们使用MIG工具配置DDR3时,对于我们的FPGA,此DDR3组件未显示在支持的DDR3组件列表中。如果我们使用“创建自定义部件”添加我们的芯片,那么

2019-02-18 09:01:37

我可以使用mig生成ddr控制器(xc6vlx130t)吗?mig向导只支持ddr2和ddr3!

2020-06-12 07:32:48

用DDR3获得更好的性能,DDR3的可用性可能不如DDR2,但我不想在部件选择中出错并选择一个已知的部件,并得到MIG发电机的支持在ISE。最好的祝福,埃尔维斯·道森以上来自于谷歌翻译以下为原文Hi, I

2019-05-21 06:16:43

。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配威廉希尔官方网站

对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM

2018-08-02 09:34:58

作者:吴连慧,周建江,夏伟杰摘要:为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器

2018-08-02 11:23:24

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

。 本手册以一个经过验证的可稳定工作的设计为例,来系统介绍高云FPGA连接DDR3的硬件设计方法,FPGA芯片型号采用GW2A-LV18PG256,存储芯片采用镁光(Micron)公司生产的单晶粒封装

2022-09-29 06:15:25

亲爱的先生Vivado:v2016.4装置:Artix-7我尝试在Vivado中使用MIG设计DDR3 SODIMM接口。但是,MIG只生成一对ddr_ck。我认为DDR3 SODIMM需要2对ddr_ck,如ddr_ck0和ddr_ck1。我该如何生成2对ddr_ck?谢谢。

2020-08-24 06:45:17

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

大家好,我们的定制板上焊接了定制的DDR3架构:16 x(256Mb x 8b)MT41J256M8 IC = 4GB,32b数据总线和4个等级,连接到Virtex-6设备。我们刚刚注意到

2020-06-15 06:59:58

自建Spartan6 DDR3仿真平台

2019-08-01 06:08:47

我正在使用vivado 2014.3,MIG 7 ddr3 verilog IP,内存时钟400MHz,用户时钟200 MHz,ddr数据宽度64位,AXI数据宽度128位。在我的系统中,我们有微型

2020-08-05 13:45:44

大家好 我的问题是DDR3校准完成失败。调试结果:dbg_wrcal_err = 1,通过波形,我们可以看到写入模式不匹配。 我的问题是MIG IP Core配置中是否有任何参数可以调整它?或者我

2020-07-23 10:09:37

嗨,任何1可以帮我写一个代码,用于连接DDR3 SDRAM内存和Virtex6 fpga。实际上我有一个小疑问,通过MIG我可以为此生成代码。如果不是如何继续这个我对这个PLZ帮助我。谢谢以上

2019-02-15 06:36:48

嗨,我正在尝试用我的设计生成带有MIG3.2的DDR3控制器,并修改example_design项目以适应我的电路板。在更改.ucf文件之前,实现成功。但在改变.ucfaccording我的设计后

2020-06-10 08:25:16

怎样对DDR3芯片进行读写控制呢?如何对DDR3芯片进行调试?

2021-08-12 06:26:33

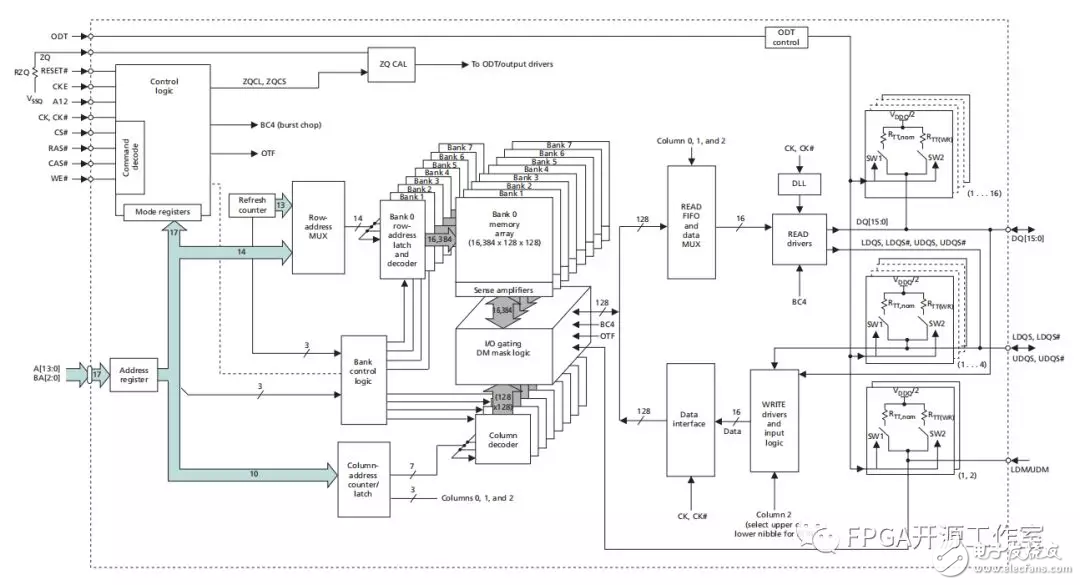

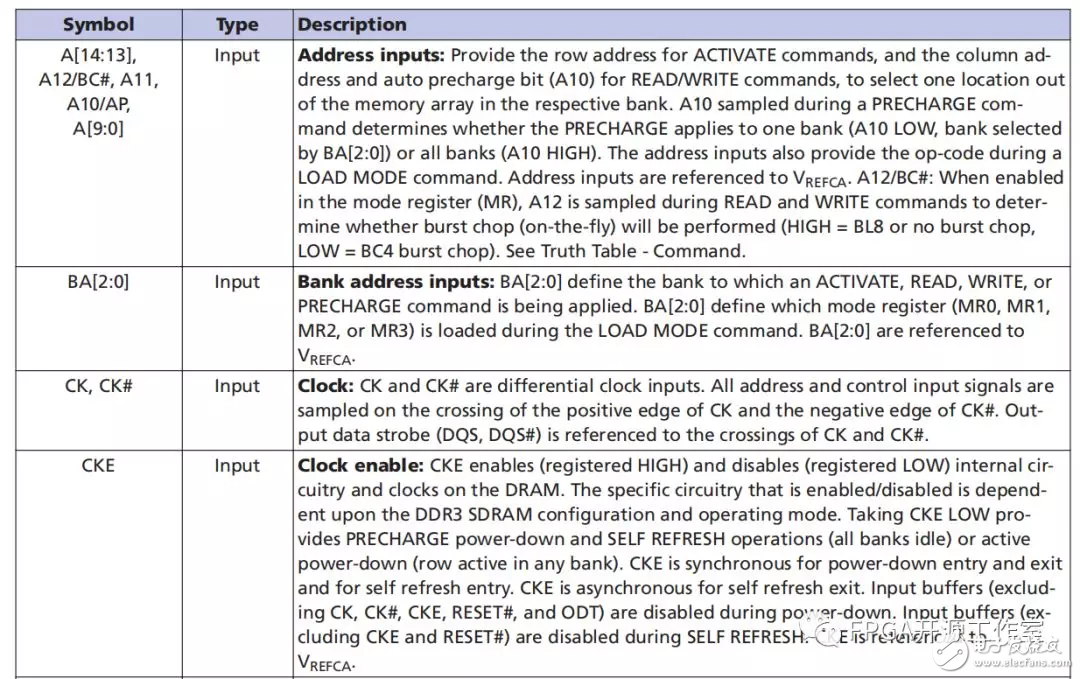

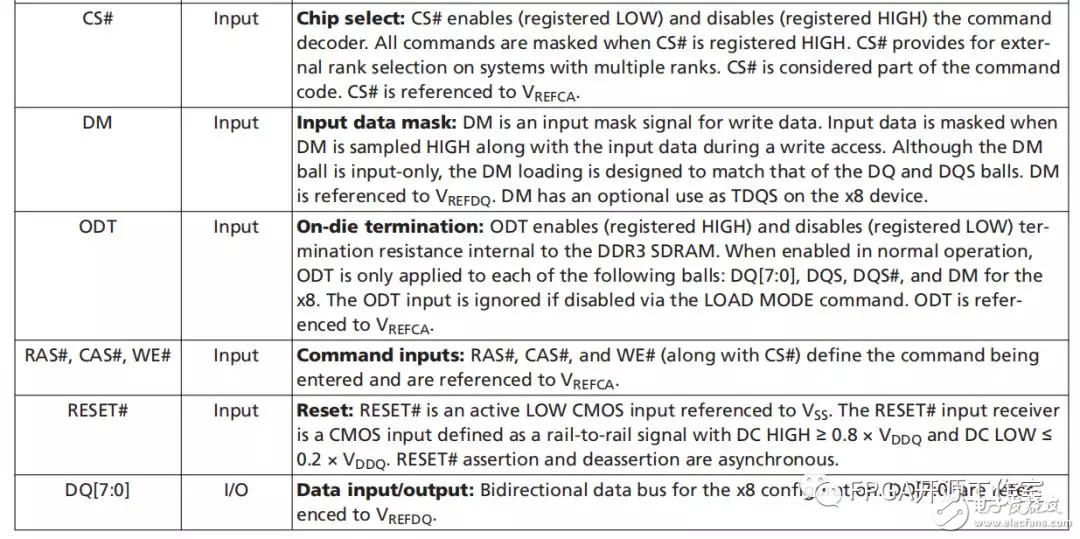

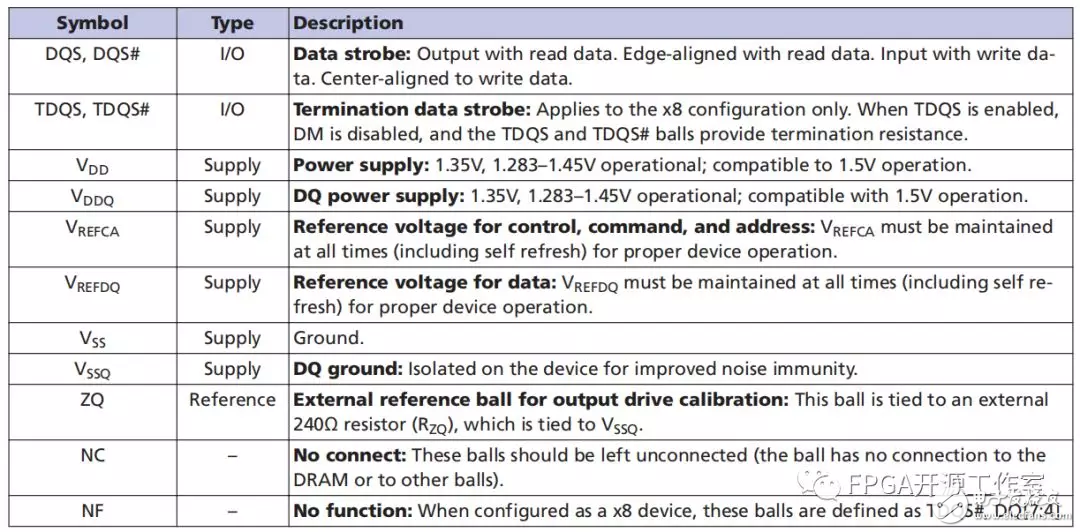

各位大神好,小弟在设计的FPGA模块中需要加入一个DDR3作为缓存,但是不是特别了解DDR3的输入输出信号(包括信号类型、位宽以及功能),哪位大神对这个比较了解,最好能分享下相关资料,谢谢了,急用!!!!!!

2014-10-21 17:46:09

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 编辑

各位专家好!刚刚学习DSP,还没有入门。实验室购买了TMS320C6678开发板。请问:1、为什么DSP需要外接DDR3?2

2018-06-20 00:40:57

我需要在V7中实现与DDR3 SDRAM相同的功能和接口。这意味着命令/地址,读取数据和写入数据流的方向与MIG的方向不同。这可以实现吗?

2020-07-14 16:18:04

喜 我需要支持ml605板的2G内存,我在用2G DDR3更换512M DDR3后遇到了一些问题..它没有用。我使用ise13.3我通过核心生成器生成mig,当我生成核心时,我应该做什么谢谢。

2020-06-14 14:59:33

DDR3的系统时钟?如何在MIG工具中使用NO BUFFER?clcok资源能实现这一目标吗?我已经尝试了,但它失败了。我注意到它在数据表中说系统时钟必须与mig相同,它是否重要?我很想知道如何将这个MRCC引入MMCM,PLL或BUFGDS,或其他类似的东西。谢谢。

2020-07-22 07:43:59

/Trenz_Electronic/TE0630_series/TE0630/documents/UM-TE0630.pdf)在这个主板上有Nanya的DDR3内存(NT5CB64M16DP)。对于

2019-08-05 08:08:14

你好,有没有人使用过Digilent的Atlys主板?热衷于了解获得的DDR b / w以及适合使用该内存的MIG设置。目前还没有参考设计干杯,马尼什

2019-10-16 01:28:47

DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 8454

8454

虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 30895

30895 为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 19504

19504

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取

2017-11-17 14:26:43 24265

24265

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 6412

6412

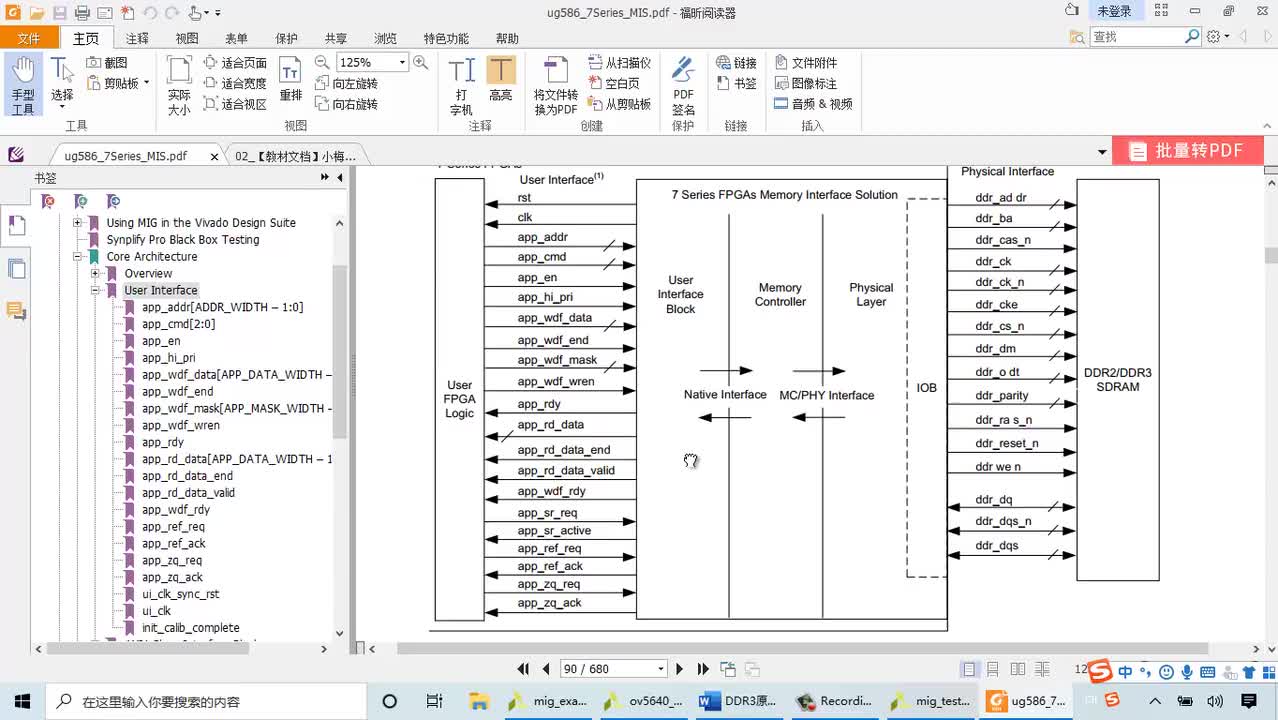

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11:53 5640

5640

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 从成本的角度来看,DDR3也许的确要比DDR4低一些,所以从这个角度可以讲通。

2020-09-08 16:28:23 4062

4062 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2021-05-02 09:05:00 2979

2979

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28:58 1241

1241 一、DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据

2022-12-21 18:30:05 1915

1915 复制Vivado工程路径vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夹。粘贴到仿真路径testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夹)下。

2023-08-12 11:08:27 735

735 本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1896

1896

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 743

743

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 517

517

是目前使用最为广泛的计算机内存标准,它已经服务了计算机用户多年。但是,DDR4内存随着威廉希尔官方网站

的进步,成为了更好的内存选择。本文将详细介绍DDR4和DDR3内存的各种区别。 1. 工作频率 DDR3内存的标准工作频率为1600MHz,而DDR4内存标准则为2133MHz。这意味着DDR4内存的传输速度

2023-10-30 09:22:00 3900

3900

电子发烧友App

电子发烧友App

评论