静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期

2020-11-25 11:03:09 8918

8918

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 使用SDC命令create_clock创建时钟,时钟周期20,占空比50%的时钟信号;

2022-11-08 09:12:02 5409

5409 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

特权老师,您好,关于时序分析-寻找PLL相移值,有些问题想请教您:疑问一:在您的《特权和你一起学NIOS II》书中,第五章,5.4 三部曲-时序报告,5.4.1 寻找PLL相移值,第102页,书中

2013-10-22 22:26:12

前言小梅哥FPGA时序分析和约束实例演练FPGA的基本原理FPGA基本结构Field-Programmable Gate Array现场-可编程 门 阵列现场可编程通过JTAG、AS、PS等方式

2021-07-26 07:52:42

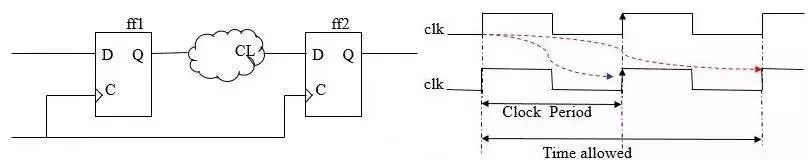

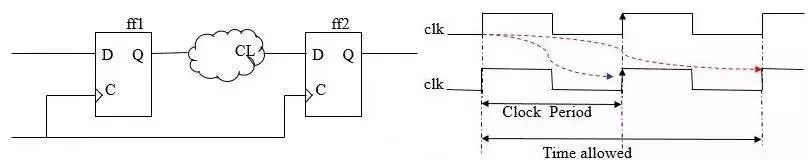

1。时序分析就是分析前级的数据是否在后一个时钟沿的数据有效窗口里面,就是说在整个窗口内部,数据都应该保持有效,如果不满足时间窗的前端,就是setup违例,如果不满足时间窗的后端,那么就是hold违例

2014-12-29 14:53:00

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

不需要确定时序,不进行分析的路径。set_false_path -from [get_port reset] -to[all_register] set_false_path -from

2018-09-21 12:55:34

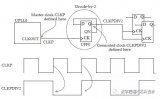

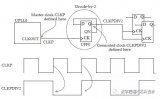

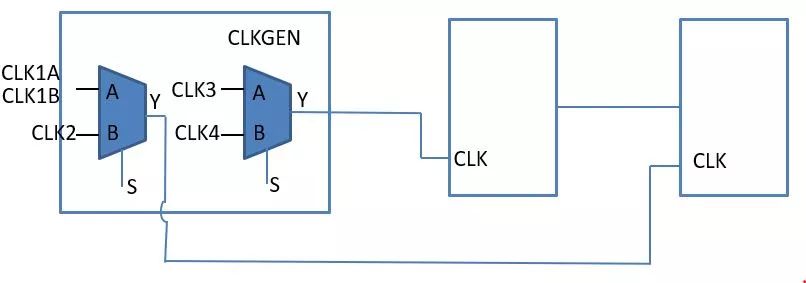

vivado默认计算所有时钟之间的路径,通过set_clock_groups命令可禁止在所标识的时钟组之间以及一个时钟组内的时钟进行时序分析。 1.异步时钟组约束声明两时钟组之间为异步关系,之间不进行时序

2018-09-21 12:40:56

这种时序图第一次见,不会分析。1.希望威廉希尔官方网站

支持或者哪位大神从编程的角度分析一下这个时序。2.上面的线为什么是曲线,代表什么意思?3.CLK正负的产生源可否是由DSP的引脚产生,经反相器,通过电容,形成两路互补的信号?附件图像 1.png35.7 KB

2018-12-03 09:15:27

DAC时序分析

2021-07-29 09:14:26

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

知道“时间分析器”和“planahead”可以帮助我,但我无法理解它的报告。我该怎么做才能解决时间问题。我找不到一些材料来帮助我理解“时序分析”,“代码风格”,“如何纠正时间问题” ','时序收敛'等等

2019-03-18 13:37:27

时序约束的目的是:规范设计的时序行为,表达设计者所期望满足的时序条件,指导综合和布局布线阶段的优化算法等,作用:提高系统设计的fmax、得到正确的时序分析报告 1. 系统的最高频率FmaxFmax

2018-07-03 02:11:23

时序约束的目的是:规范设计的时序行为,表达设计者所期望满足的时序条件,指导综合和布局布线阶段的优化算法等,作用:提高系统设计的fmax、得到正确的时序分析报告 1. 系统的最高频率FmaxFmax

2018-07-09 09:16:13

/1pJ5bCtt 下面我们来添加时序约束,打开TimeQuest,点击菜单栏的ContraintsàCreat Clock,做如图8.54所示的设置,首先约束CMOS Sensor的同步时钟VCLK

2015-08-18 21:24:30

(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。3.Clock Setup Time (Tsu) 建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立

2012-01-11 11:43:06

:set_input_delay -clock [get_clocks clkin_adc_a] -max 0.3 [get_ports {datain_adc_a_p }] set

2020-08-06 06:07:05

您好,我正在使用最新的A.09.90.05固件。查看“编程”部分下的帮助文件,在'SENSe:MIXer:'树下,他们有命令设置RF输入功率(即'INPut:POWer)和LO功率(即'LO

2019-01-07 16:03:10

嗨,我在N6700B主机中使用了两个模块(N6762A和N6784A)。我知道查询正常(设定或编程)输出电压的命令,但我正在寻找查询电源端子实际输出电压的命令。在远程使用时,电源输出将略大于编程电压

2018-12-06 15:56:24

约束文件(XDC文件),它包含用于时序分析的“create_clock”和“set_input_jitter”约束。在ISE 14.7和Spartan-3 FPGA中,我可以使用称为“时钟向导”的IP来

2019-08-02 09:54:40

某些时钟是异步的命令:set_clock_groups -name async_ADC_ETH -asynchronous \ -group [get_clocks

2018-11-05 11:31:53

会影响到对 Tsu 的分析,也会影响到对Thold的分析。因此,采用set_clock_uncertainty的参数要多一些。如果要理解这个命令对系统时序分析的影响,就需要对 Altera的延时计算的概念

2012-03-05 15:02:22

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

我只有非常有限的知识来使用tcl命令进行时序分析(不用于时序约束,仅用于时序分析)。这些命令如下:check_timingreport_timing_summary我希望知道一些最常见的tcl命令来

2019-03-11 13:41:27

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-27 06:34:40

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-27 00:00:41

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。在QuartusII的一个培训

2017-06-26 23:54:23

本帖最后由 630183258 于 2017-9-27 10:11 编辑

一、TLC549时序分析1、TLC549管脚图2、时序图3、时序分析(1)nCS拉低后需要延时1.4us,然后发送发送

2017-09-27 10:04:22

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

为什么静态时序分析受组件(符号)名称的影响?我在示意图中有一个ISR,当我把它称为“CuttIsIr”时,静态时序分析返回一个警告“设置时间违反”,但是当我称之为“UTHISISR”时,一切都

2019-07-30 10:42:26

就是基于时序进行分析的,而绝大多数的时序路径的计算又都是以时钟为基础的。所谓时钟定义是指对于设计中所用到的时钟设定名称、周期、相位、占空比。在Primetime中用如下命令来实现

2018-08-28 11:58:31

当我实现我的设计时,它会报告警告“没有找到set_false_path约束的有效对象,带有选项'-from [get_clock userclk1]'”。但我可以使用TB“get_clocks

2018-11-06 11:29:25

挑战。本文主要介绍了逻辑设计中值得注意的重要时序问题,以及如何克服这些问题。最后介绍了利用Astro工具进行时序分析的方法。关键词:ASIC;同步数字电路;时序;Astro引言 随着系统时钟频率的提高

2012-11-09 19:04:35

器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合

2018-04-03 11:19:08

请教如何做时序分析

2013-06-01 22:45:04

新手,求教怎么根据spi时序编程,最好有例子,这是我的时序,真心求教

2016-01-11 16:45:31

了时钟,也可以使用set_input_transition命令来约束。Clock Uncertainty可以使用set_clock_uncertainty约束来指定时钟周期的timing

2023-04-20 16:17:54

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 时序约束与时序分析 ppt教程

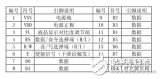

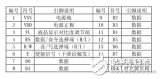

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 使用时钟PLL的源同步系统时序分析一)回顾源同步时序计算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 _静态时序分析(Static_Timing_Analysis)基础及应用[1]。

2016-05-09 10:59:26 31

31 基于时序路径的FPGA时序分析威廉希尔官方网站

研究_周珊

2017-01-03 17:41:58 2

2 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 在进行时序分析时片上工艺差别通常会导致严重的“时钟悲观效应”。这种问题可以通过CPR(Clock Pessimism Reduction)操作来恢复.然而经常有用户咨询我们说在他们的设计中CPR操作

2017-02-07 18:04:11 1357

1357 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子威廉希尔官方网站

中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 09:39:25 86341

86341

I2C总线的结构、工作时序和模拟编程

2017-10-24 14:34:20 13

13 如何看懂芯片的时序图,进行编程设计是单片机对外接芯片进行操作的基础。本文以1602为例,解析单片机对芯片时序图的编程思路。

2018-01-06 10:13:01 10501

10501

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

2018-04-03 15:56:16 10

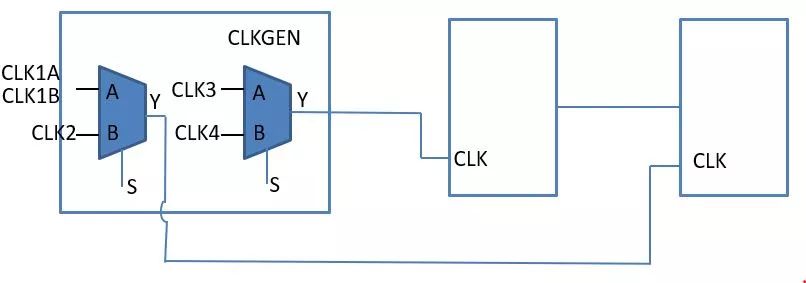

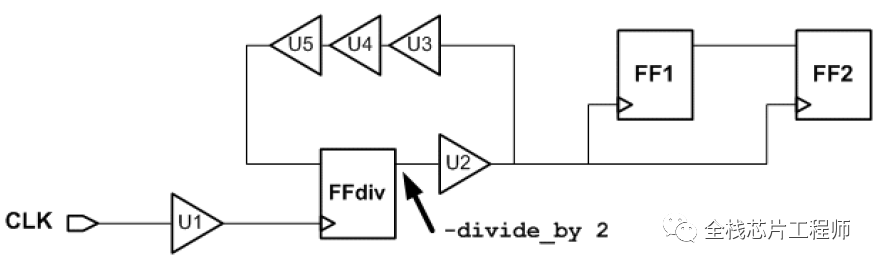

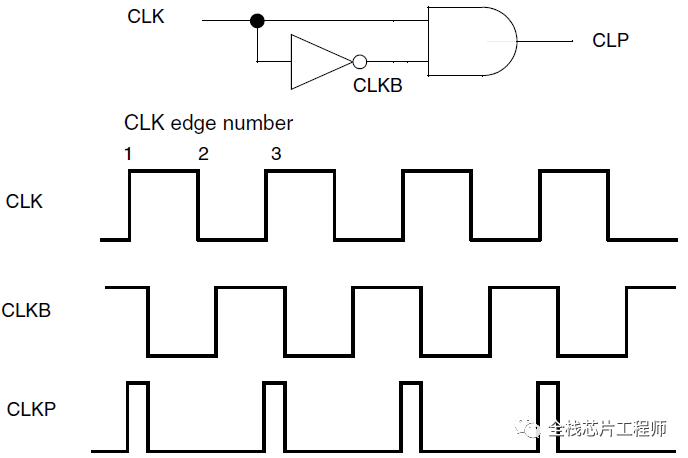

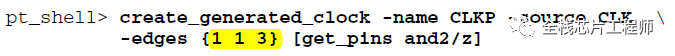

10 今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念。

2018-09-24 08:12:00 7990

7990

如果时钟同时驱动I/O和Slice中的逻辑资源,且负载小于2000时,可通过CLOCK_LOW_FANOUT属性对相应的时钟net进行设置,最终可使工具将该时钟驱动的所有负载放置在同一个时钟域内。通过命令report_clock_utilization生成的报告可查看每个时钟的负载,如下图所示。

2018-11-07 11:08:44 4333

4333

了解report_design_analysis,这是一个新的Vivado报告命令,可以独特地了解时序和复杂性特征,这些特性对于分析时序收敛问题很有价值。

2018-11-26 07:01:00 3313

3313 FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 1894

1894

静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和威廉希尔官方网站

,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

停止条件即示波器停止“统计分析”的条件,当测试条件满足预设条件时,时序分析软件会停止统计完成分析工作。

2020-04-29 15:18:52 2425

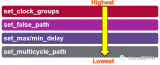

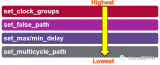

2425 XDC描述的时序约束是有优先级的,尤其是涉及到时序例外的约束,如set_clock_groups、set_false_path、set_max_delay和set_multicycle_path。如果这些约束施加到同一条路径上,那么其优先级如下图所示。

2020-09-07 10:53:49 8944

8944

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 当我们开始精通编程语言时,我们不仅希望实现最终的编程目标,而且还希望可以使我们的程序更高效。在本文中,我们将学习一些 Ipython 的命令,这些命令可以帮助我们对 Python 代码进行时间分析

2020-11-25 10:43:00 10

10 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 3

3 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 15

15 Clock shew是数字集成电路设计中一个重要的因素。本文比较了在同步电路设计中0clock shew和非0clock shew时钟分布对电路性能的影响,分析了通过调整时钟树中CLOCK SKEW来改善电路性能的方法,从而说明非0clock shew时钟分布是如何提高同步电路运行的最大时钟频率的。

2021-01-14 16:26:52 21

21 基本正确 器件时序, 约束采用的是其中的 tframe = 1.3 - 1.9ns 约束: set_input_delay -clock [get_clocks rxDco_p] -clock

2021-04-10 09:43:02 1556

1556

关于objects1、分类2、包括六类:Design、clock、port、net(模块与模块之间的互连线)、cell(例化的模块)、pin(cell里面的引脚)3、design可以转换为cell4

2021-11-09 20:51:07 2

2 今天我们要介绍的时序分析基本概念是collection。代表的是一个集合,类似指针。在数字后端工具中,我们可以通过命令get_*来寻找想要的Object。这些get_*命令返回的就是collection。不同类型的object对应不同的get命令。

2021-11-26 10:30:18 3272

3272 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 有一说一,我之前还真不知道set命令这么好用,还傻呵呵地自己写函数做脚本阶段性判断,判断上一条命令是否有问题,有问题就直接退出脚本。

2022-11-25 09:10:32 290

290 这个命令指定clock之间是异步关系,时序分析时会完全ignore这些clock之间的path。

2022-12-12 09:49:11 1723

1723 使用SDC命令create_clock创建时钟,时钟周期20,占空比50%的时钟信号

2023-06-18 09:42:13 2273

2273

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

今天我们要介绍的时序分析基本概念是 **clock group,简称时钟组。** 定义完时钟后,我们也需要通过设置clock group来确认各个时钟之间的关系。

2023-07-03 14:37:27 716

716

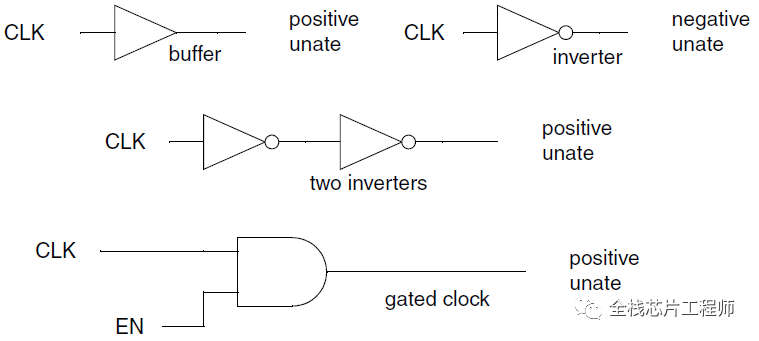

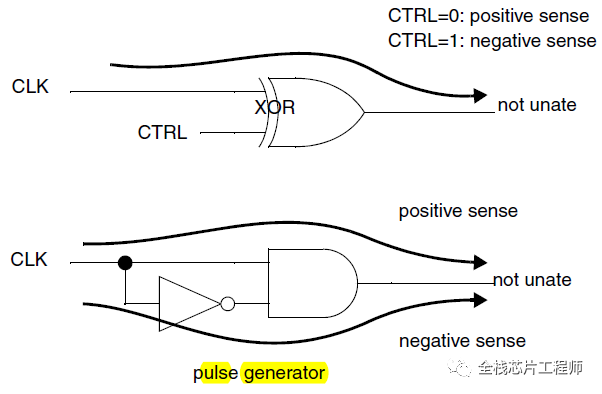

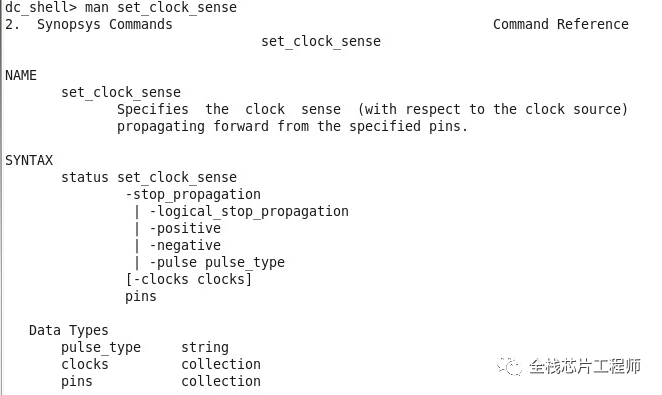

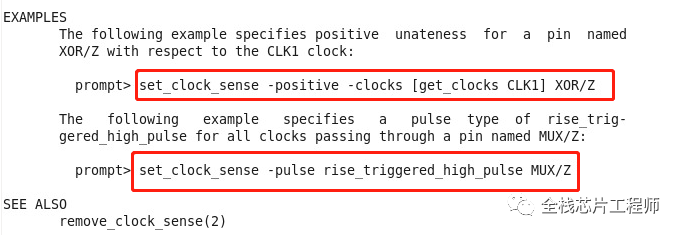

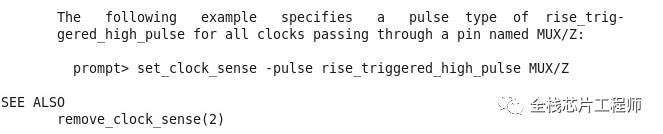

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。

2023-07-03 15:06:03 1484

1484

今天我们要介绍的基本sdc是 **时序特例** ,也就是我们常说的Path exception。针对一些路径需要的一些特殊设定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

2023-07-03 15:34:52 471

471

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们会给data path,clock path上设定单一的timing derate值。

2023-07-03 16:29:05 1164

1164

本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 528

528

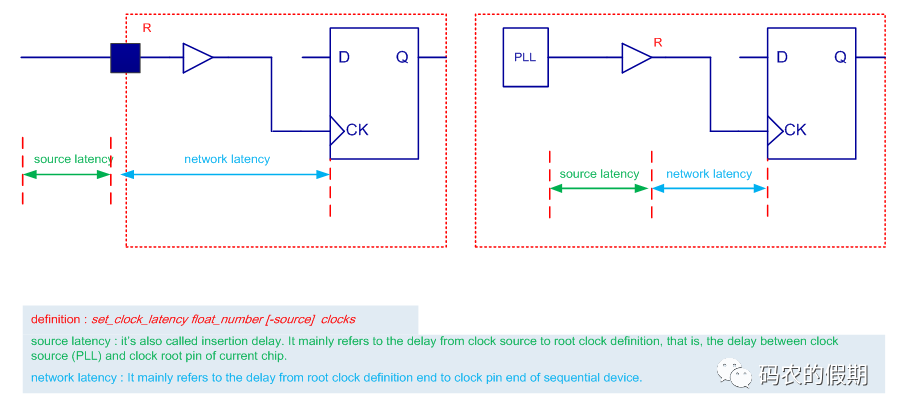

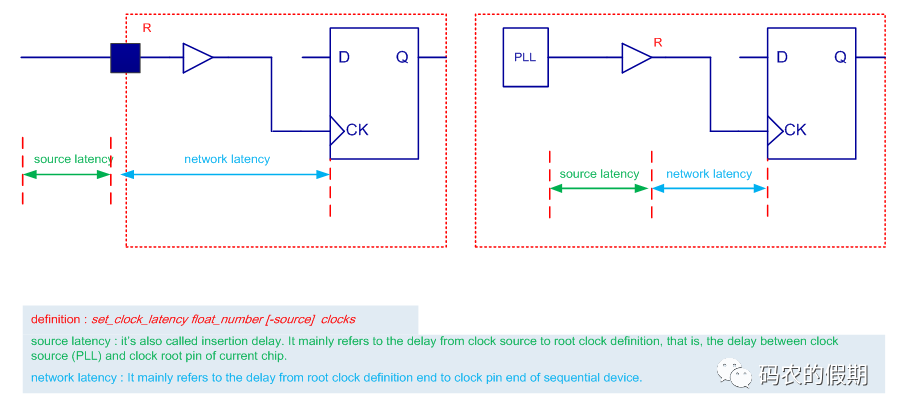

今天要介绍的时序分析基本概念是Latency, 时钟传播延迟。主要指从Clock源到时序组件Clock输入端的延迟时间。

2023-07-04 15:37:08 1311

1311

今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念。

2023-07-06 10:34:18 1234

1234

要探讨今天的主题,首先需要跟大家一起学习下clock latency这个基本概念。Clock latency通俗意义上是指clock定义点到clock sink point(时序器件的clock

2023-07-06 15:34:44 1644

1644

今天我们介绍的时序分析基本概念是Virtual Clock,中文名称是虚拟时钟。

2023-07-07 16:52:55 744

744

今天我们要介绍的时序分析命令是uncertainty,简称时钟不确定性。

2023-07-07 17:23:46 1796

1796

在本篇博文中,我们来聊聊“RQS_CLOCK-12”时钟设置建议以及它如何帮助达成时序收敛。

2023-07-26 09:53:50 384

384

Linux命令和Shell编程之间存在密切的联系。 首先,Shell是Linux命令行下的解释器,它提供了一个用户界面,使用户能够与Linux内核进行交互。Shell解释器可以解释和执行用户输入

2023-11-08 10:53:26 359

359

电子发烧友App

电子发烧友App

评论