一、反向器

反相器是可以将输入信号的相位反转180度,这种电路应用在interwetten与威廉的赔率体系 电路,比如说音频放大,时钟振荡器等。在电子线路设计中,经常要用到反相器。随着微电子威廉希尔官方网站 与工艺的不断发展和创新,以计算机为代表的各类数字电子产品应用越来越广泛,与此同时也面临着更加复杂的电磁环境。CMOS 反相器是几乎所有数字集成电路设计的核心,它具有较大的噪声容限、极高的输入电阻、极低的静态功耗以及对噪声和干扰不敏感等优点,因此广泛应用于数字集成电路中。

HPM可以通过缝隙、孔洞以及外露连接线缆等“后门”途径,耦合进入电子系统内部,影响系统内器件的正常工作,CMOS 反相器作为构成数字集成电路最基础的功能单元和数字电子系统中最为典型的器件,极易受 HPM“后门”耦合作用的影响,进而产生干扰、扰乱或直接损伤效应。

另外,CMOS 反相器有明确的逻辑功能,HPM 或者其它类型的强电磁脉冲对其产生的扰乱效应相比于对其它器件来讲更加明显。因此,研究数字集成电路或者数字电子系统的 HPM 效应,可以从 CMOS 反相器的HPM 效应研究入手。已有研究指出 HPM 可以引起 CMOS 反相器的闩锁(latch-up)效应,进而导致扰乱效应,Kim等人对CMOS反相器的HPM效应进行了大量的实验研究,得到了一些重要结论,比如,当HPM频率较高时其引发的CMOS反相器扰乱效应将会被抑制等,CMOS 反相器在 HPM 作用下会发生门锁效应并导致功能扰乱,但是一段时间后其功能可能会恢复正常,HPM 引起 CMOS 反相器闩锁效应的能量阈值特性。

这些报道多数都是 HPM 效应实验的结果描述和规律统计,而针对具体效应与规律进行机理分析和微观解释的研究则相对较少。

组成结构:

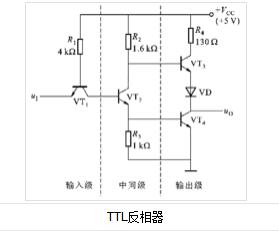

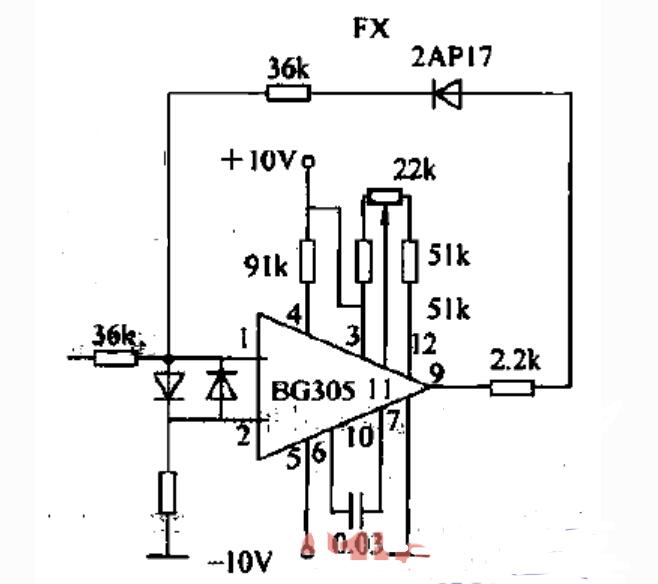

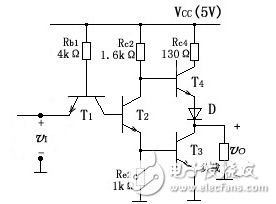

典型TTL与非门电路电路组成

输入级——晶体管T1和电阻Rb1构成。

中间级——晶体管T2和电阻Rc2、Re2构成。

输出级——晶体管T3、T4、D和电阻Rc4构成,推拉式结构,在正常工作时,T4和T3总是一个截止,另一个饱和。

工作原理:

当输入Vi=3.6V(高电平)

Vb1=3.6+0.7=4.3V 足以使T1(bc结)T2(be结)T3 (be结)同时导通, 一但导通Vb1=0.7+0.7+0.7=2.1V(固定值),此时V1发射结必截止(倒置放大状态)。

Vc2=Vces+Vbe2=0.2+0.7=0.9V 不足以T3和D同时导通,反相器T4和D均截止。

V0=0.2V (低电平)

当输入Vi=0.2V(低电平)

Vb1=0.2+0.7=0.9V不 足以使T1(bc结)T2(be结)T3 (be结)同时导通,T2 T3均截止, 同时Vcc---Rc2----T4---D---负载形成通路,T4和D均导通。

V0=Vcc-VRc2(可略)-Vbe4-VD=5-0.7-0.7 =3.6(高电平)

结论:输入高,输出低;输入低,输出高(非逻辑)

反相器的种类

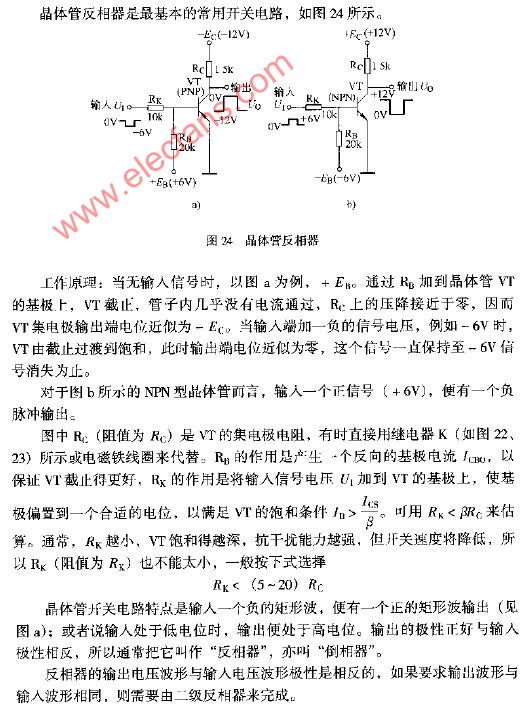

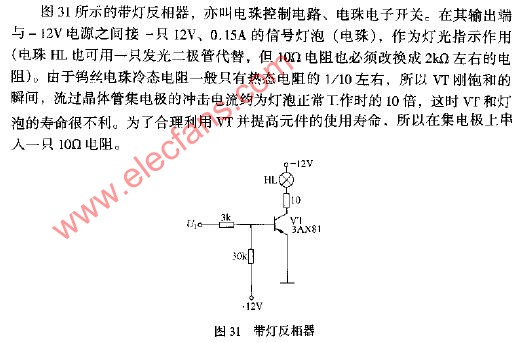

1、TTL非门

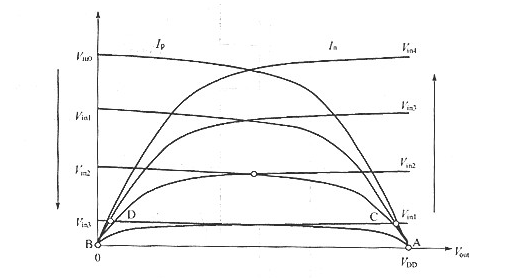

典型TTL与非门电路电路组成:输入级——晶体管T1和电阻Rb1构成。中间级——晶体管T2和电阻Rc2、Re2构成。输出级——晶体管T3、T4、D和电阻Rc4构成,推拉式结构,在正常工作时,T4和T3总是一个截止,另一个饱和。当输入Vi=3.6V(高电平)Vb1=3.6+0.7=4.3V 足以使T1(bc结)T2(be结)T3 (be结)同时导通, 一但导通Vb1=0.7+0.7+0.7=2.1V(固定值),此时V1发射结必截止(倒置放大状态)。Vc2=Vces+Vbe2=0.2+0.7=0.9V 不足以T3和D同时导通,T4和D均截止。V0=0.2V (低电平)当输入Vi=0.2V(低电平)Vb1=0.2+0.7=0.9V不 足以使T1(bc结)T2(be结)T3 (be结)同时导通,T2 T3均截止, 同时Vcc---Rc2----T4---D---负载形成通路,T4和D均导通。V0=Vcc-VRc2(可略)-Vbe4-VD=5-0.7-0.7 =3.6(高电平)结论:输入高,输出低;输入低,输出高(非逻辑)。TTL优势:工作速度快 、带负载能力强 、传输特性好。TTL反相器的电压传输特性:电压传输特性是指输出电压跟随输入电压变化的关系曲线,即UO=f(uI)函数关系。如图2.3.2所示曲线大致分为四段:AB段(截止区):当UI≤0.6V时,T1工作在深饱和状态,Uces1《0.1V,Vbe2《0.7V,故T2、 T3截止,D、T4均导通, 输出高电平UOH=3.6V。TTL反相器的电压传输特性 BC段(线性区):当0.6V≤UI《1.3V时,0.7V≤Vb2《1.4V,T2开始导通,T3尚未导通。此时T2处于放大状态,其集电极电压Vc2随着UI的增加而下降,使输出电压UO也下降 。CD段(转折区):1.3V≤UI《1.4V,当UI略大于1.3V时, T2 T3均导通, T3进入饱和状态,输出电压UO迅速下降。DE段(饱和区):当UI≥1.4V时,随着UI增加 T1进入倒置工作状态,D截止,T4截止,T2、T3饱和,因而输出低电平UOL=0.3V。

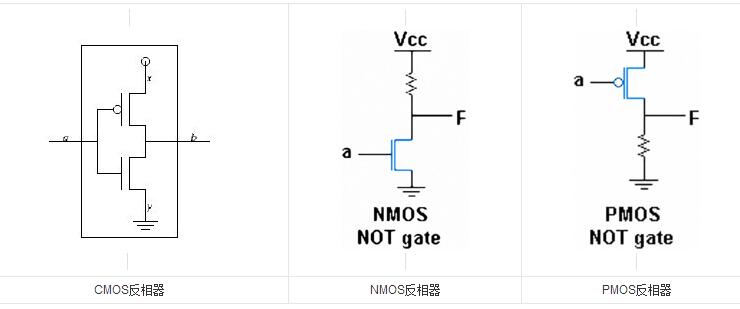

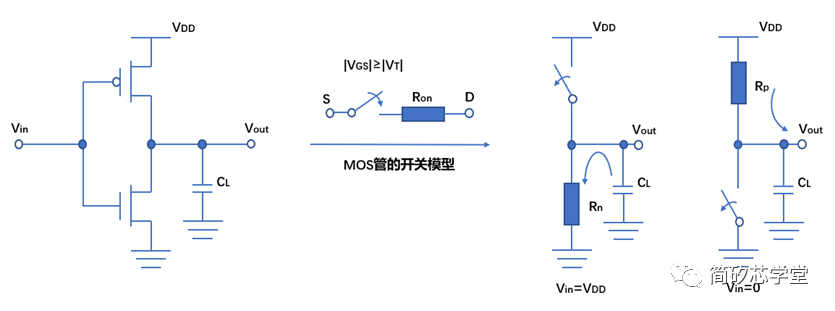

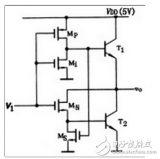

2、CMOS反相器

CMOS反相器电路由两个增强型MOS场效应管组成,其中V1为NMOS管,称驱动管,V2为PMOS管,称负载管。 NMOS管的栅源开启电压UTN为正值,PMOS管的栅源开启电压是负值,其数值范围在2~5V之间。为了使电路能正常工作,要求电源电压UDD》(UTN+|UTP|)。UDD可在3~18V之间工作,其适用范围较宽。工作原理:当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|》|UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD, 即输出为高电平。当UI=UIH=UDD时,UGS1=UDD》UTN,V1导通,而UGS2=0《|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。 可见,CMOS反相器实现了逻辑非的功能。CMOS反相器的主要特性:在AB段由于V1截止,阻抗很高,所以流过V1和V2的漏电流几乎为0。 在CD段V2截止,阻抗很高,所以流过V1和V2的漏电流也几乎为0。只有在BC段,V1和V2均导通时才有电流iD流过V1和V2,并且在UI=1/2UDD附近,iD最大。

3、HPM 扰乱效应

基于 CMOS 反相器仿真模型,研究了温度变化对反相器 HPM 扰乱效应的影响。研究表明,反相器所处环境温度越高对 HPM 越敏感,这一结论得到了实验数据的验证,同时又扩充了实验数据所适用的温度范围。研究认为,衬底电阻增大是环境温度升高时反相器 HPM 扰乱效应敏感性增加的主要原因。仿真得到了 HPM 引起的反相器门锁延时特性,通过对温度分布影响的分析,论文指出闩锁延时特性与热边界条件密切相关,器件内部平均温度持续上升导致闩锁效应的大电流通路阻抗增大,从而使得闩锁效应难以继续维持,这一结论为文献中报道的闩锁延时特性提供了微观解释CMOS 反相器的 HPM 扰乱效应机理出发,建立了考虑 HPM 脉宽效应和频率影响的扰乱效应阈值解析模型,并利用仿真结果和实验数据对解析模型进行了验证。研究认为,HPM 导致的过剩载流子注入主导晶体管的电流放大过程,对扰乱效应至关重要。HPM 扰乱脉宽效应可以用反相器寄生晶体管基区过剩载流子随时间的累积效应来解释;而 HPM 频率对扰乱效应的影响则是由于 HPM 频率较高时器件内部交变电场变化太快以致于载流子无法响应,从而影响了 p 型衬底中的注入电荷总量和过剩载流子浓度分布。利用解析模型研究了结构参数 LB对扰乱效应的影响,结果表明 LB较小的 CMOS 反相器对 HPM 更敏感。

反相器的应用

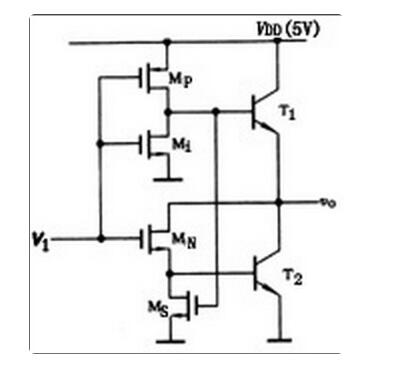

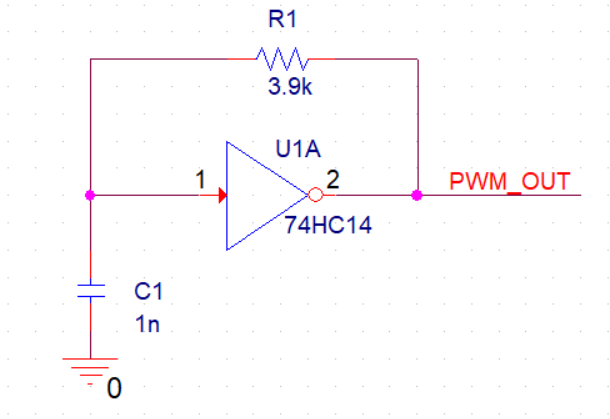

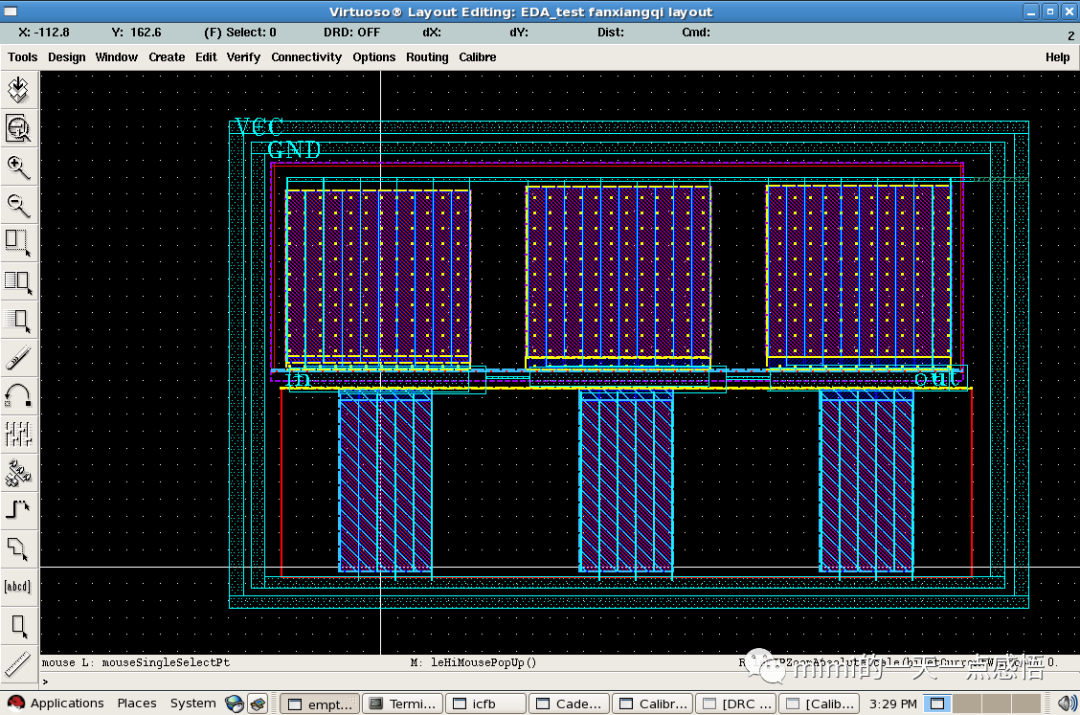

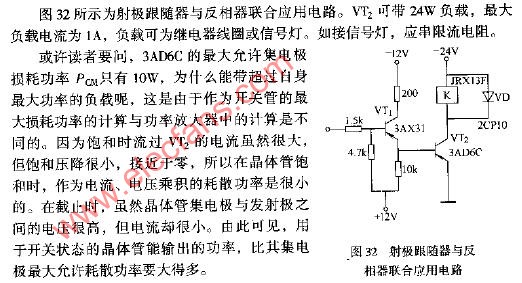

CMOS 反相器凭借其互补结构所具备的优势成为于数字电路设计中应用最广泛的一种器件。CMOS 反相器是由 n-MOSFET 与 p-MOSFET 组成的互补推拉式结构,n-MOSFET 作为驱动管(下拉管),p-MOSFET 作为负载管(上拉管)。包含 p-n-p-n 寄生结构的 CMOS 基本结构示意图,两个晶体管的栅极连接在一起,作为信号输入端;两个晶体管的衬底分别与它们的源极连接在一起,n-MOSFET 的源极接地 GND,p-MOSFET 的源极接电源电压 Vdd;n-MOSFET 与 p-MOSFET 的漏极连接在一起作为反相器的输出端。为了在集成电路中制造 n-MOSFET 和 p-MOSFET,必须形成绝缘的 p 衬底区和 n 衬底区,因此,CMOS 集成电路中具有 n 阱、p 阱和双阱这三种工艺,本文针对 n 阱工艺下 CMOS 反相器进行研究,即在重掺杂的 p 型衬底硅上先生长一层轻掺杂 p 型外延层,然后通过 n 阱扩散工艺形成 n 阱,之后再制作场氧化层和栅氧化层,利用杂质注入的方式形成源漏区和高掺杂扩散区,最后淀积和刻蚀出金属化电极并对器件表面进行一定程度的钝化保护。如图所示,这种情况下CMOS 结构内部会形成寄生的 n-p-n 双极型晶体管 Q1 和 p-n-p 双极型晶体管 Q2,Rsub和 Rwell代表 p 型衬底电阻和 n 阱电阻。在实际应用时,CMOS 反相器电路可能还会包含诸如静电放电(electrostatic discharge, ESD)保护电路、闩锁防护电路以及输入施密特整形电路等其它附属电路。

目前关于 HPM 效应的实验主要有两种方法,即辐照法和注入法。辐照法是指 HPM 以空间电磁波方式对目标电子系统进行辐照,得到的是电子系统的 HPM 效应阈值。辐照法主要针对电子系统,能够比较真实地模拟实际应用环境中电子系统的 HPM 电磁辐射环境,是获取电子系统整机 HPM 效应阈值的最有效手段;但是这种方法也存在缺点,为了较为真实地模拟实际情况,实验要求较高:微波波束需要覆盖整个目标电子系统,并且照射强度均匀,这就要求微波源辐射天线与效应物之间的距离不能太小,但是通常实验需要在特定的微波暗室中进行,实验空间有限,难以满足辐照均匀的要求。另外,辐照实验从 HPM 源到电子系统内部元器件须经过电磁传输和耦合等复杂过程,不利于对电子系统 HPM 效应机理进行分析。注入法是指 HPM 以传导方式注入目标效应物的敏感端口,观测其瞬态响应。注入法主要针对单元电路或器件,更适合于 HPM 效应规律、效应机理及敏感环节研究。注入法相对于辐照法更容易实现,对实验环境的要求相对较低,可以在普通实验室完成,主要需要解决两个问题:一是减小注入通道的微波驻波系数,提高微波注入效率,使更多的微波功率进入目标电路或器件;二是要做好微波源和效应目标之间的隔离,避免相互影响和破坏,目前主要隔离措施有衰减、高通/低通滤波和隔离等。

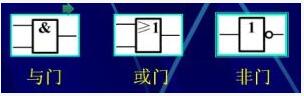

二、非门

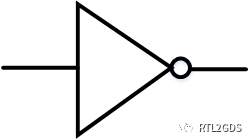

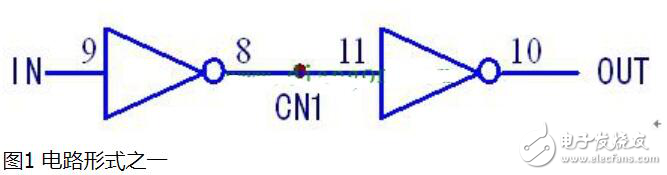

非门(英文:NOT gate)又称非电路、反相器、倒相器、逻辑否定电路,简称非门,是逻辑电路的基本单元。非门有一个输入和一个输出端。当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。也就是说,输入端和输出端的电平状态总是反相的。非门的逻辑功能相当于逻辑代数中的非,电路功能相当于反相,这种运算亦称非运算。

非门又称反相器,是逻辑电路的重要基本单元,非门有输入和输出两个端,电路符号见附图,其输出端的圆圈代表反相的意思,当其输入端为高电平时输出端为低电平,当其输入端为低电平时输出端为高电平,也就是输入端和输出端总是反相的。

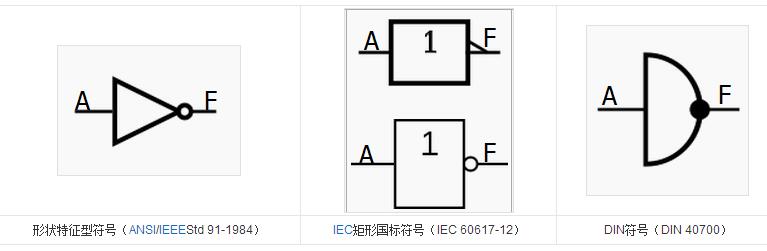

逻辑符号

非门共有3种逻辑符号:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)和DIN符号(DIN 40700),分别如下图所示:

实现

非门(反相器)通常采用CMOS逻辑和TTL逻辑,也可以通过NMOS逻辑、PMOS逻辑等来实现。

CMOS逻辑:

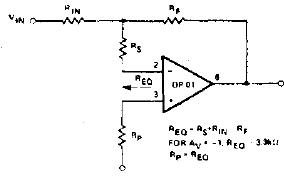

两管的栅极相连作为输入端,两管的漏极相连作为输出端。TN的源极接地,TP的源极接电源。为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD》UTN+ |UTP|。当Ui=0V时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。因此实现了逻辑非的功能。

TTL逻辑:

TTL反相器由三部分组成,包括输入级、倒相级、输出级组成[3] 。由于输入和输出均为三极管结构,因此也成为三极管-三极管逻辑电路。其结构如图所示。

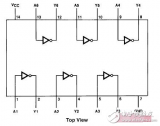

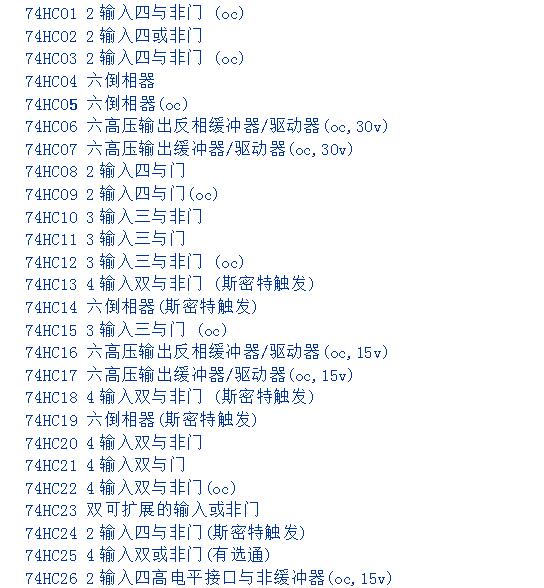

集成电路

非门是基本的逻辑门,因此在TTL和CMOS集成电路中都是可以使用的。标准的集成电路有74X04和CD4049。74X04TTL芯片有14个引脚,4049CMOS芯片有16个引脚,两种芯片都各有2个引脚用于电源供电/基准电压,12个引脚用于6个反相器的输入和输出(4049有2个引脚悬空)。

在数字电路中最具代表性的CMOS非门集成电路是CD4069。

三、反相器和非门有什么区别

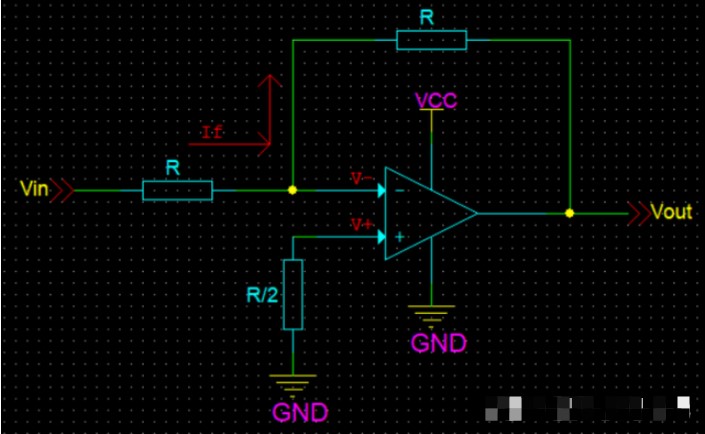

反相器是可以将输入信号的相位反转180度,这种电路应用在摸拟电路,比如说音频放大,时钟振荡器等。

非门是将输入端的高低电平翻转,输入的电平与输出电平相反,这种电路是应用在数字电路上。

电子发烧友App

电子发烧友App

评论