半加器

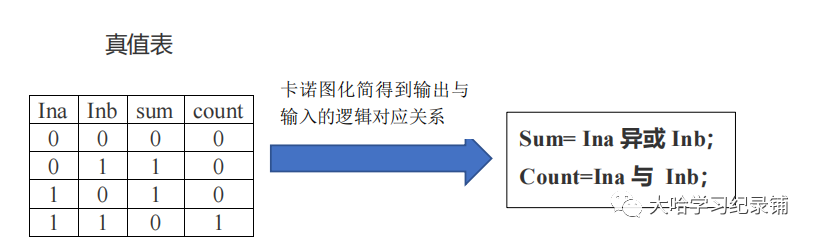

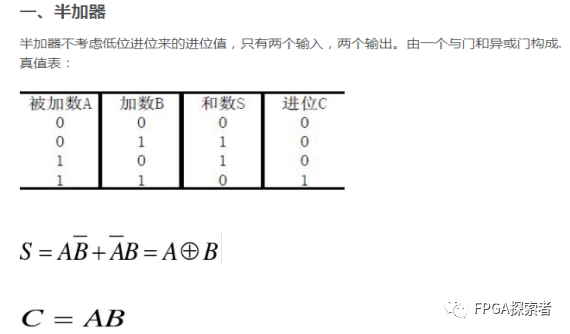

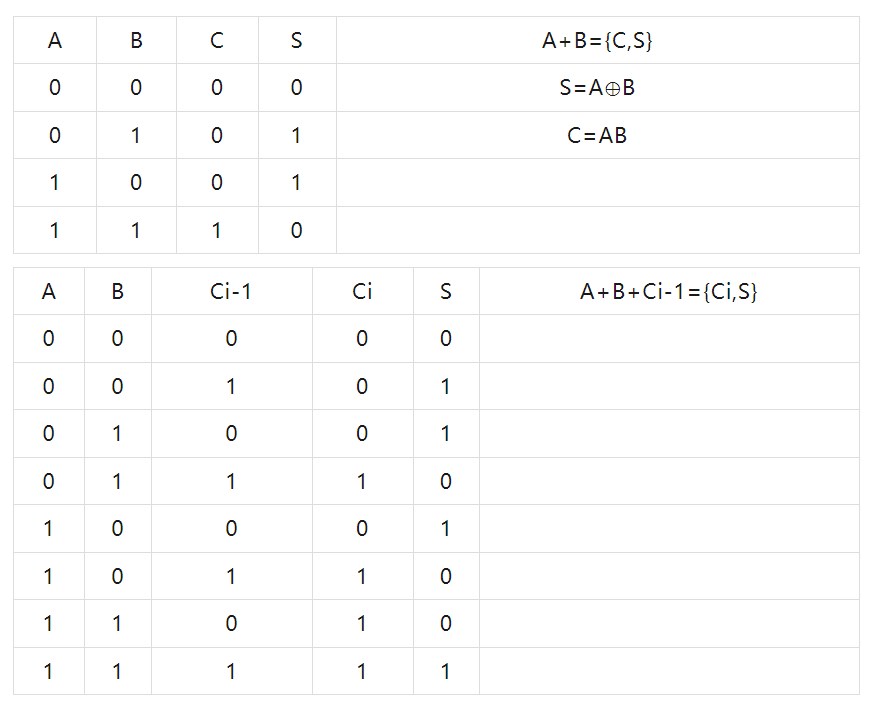

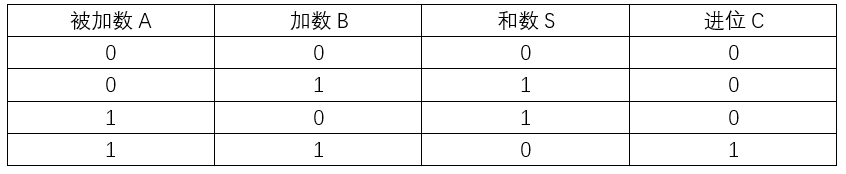

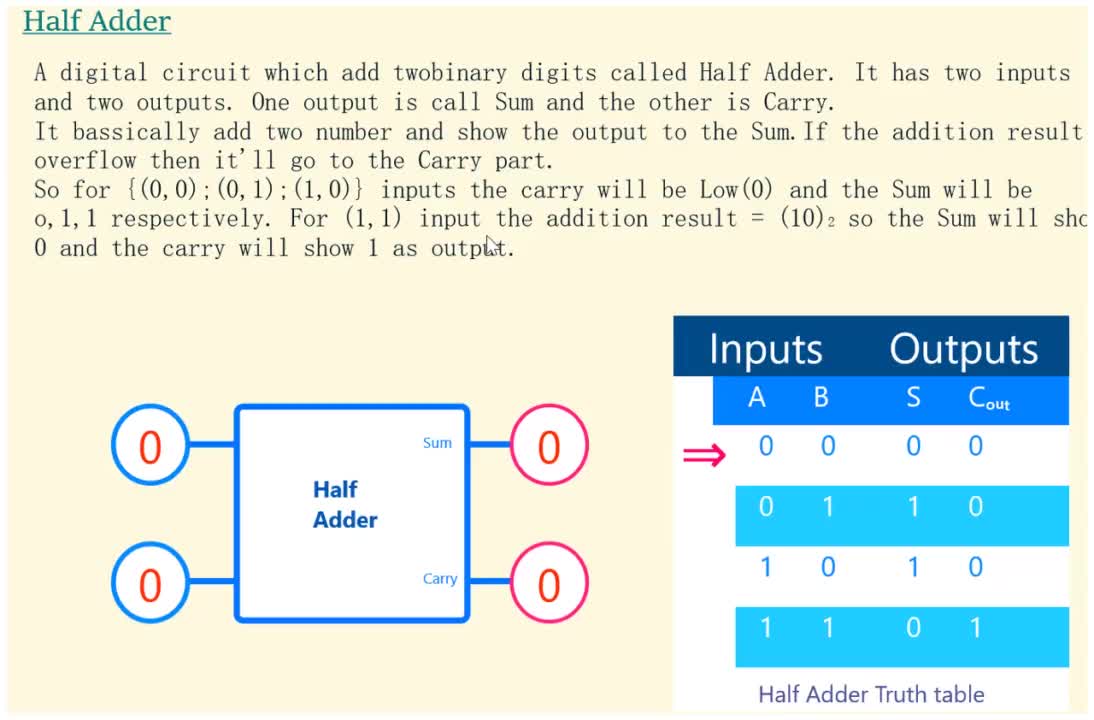

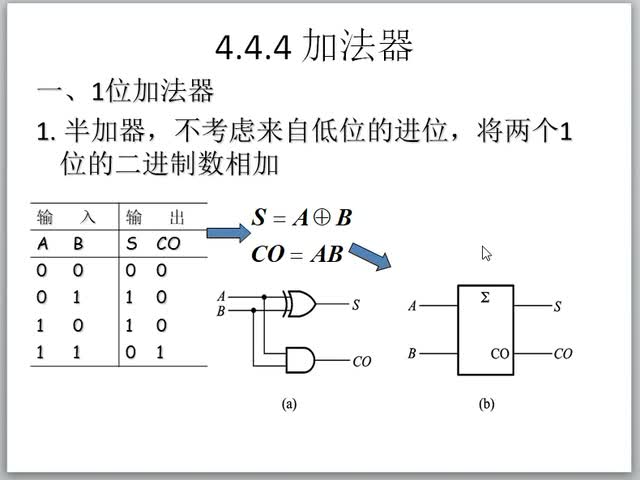

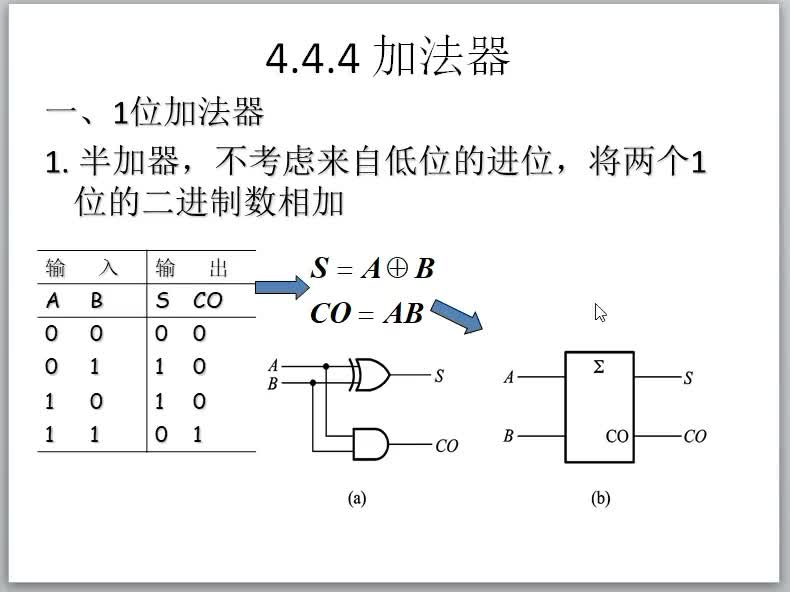

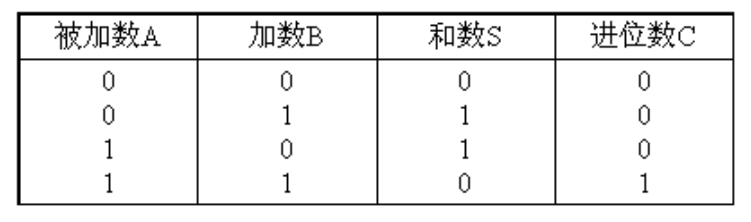

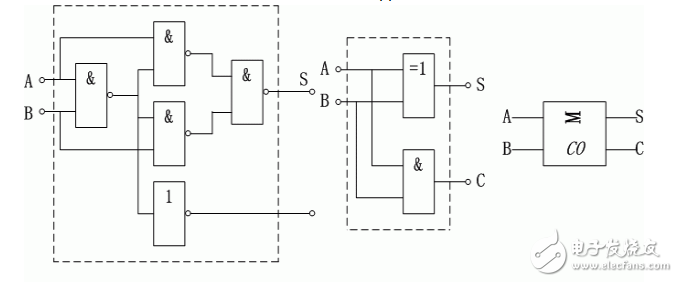

半加器和全加器是算术运算电路中的基本单元,它们是完成1位二进制数相加的一种组合逻辑电路。两个1二进制的加法运算如下表所示,其中S表示和数C表示进位数。由表中逻辑关系可见,这种加法运算只考虑了两个加数本身,而没有考虑由低位来的进位,所以称为半加。半加器就是实现下面这个真值表关系的电路。

半加器和全加器是算术运算电路中的基本单元,它们是完成1位二进制数相加的一种组合逻辑电路。两个1二进制的加法运算如下表所示,其中S表示和数C表示进位数。由表中逻辑关系可见,这种加法运算只考虑了两个加数本身,而没有考虑由低位来的进位,所以称为半加。半加器就是实现下面这个真值表关系的电路。

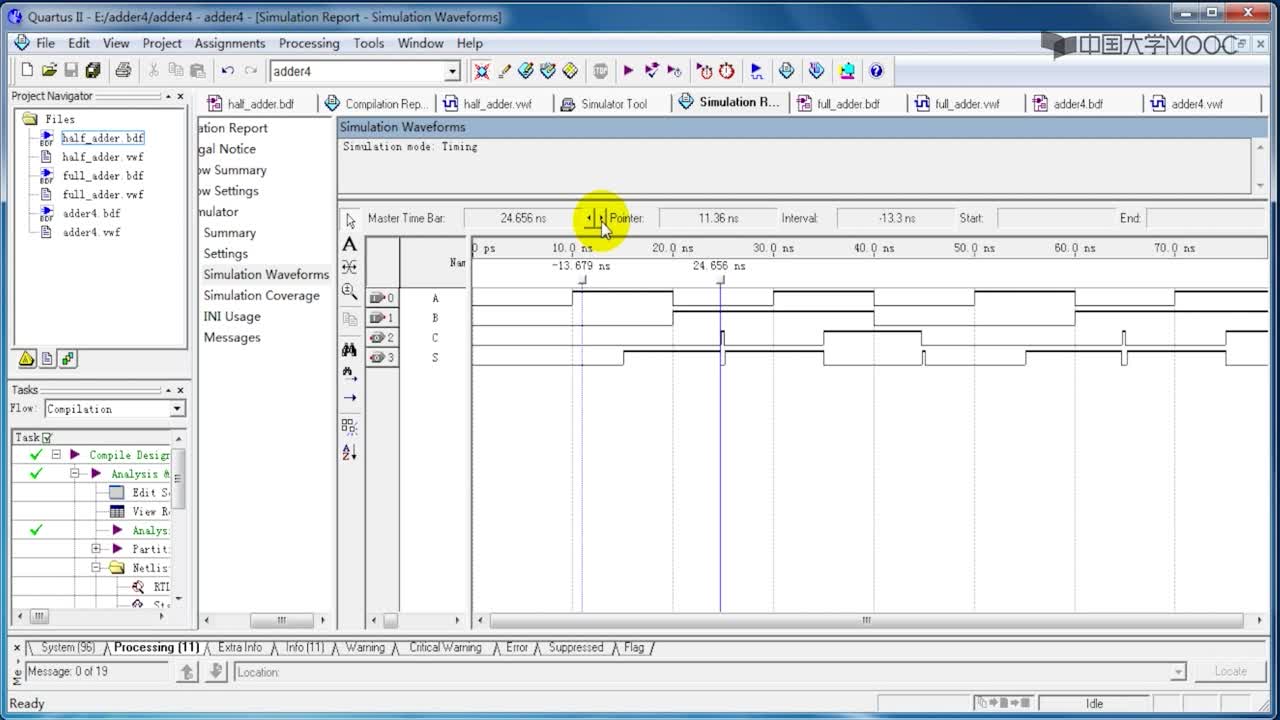

由真值表可得逻辑表达式

运用逻辑代数,可将上式变换成与非形式

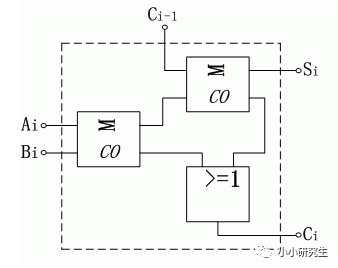

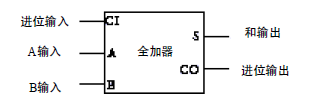

根据这两个表达式可得由与非门组成的半加器:

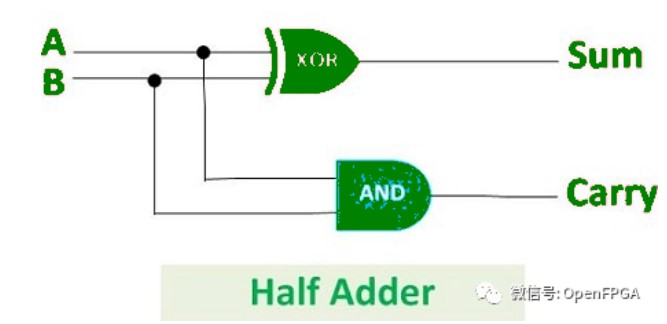

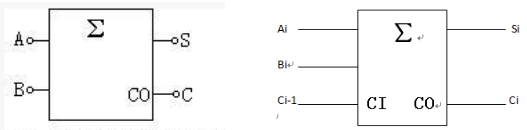

因为半加和 是异或关系,所以半加器也可利用一个集成异或门和与门来实现:

是异或关系,所以半加器也可利用一个集成异或门和与门来实现:

图中右边是半加器的代表符号。

电子发烧友App

电子发烧友App

评论