电平信号与电压信号的区别 不同的电平信号怎么进行“沟通”? 电平信号与电压信号是在电子设备中使用的两个术语,它们描述了不同类型的信号传输方式。电平信号和电压信号都是将信息转换为可传输的形式,但它

2023-10-24 09:58:37 32

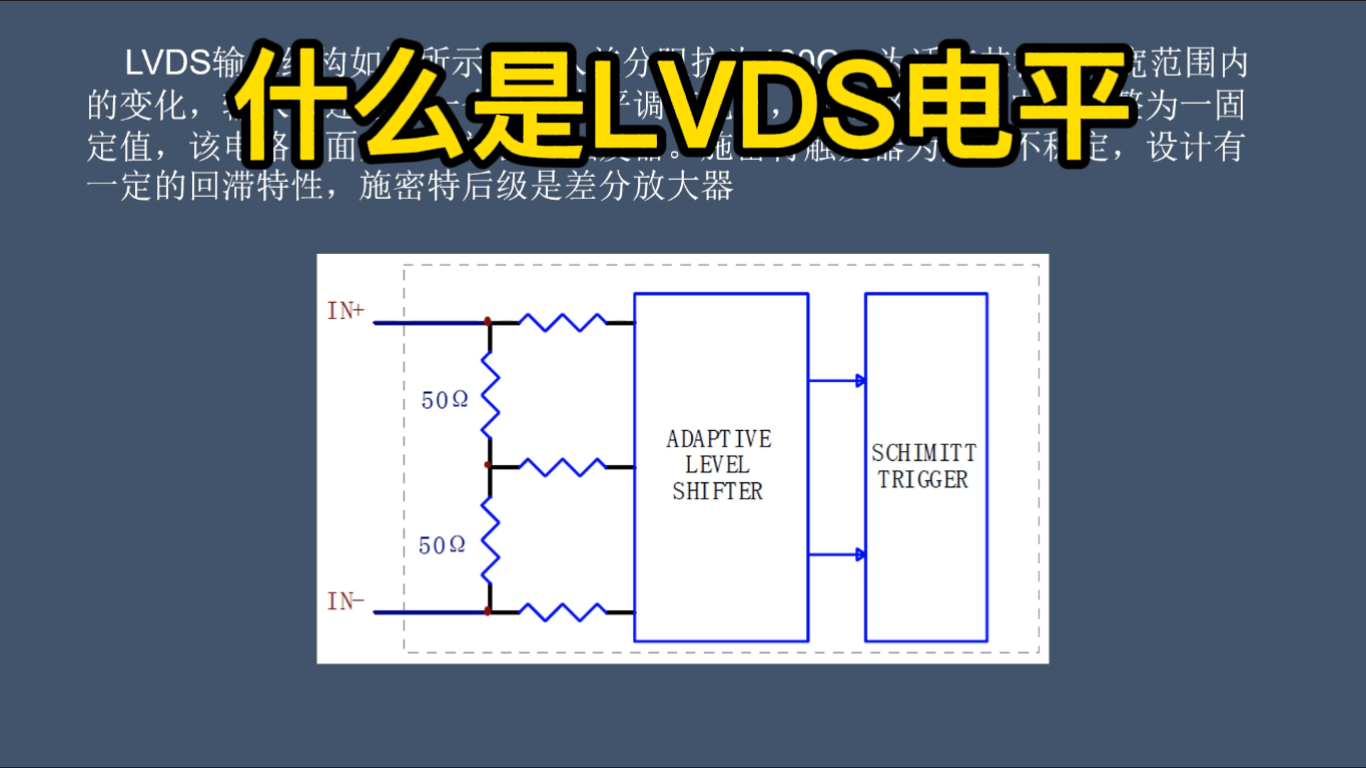

32 请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况? LVDS(Low Voltage Differential Signaling)是差分信号传输威廉希尔官方网站

,能够提供较高的数据传输速率

2023-10-18 16:48:38 107

107 LVDS中的时钟脉冲信号是干什么的? LVDS(Low Voltage Differential Signaling)中的时钟脉冲信号(Clock)是用于同步数据传输的,是整个LVDS接口的重要

2023-10-18 15:38:20 66

66 什么叫做LVDS信号?请问TTL信号与LVDS信号有什么区别? LVDS信号 LVDS(Low Voltage Differential Signaling)又称低压差分信号传输威廉希尔官方网站

,是一种采用差分

2023-10-18 15:38:18 70

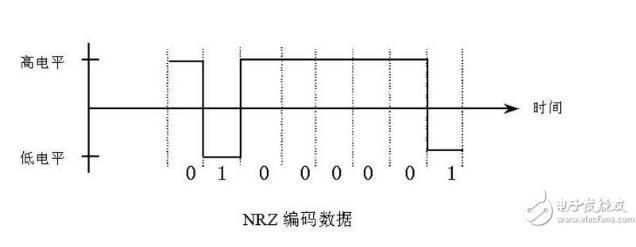

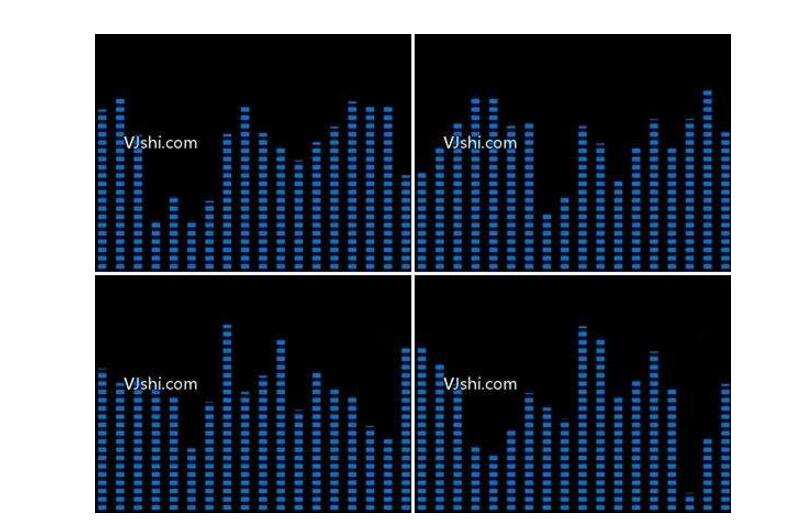

70 、降低功耗和更好的抗干扰能力。 LVDS即低压差分信号,是一种常见的数字信号传输协议。在LVDS中,数据信号被编码成高电平和低电平之间的电压差分,以提高抗干扰能力和传输速度。LVDS具有较低的传输电压和功耗,能够支持高达4 Gbps的数据传输速度,并且传输距离可以达到

2023-10-18 15:38:16 189

189 LVDS传输的是什么信号?判断LVDS信号正常的方法 一、LVDS传输的是什么信号? LVDS是一种低电压差分信号,有两种电压状态,即高电平和低电平,它类似于RS485协议。LVDS信号作为一种数字信号

2023-10-18 15:38:13 145

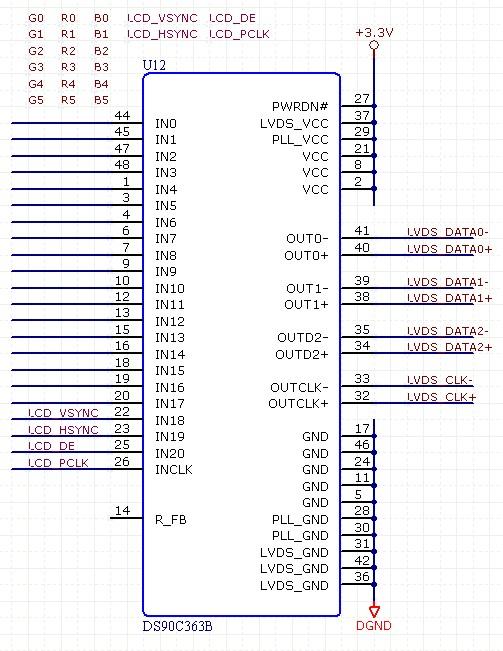

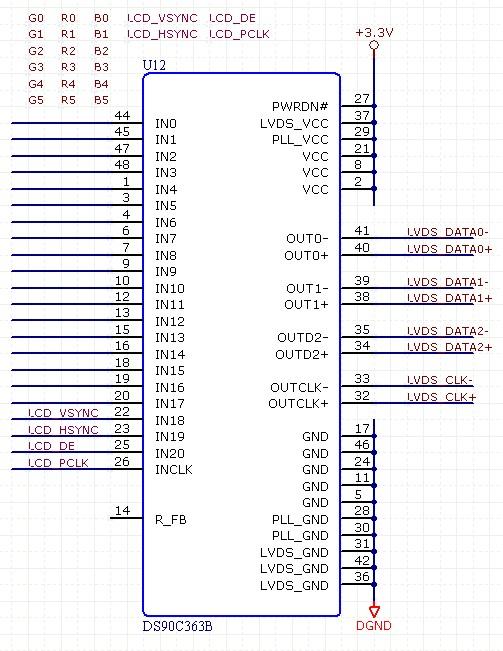

145 LVDS发送芯片的输入信号来自主控芯片,输入信号包含RGB数据信号、时钟信号和控制信号三大类。

2023-10-17 17:28:13 93

93

电子发烧友网站提供《使用Pericom交换机连接LVDS信号.pdf》资料免费下载

2023-07-26 09:17:24 0

0 LVDS :低电压差分信号(Low-Voltage Differential Signaling)是美国国家半导体(National Semiconductor, NS)于1994年提出的一种信号传输模式的电平标准

2023-06-25 15:02:45 1609

1609

单通道M-LVDS接收机的特性与应用 SN65MLVD2 与 SN65MLVD3 均为单通道 M-LVDS 接收机。这些器件完全符合 TIA/EIA-899 (M-LVDS

2009-10-28 14:38:59

今天听了下公司analog designer的介绍课程,有一些LVDS在信号上的观点非常亮,我做了点笔记,跟大家分享一下。

2023-05-25 11:28:20 865

865

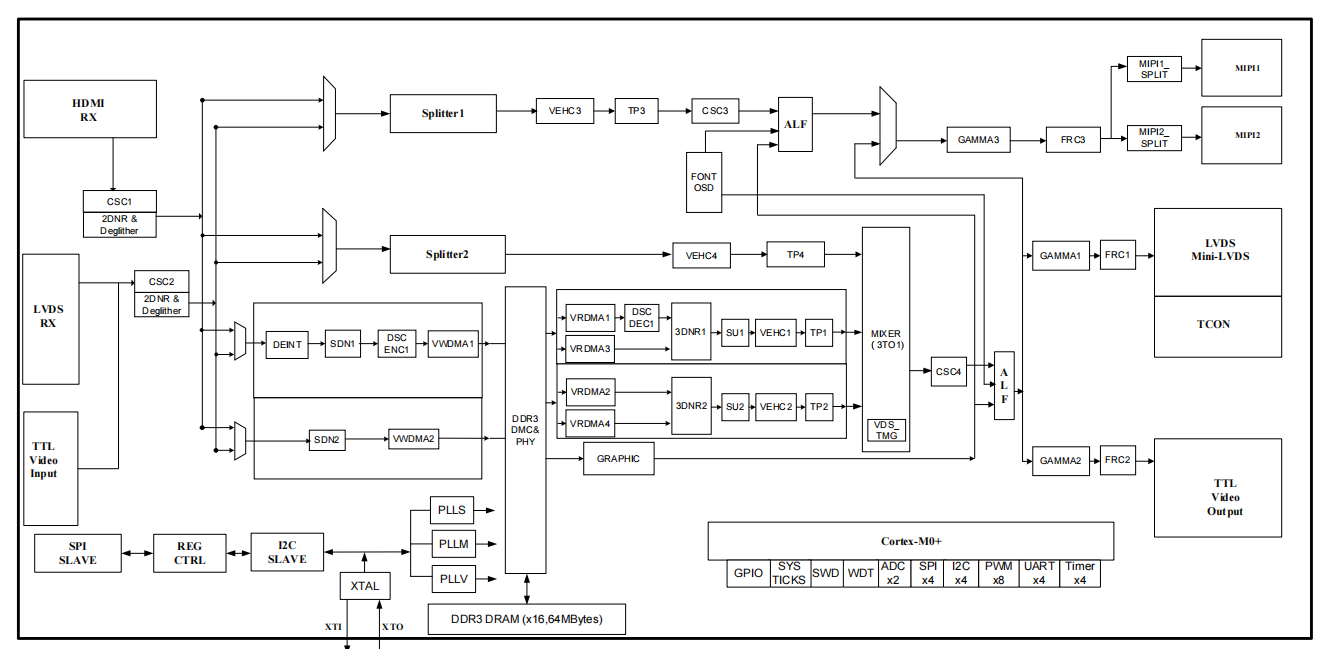

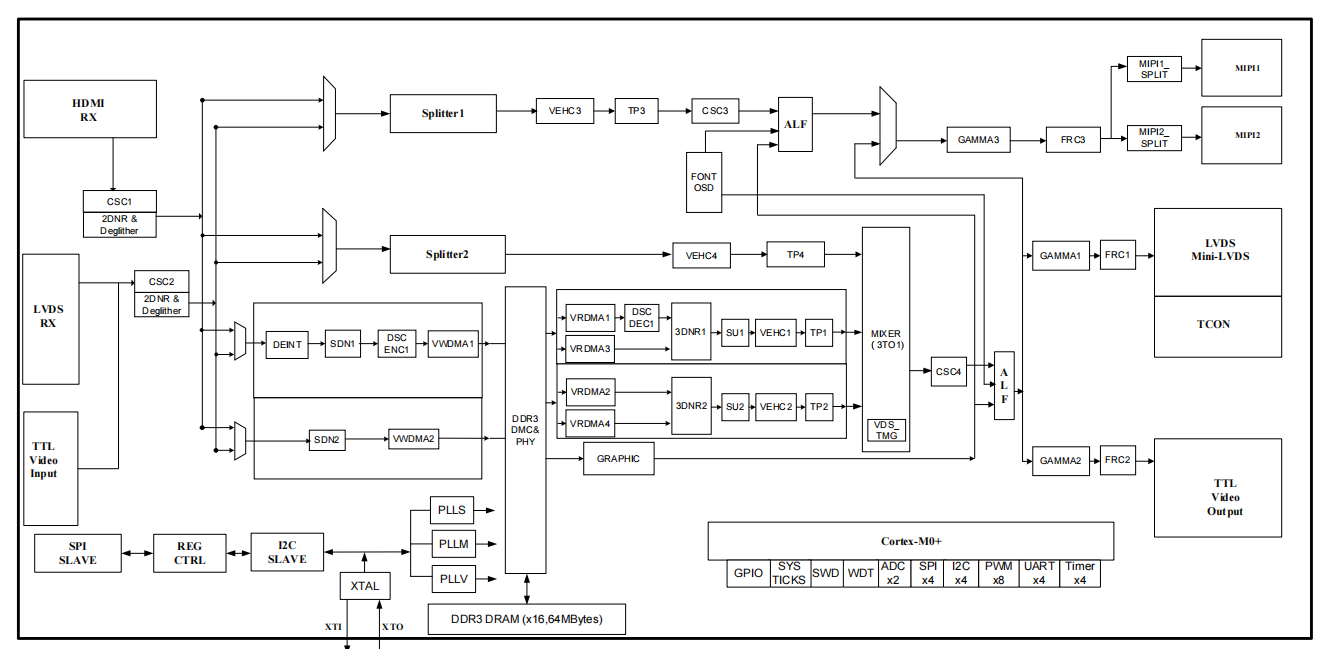

MS1861单颗芯片集成了HDMI、LVDS和数字视频信号输入;输出端可以驱动MIPI(DSI-2)、

LVDS、Mini-LVDS 以及 TTL 类型 TFT-LCD 液晶显示。可支持对输入

2023-05-24 18:52:42 324

324

本应用笔记讨论了EIA/TIA-644低压差分信号(LVDS)标准在3G移动通信中的应用。LVDS具有低功耗和低辐射特性,非常适合WCDMA、EDGE和cdma2000®基站中的高速时钟和信号分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中继器和MAX9152交叉点开关。

2023-03-29 11:14:33 508

508

ANSI EIA/TIA-644 低压差分信号 (LVDS) 标准比更传统的 ECL、PECL 和 CML 标准提供更低的功率和更低的噪声发射,用于高速信号分配。本应用笔记比较了这些通信标准的一些特性,并讨论了LVDS标准的一些优点。

2023-03-29 11:05:07 398

398

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

2023-03-28 11:46:23 1725

1725 LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出

2023-03-08 15:40:00 1912

1912

电平信号检测通常可以采用比较器或者门电路实现。以下是两种常见的方法:比较器是一种有两个输入端口和一个输出端口的电路。当两个输入端口之间的电压差超过比较器的阈值电压时,输出端口会产生一个高电平或低电平

2023-02-27 16:59:33 2750

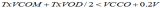

2750 很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2023-02-09 09:48:03 1149

1149 由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平匹配将是电路设计中必须考虑的问题。

2022-11-10 10:01:54 5794

5794 QFN64 封装。该封装符合 RoHS 标准,额定工作温度范围为 -40°C 至 +85°C。 特性: 支持 3 位最大 10dB 输入均衡 支持 LVDS 输出信号重驱输入和输出 每条数据通道 80Mb/s

2022-09-29 14:27:31 642

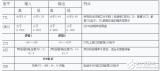

642 当两个banks的I/O口作为LVDS电平时,HR banks的I/O电压VCCO只能为2.5V,HP banks的I/O口电压为1.8V。两个banks支持LVDS的标准不同,HR I/O banks的I/O只能分配LVDS_25标准,HP分配为LVDS标准。

2022-06-24 11:28:04 5095

5095 GM8827C实现以7:1的压缩比将27位CMOS/TTL信号(RGB 8位和HSYNC、VSYNC、 DE)换成串行 LVDS 输出数据流。输入时钟经内部锁相后,同频率输出,同时转换为 LVDS

2021-11-30 21:06:05 7

7 很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2021-08-19 10:08:00 7290

7290

LVDS接口设计及电平转换综述

2021-07-31 16:34:38 14

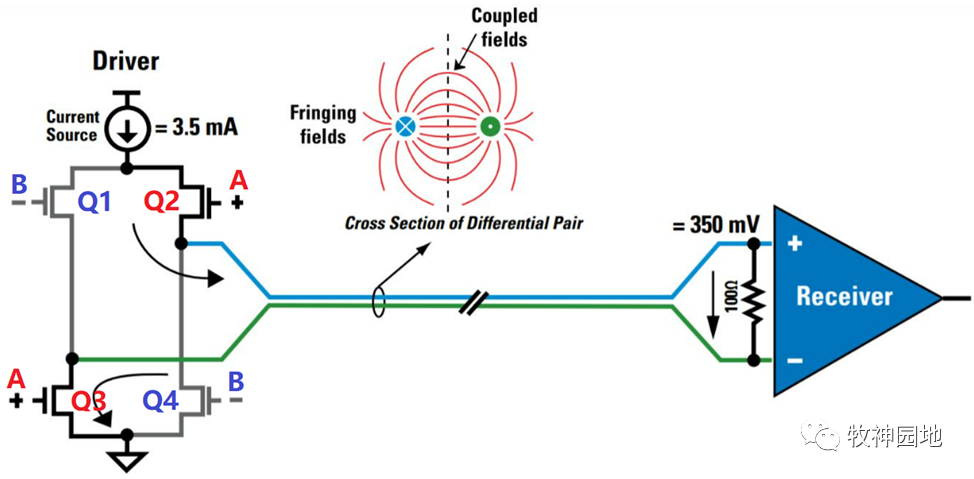

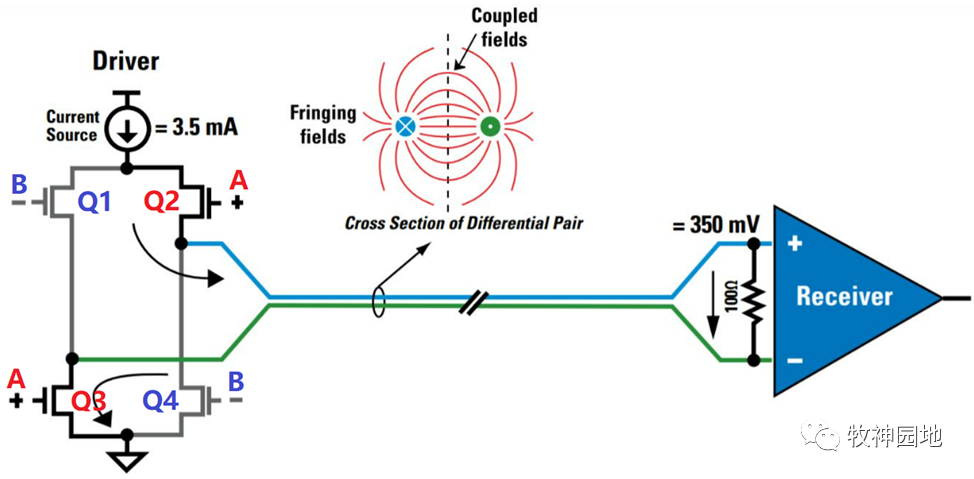

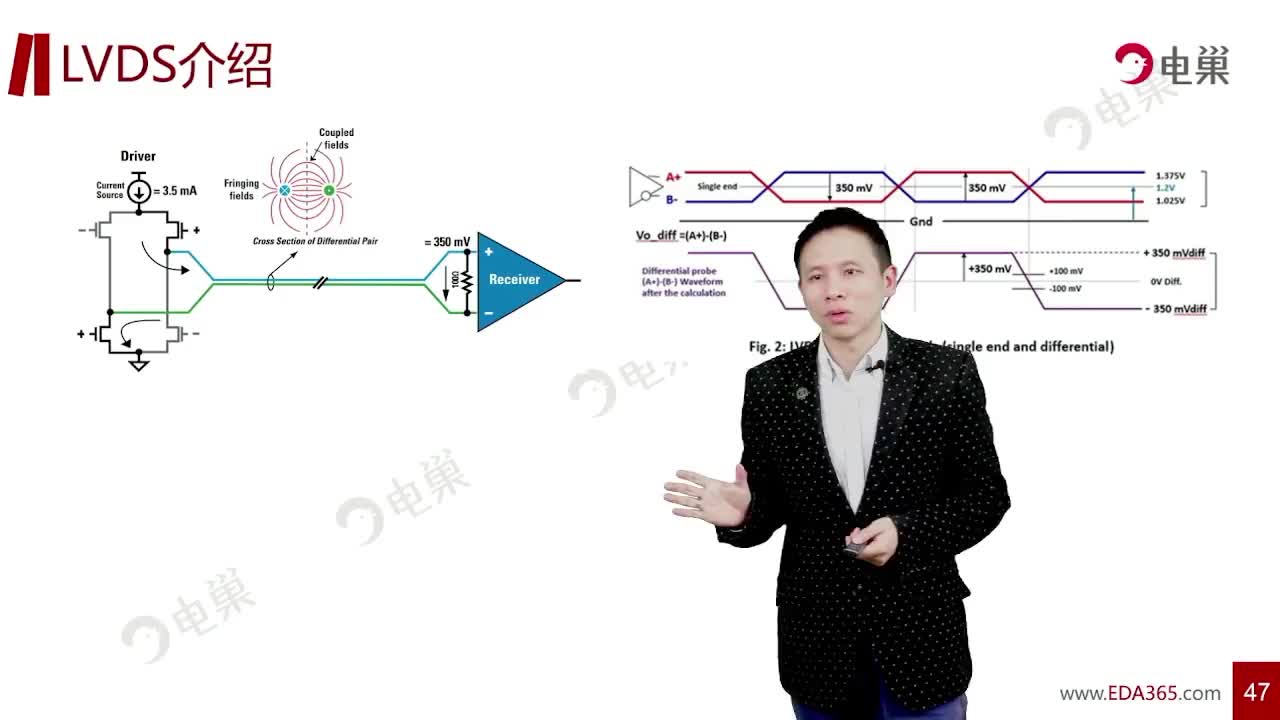

14 。这些良好特性可归因于内部使用的电流控制或驱动器模块的限流功能(最大3 mA)。信号差分电压仅为 20 mV。但是,它随后在接收器侧被放大回 300 mV(差分)的逻辑电平。由此获得的好处包括电磁干扰 (EMI) 极其低、开关速度极其快等。 LVDS接口常常与控制和调节系

2021-05-24 14:05:26 2127

2127

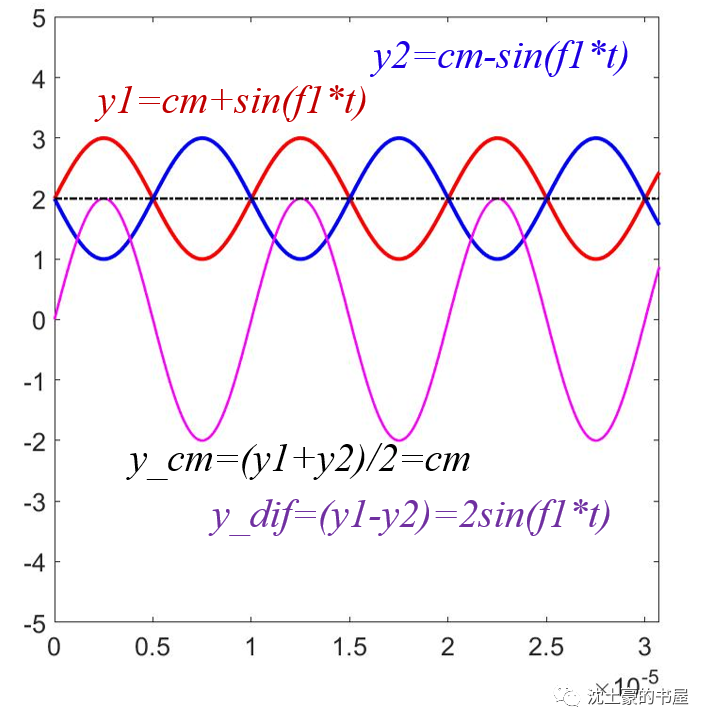

低电压差分信号(LVDS)是一种高速点到点应用通信标准。多点LVDS( M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补电信号之间的电压差检测数据。这样能够极大地改善噪声抗扰度,并将噪声辐射降至最低。

2021-05-24 11:46:54 18

18 电子发烧友网为你提供详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-09 08:45:44 86

86 本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

2021-01-07 16:30:00 36

36 一般情况下,两种不同直流电平的信号(即输出信号的直流电平与输入需求的直流电平相差比较大),比较提倡使用AC耦合,这样输出的直流电平与输入的直流电平独立。

2021-01-07 16:30:00 34

34 信号的逻辑电平经历了从单端信号到差分信号、从低速信号到高速信号的发展过程。最基本的单端信号逻辑电平为CMOS、TTL,在此基础上随着电压摆幅的降低,出现LVCMOS、LVTTL等逻辑电平,随着信号速率的提升又出现ECL、PECL、LVPECL、LVDS、CML等差分信号逻辑电平。

2021-01-05 17:32:38 7

7 本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。 下面详细介绍第二部分:不同逻辑电平之间的互连。 1、LVPECL的互连 1.1、LVPECL到CML的连接 一般情况下

2020-12-20 11:49:31 19167

19167

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。 下面详细介绍第一部

2020-12-20 11:39:59 34000

34000

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2020-10-10 09:25:37 9912

9912

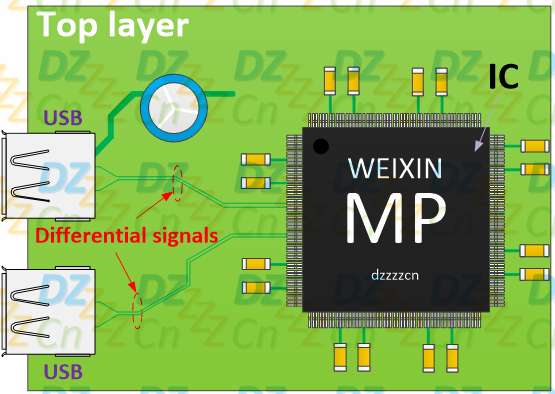

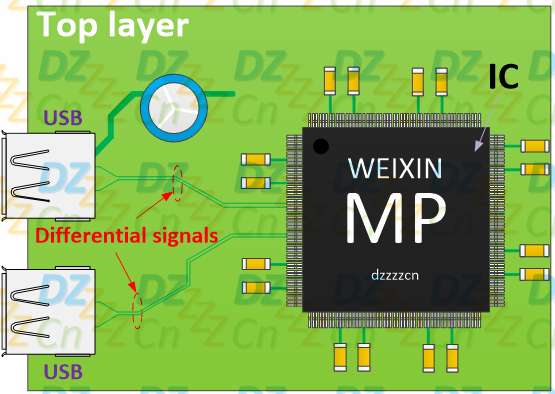

LVDS信号不仅是差分信号,而且还是高速数字信号。因此LVDS传输媒质不管使用的是PCB线还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。

2020-03-08 13:14:00 1636

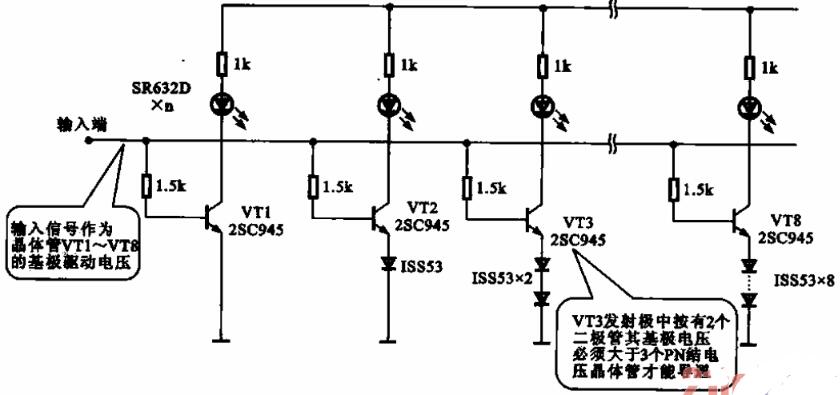

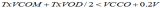

1636 所示是信号电平状态显示电路,例如可作音响的电平显示,多毁发光二极管分别由多组晶体管驱动电路构成,每个驱动晶体管发射极串接的二极管数量不同,驱动晶体管对驱动信号的电平的要求不同。发射极串接的二极管越多

2020-01-24 14:47:00 4025

4025

854105是一种低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),854105提供了一种低功耗、低噪声的解决方案,用于将时钟信号分布在100Ω的受控阻抗上。854105接受LVCMOS/LVTTL输入电平,并将其转换为LVDS输出电平。

2019-07-22 08:00:00 3

3 本文开始介绍了电平的定义与传输电平的分类,其次阐述了电平信号的相关概念,最后介绍了电平信号的产生。

2018-03-13 15:51:05 14891

14891

本文开始阐述了电平信号什么意思以及电平信号的产生,其次对TTL电平的相关定义进行了介绍,最后阐述了电平信号和脉冲信号区别以及阐述了电平和电压的区别。

2018-03-13 10:02:07 65897

65897

本文主要介绍了USB转TTL、USB转232的区别以及各电平信号的特性分析。USB转TTL芯片的单片机通信,直接用USB线连接即可。USB转RS-232模块,该模块核心是在DB9的一端有一块CH340或CH341电平转换芯片,把RS-232电平转换为USB电平。并且PC端还要安装相应的驱动程序。

2018-01-05 14:55:29 33891

33891

本文以脉冲信号和电平信号中心,主要介绍了脉冲信号的原理以及威廉希尔官方网站

标准,其次再具体的阐述了电平信号的概要。最后详细的介绍了电平信号和脉冲信号的产生与它们两者之间的区别。

2017-12-26 15:18:04 72370

72370 本文详细介绍了多点LVDS特性及TI接口的选择指南等相关知识。

2017-11-18 10:18:07 10

10 它差分信号标准类似,LVDS由于消除了磁场,因而比单端信号辐射的噪声要低得多。同时外来噪声作为共模信号耦合到两根线上(即两根线上的噪声电平相同),因此它的抗噪声能力比单端信号要强得多。另外,LVDS驱动器的输出采用电流驱动方式(图1),与其它差分信号标准中的电压

2017-04-06 16:11:31 6

6 ECL电平、LVDS电平、TTL电平三者的简单比较,在应用方面酌情选取

2016-08-29 16:05:01 69

69 什么是LVDS?

现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢?

LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型威廉希尔官方网站

。

2016-06-17 15:42:45 16

16 低电压差分信号(LVDS)是一种高速点到点应用通信标准。多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补

2013-08-22 16:09:00 92

92 LVDS,即Low Voltage Differential Signaling,是一种低压差分信号威廉希尔官方网站

接口。它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研

2012-07-19 16:01:53 5074

5074

文中以基于FPGA设计的高速信号下载器为例,从LVDS的PCB设计,约束设置和信号完整性仿真等多方面研究LVDS信号的实现。

2012-04-20 10:37:02 51

51 随着数字电路数据量的提高,数据的传输速率也越来越快,LVDS(低压差分信号)标准越来越多的应用在FPGA和ASIC器 件中。文章对LVDS信号的特点进行了分析,说明了PCB设计中差分走线的注意事项并结合实际应用设计了一块LVDS接口板。 关键词: LVDS; PCB设计;接口;阻抗

2011-02-23 09:54:03 339

339 基于低电压差分信号(LVDS)的高速信号传输

2010-12-17 17:21:46 38

38 MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器

概述

The MAX9376 is a fully differential

2009-12-19 12:11:39 1492

1492

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1602

1602

lvds是什么意思?

摘要:与ECL、PECL和CML标准相比,ANSI EIA/TAI-644的低电压差分信号(LVDS)标准具有低功耗、低噪声辐射等优势。本文主要讨论LVDS的特性及

2009-05-01 11:13:29 9857

9857

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 1198

1198

摘要:与ECL、PECL和CML标准相比,ANSI EIA/TAI-644的低电压差分信号(LVDS)标准具有低功耗、低噪声辐射等优势。本文主要讨论LVDS的特性及其可能的应用。 最近几年,随着微

2009-04-24 16:04:30 862

862

LVDS与RS422/RS485的应用设计比较

公司产品中,有些时钟传输使用LVDS电平,有些使用了RS422电平。其实,RS422电平也是差分形式,其电

2008-10-16 13:58:57 10752

10752 LVDS信号的PCB设计

1 LVDS信号的工作原理和特点 对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成

2008-10-16 13:57:52 3248

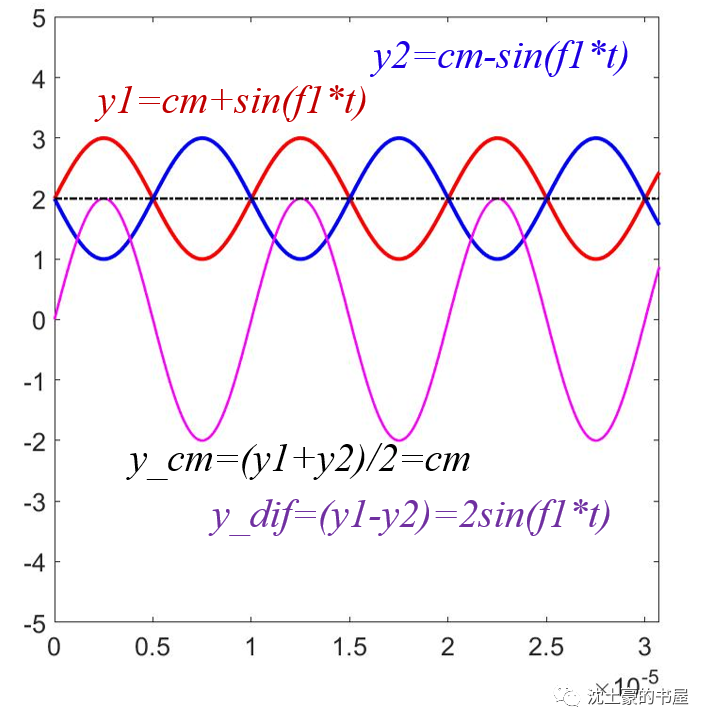

3248 LVDS差分信号抗噪特性

从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:

2008-10-16 13:53:16 1404

1404 什么是lvds信号

LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号

2008-10-16 13:49:11 7293

7293 1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号威廉希尔官方网站

,它使得信号能在差

2008-10-16 13:44:45 152

152 84:GTL信号的时序 31

83:GTL信号的测试 30

82:GTL信号的PCB设计 30

81:GTL器件的特点和电平 29

8、GTL器件的原理和特点29

77:LVDS器件应用举例 28

76:LVDS

2008-06-24 10:04:11 358

358 什么是LVDS?现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢?LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应

2007-09-26 11:45:09 4838

4838

电子发烧友App

电子发烧友App

评论